# RZ/T2, RZ/N2

# Quick Start Guide: Firmware Update

## Introduction

This document describes the procedure for updating user application programs via Ethernet by using the RZ/T2, RZ/N2 firmware update sample programs.

## **Target Device**

RZ/T2M Group

RZ/T2L Group

RZ/N2L Group

RZ/T2H Group

RZ/N2H Group

## **Contents**

| 1.    | Overview                                          | 4  |

|-------|---------------------------------------------------|----|

| 1.1   | Introduction                                      | 4  |

| 1.2   | Features                                          | 4  |

| 1.3   | Limitations                                       | 4  |

| 1.4   | Package Contents                                  | 4  |

| 1.5   | Related Documents                                 | 8  |

| 1.6   | Explanation of Terms                              | 8  |

| 2.    | Firmware Update Mechanism                         | 9  |

| 2.1   | Operating Modes                                   | 9  |

| 2.2   | Sample Program Configuration                      | 10 |

| 2.3   | Using External Flash Memory                       | 10 |

| 3.    | Configuring the Firmware Update System            | 13 |

| 3.1   | Configuring the Firmware Update System for RZ/T2M | 13 |

| 3.1.  | 1 Concatenate Program and Parameter               | 13 |

| 3.1.2 | 2 Program to Flash                                | 14 |

| 3.2   | Configuring the Firmware Update System for RZ/T2L | 16 |

| 3.2.  | .1 Concatenate Program and Parameter              | 16 |

| 3.2.2 | 2 Program to Flash                                | 16 |

| 3.3   | Configuring the Firmware Update System for RZ/N2L | 19 |

| 3.3.  | .1 Concatenate Program and Parameter              | 19 |

| 3.3.2 | 2 Program to Flash                                | 19 |

| 3.4   | Configuring the Firmware Update System for RZ/T2H | 22 |

| 3.4.  | 1 Concatenate Program and Parameter               | 23 |

| 3.4.2       | Program to Flash                                          | 23 |

|-------------|-----------------------------------------------------------|----|

| 3.5         | Configuring the Firmware Update System for RZ/N2H         | 25 |

| 3.5.1       | Concatenate Program and Parameter                         | 26 |

| 3.5.2       | Program to Flash                                          | 26 |

| 3.6         | Update Program Configuration                              | 28 |

| 3.7         | SSBL Configuration                                        | 28 |

| 3.7.1       | Concatenate SSBL and Parameter for RZ/T2M                 | 30 |

| 3.7.2       | Concatenate SSBL and Parameter for RZ/T2L                 | 30 |

| 3.7.3       | Concatenate SSBL and Parameter for RZ/N2L                 | 30 |

| 3.7.4       | Concatenate SSBL and Parameter for RZ/T2H Cortex®-R52     | 31 |

| 3.7.5       | Concatenate SSBL and Parameter for RZ/T2H Cortex®-A55     | 31 |

| 3.7.6       | Concatenate SSBL and Parameter for RZ/N2H Cortex®-R52     | 31 |

| 3.7.7       | Concatenate SSBL and Parameter for RZ/N2H Cortex®-A55     | 31 |

| 3.8         | User Application Program Configuration                    | 31 |

| 3.8.1       | Generate Parameter for Application for RZ/T2M             | 43 |

| 3.8.2       | Generate Parameter for Application for RZ/T2L             | 43 |

| 3.8.3       | Generate Parameter for Application for RZ/N2L             | 43 |

| 3.8.4       | Generate Parameter for Application for RZ/T2H Cortex®-R52 | 43 |

| 3.8.5       | Generate Parameter for Application for RZ/T2H Cortex®-A55 | 44 |

| 3.8.6       | Generate Parameter for Application for RZ/N2H Cortex®-R52 | 44 |

| 3.8.7       | Generate Parameter for Application for RZ/N2H Cortex®-A55 | 44 |

| 4. <i>i</i> | Applying Firmware Updates                                 | 45 |

| 4.1         | Host PC Setup                                             |    |

| 4.1.1       | Tool Setup                                                |    |

| 4.1.2       | Network Adapter Settings                                  |    |

| 4.2         | Update Procedure                                          |    |

|             | Update Procedure for RZ/T2M                               |    |

|             | 1 Creating Update File                                    |    |

|             | 2 Applying Update                                         |    |

|             | Update Procedure for RZ/T2L                               |    |

|             | 1 Creating Update File                                    |    |

|             | 2 Applying Update                                         |    |

|             | Update Procedure for RZ/N2L                               |    |

|             | 1 Creating Update File                                    |    |

|             | 2 Applying Update                                         |    |

|             | Update Procedure for RZ/T2H                               |    |

|             | 1 Creating Update File                                    |    |

|             | 2 Applying Update                                         |    |

|             | Update Procedure for RZ/N2H                               |    |

|             | 1 Creating Update File                                    |    |

| 4.2.5. | .2 Applying Update                               | 57 |

|--------|--------------------------------------------------|----|

| 5.     | Sample Program                                   | 59 |

| 5.1    | Update File Format                               | 59 |

| 5.2    | Communication Protocols of Update Program        | 61 |

| 5.2.1  | START_UPDATE                                     | 62 |

| 5.2.2  | FIRMWARE_DATA                                    | 62 |

| 5.2.3  | ACK                                              | 62 |

| 5.2.4  | NACK                                             | 62 |

| 5.3    | Implementation Specifications of Update Program  | 64 |

| 5.3.1  | Development Environment                          | 64 |

| 5.3.2  | File Structure                                   | 64 |

| 5.3.3  | Functions                                        | 65 |

| 5.3.4  | Flowchart of Update Program Processing           | 66 |

| 5.3.5  | Memory Maps for RSK+                             | 67 |

| 5.3.6  | Memory Maps for EVB                              | 69 |

| 5.3.7  | How to Use NOR Flash in the RZ/N2L Project       | 72 |

| 5.4    | Specifications of Tools Used with Sample Program | 73 |

| 5.4.1  | fwupdate_utility.py                              | 73 |

| 5.4.2  | fwupdate.py                                      | 75 |

| Revis  | sion History                                     | 76 |

### 1. Overview

#### 1.1 Introduction

This document describes the functions provided by the RZ/T2, RZ/N2 firmware update sample programs and explains how to use the various tools.

This sample program package uses the Flexible Software Package for RZ/T2M, RZ/T2L, RZ/T2H, RZ/N2L and RZ/N2H. For more information about FSP, please refer to RZ/T2, RZ/N2 Getting Started with Flexible Software Package.

The sample program can update user application programs in the external flash memory on the boards, and the outline of the sample program is as follows. For details, please refer to Chapters 2, 3 and 4.

- Upon system reset, a loader program called the Secondary Stage Boot Loader (SSBL) is initiated from external flash.

- Based on the setting of a DIP switch, the SSBL will either load and start the user application, or an update program.

- The update program receives a binary via ethernet and replaces the user application in the external flash.

- Preparation of the binary for the update and transfer to the board is done via Python script on the PC.

- The initial flashing of the firmware (SSBL, update program and user application) is handled by scripts and sample program included in the package from the RZ/T2, RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*) Application Note.

#### 1.2 Features

The sample program has the following features:

- It is possible to update via Ethernet user application programs written to the QSPI flash, OSPI flash and NOR flash memory on Renesas Starter Kit+ for RZ/T2M, RZ/T2L and RZ/N2L.

- It is possible to update via Ethernet user application programs written to the QSPI flash, OSPI flash memory on Evaluation Board for RZ/T2H and RZ/N2H.

- If the update of a user application program fails, the user can redo the update as many times as necessary until the update is successful.

- RZ/T2M, RZ/T2H Cortex®-R52 and RZ/N2H Cortex®-R52 can update applications that use dual cores.

- RZ/T2H Cortex®-A55 and RZ/N2H Cortex®-A55 can update applications that use multi cores.

### 1.3 Limitations

The sample program has the following limitations:

• It is not possible to update a user application program while a user application program is running.

## 1.4 Package Contents

RZ/T2, RZ/N2 firmware update sample program package contains several files with software and tools. The following table lists their contents.

**Table 1.1 Firmware Update Sample Program Common Package Contents**

| No. | File Path                               | Classification | Remarks                                                       |

|-----|-----------------------------------------|----------------|---------------------------------------------------------------|

| 1   | fwupdate_utility.py                     | Tool           | Update file generator tool                                    |

| 2   | fwupdate.py                             | Tool           | Update files send tool                                        |

| 3   | r01an6472ej0310-rzt2-n2-fwupdate.pdf    | Document       | This document RZ/T2, RZ/N2 Quick Start Guide: Firmware Update |

| 4   | r01an6641ej0310-rzt2-n2-releasenote.pdf | Document       | Release Note                                                  |

Table 1.2 Firmware Update Sample Program Common Package Contents for RZ/T2M

| No. | File Path                     | Classification  | Remarks                               |

|-----|-------------------------------|-----------------|---------------------------------------|

| 1   | RZT2M_RSK_FWUpdate_Rev300.zip | Software        | Sample program code for RZ/T2M  Note1 |

| 2   | RZT2M_RSK_FWUpdate.bin        | Software        | Programs and data for RZ/T2M          |

| 3   | RZT2M_RSK_SSBL.bin            | Software        | stored in the "Pre-built parameters   |

| 4   | RZT2M_RSK_SSBL_xspi0.bin      | Software & data | and programs" folder. Note2           |

| 5   | parameter_RZT2M_bsp_LED_0.bin | Data            | (The application's bin file was       |

| 6   | parameter_RZT2M_bsp_LED_1.bin | Data            | generated by the IAR Compiler         |

| 7   | initial_image_RZT2M_xspi0.bin | Data            | project)                              |

| 8   | RZT2M_bsp_LED_0.bin           | Software        |                                       |

| 9   | RZT2M_bsp_LED_1.bin           | Software        |                                       |

| 10  | RZT2M_bsp_LED_x.zip           | Software        |                                       |

| 11  | RZT2M_bsp_LED_x_CPU1.zip      | Software        |                                       |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.3 Firmware Update Sample Program Common Package Contents for RZ/T2L

| No. | File Path                     | Classification  | Remarks                               |

|-----|-------------------------------|-----------------|---------------------------------------|

| 1   | RZT2L_RSK_FWUpdate_Rev300.zip | Software        | Sample program code for RZ/T2L  Note1 |

| 2   | RZT2L_RSK_FWUpdate.bin        | Software        | Programs and data for RZ/T2L          |

| 3   | RZT2L_RSK_SSBL.bin            | Software        | stored in the "Pre-built parameters   |

| 4   | RZT2L_RSK_SSBL_xspi0.bin      | Software & data | and programs" folder. Note2           |

| 5   | parameter_RZT2L_bsp_LED_1.bin | Data            | (The application's bin file was       |

| 6   | parameter_RZT2L_bsp_LED_3.bin | Data            | generated by the IAR Compiler         |

| 7   | initial_image_RZT2L_xspi0.bin | Data            | project)                              |

| 8   | RZT2L_bsp_LED_1.bin           | Software        |                                       |

| 9   | RZT2L_bsp_LED_3.bin           | Software        |                                       |

| 10  | RZT2L_bsp_LED_x.zip           | Software        |                                       |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.4 Firmware Update Sample Program Common Package Contents for RZ/N2L

| No. | File Path                     | Classification  | Remarks                                |

|-----|-------------------------------|-----------------|----------------------------------------|

| 1   | RZN2L_RSK_FWUpdate_Rev310.zip | Software        | Sample program code for RZ/N2L Note1   |

| 2   | RZN2L_RSK_FWUpdate.bin        | Software        | Programs and data for RZ/N2L           |

| 3   | RZN2L_RSK_SSBL.bin            | Software        | stored in the "Pre-built parameters    |

| 4   | RZN2L_RSK_SSBL_xspi0.bin      | Software & data | and programs" folder. Note2            |

| 5   | parameter_RZN2L_bsp_LED_0.bin | Data            | (The application's bin file was        |

| 6   | parameter_RZN2L_bsp_LED_3.bin | Data            | generated by the IAR Compiler project) |

| 7   | initial_image_RZN2L_xspi0.bin | Data            | project)                               |

| 8   | RZN2L_bsp_LED_0.bin           | Software        |                                        |

| 9   | RZN2L_bsp_LED_3.bin           | Software        |                                        |

| 10  | RZN2L_bsp_LED_x.zip           | Software        |                                        |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.5 Firmware Update Sample Program Common Package Contents for RZ/T2H Cortex®-R52

| No. | File Path                     | Classification  | Remarks                                          |

|-----|-------------------------------|-----------------|--------------------------------------------------|

| 1   | RZT2H_EVB_FWUpdate_Rev300.zip | Software        | Sample program code for RZ/T2H Cortex®-R52 Note1 |

| 2   | RZT2H_EVB_FWUpdate.bin        | Software        | Programs and data for RZ/T2H                     |

| 3   | RZT2H_EVB_SSBL.bin            | Software        | Cortex®-R52 stored in the "Pre-built             |

| 4   | RZT2H_EVB_SSBL_xspi0.bin      | Software & data | parameters and programs/cr52"                    |

| 5   | parameter_RZT2H_bsp_LED_0.bin | Data            | folder. Note2                                    |

| 6   | parameter_RZT2H_bsp_LED_1.bin | Data            | (The application's bin file was                  |

| 7   | initial_image_RZT2H_xspi0.bin | Data            | generated by the IAR Compiler project)           |

| 8   | RZT2H_bsp_LED_0.bin           | Software        | project)                                         |

| 9   | RZT2H_bsp_LED_1.bin           | Software        |                                                  |

| 10  | RZT2H_bsp_LED_x.zip           | Software        |                                                  |

| 11  | RZT2H_bsp_LED_x_CPU1.zip      | Software        |                                                  |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.6 Firmware Update Sample Program Common Package Contents for RZ/T2H Cortex®-A55

| No. | File Path                       | Classification  | Remarks                                |

|-----|---------------------------------|-----------------|----------------------------------------|

| 1   | RZT2H_EVB_CA55_FWUpdate_Rev300. | Software        | Sample program code for RZ/T2H         |

|     | zip                             |                 | Cortex®-A55 Note1                      |

| 2   | RZT2H_EVB_CA55_FWUpdate.bin     | Software        | Programs and data for RZ/T2H           |

| 3   | RZT2H_EVB_CA55_SSBL.bin         | Software        | Cortex®-A55 stored in the "Pre-built   |

| 4   | RZT2H_EVB_SSBL_xspi0.bin        | Software & data | parameters and programs/ca55"          |

| 5   | parameter_RZT2H_bsp_LED_0.bin   | Data            | folder. Note2                          |

| 6   | parameter_RZT2H_bsp_LED_1.bin   | Data            | (The application's bin file was        |

| 7   | initial_image_RZT2H_xspi0.bin   | Data            | generated by the IAR Compiler project) |

| 8   | RZT2H_bsp_LED_0.bin             | Software        | projecty                               |

| 9   | RZT2H_bsp_LED_1.bin             | Software        |                                        |

| 10  | RZT2H_bsp_LED_x_CA55_Core0.zip  | Software        |                                        |

| 11  | RZT2H_bsp_LED_x_CA55_Core1.zip  | Software        |                                        |

| 12  | RZT2H_bsp_LED_x_CA55_Core2.zip  | Software        |                                        |

| 13  | RZT2H_bsp_LED_x_CA55_Core3.zip  | Software        |                                        |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.7 Firmware Update Sample Program Common Package Contents for RZ/N2H Cortex®-R52

| No. | File Path                     | Classification  | Remarks                                |

|-----|-------------------------------|-----------------|----------------------------------------|

| 1   | RZN2H_EVB_FWUpdate_Rev310.zip | Software        | Sample program code for RZ/N2H         |

|     |                               |                 | Cortex®-R52 Note1                      |

| 2   | RZN2H_EVB_FWUpdate.bin        | Software        | Programs and data for RZ/N2H           |

| 3   | RZN2H_EVB_SSBL.bin            | Software        | Cortex®-R52 stored in the "Pre-built   |

| 4   | RZN2H_EVB_SSBL_xspi0.bin      | Software & data | parameters and programs/cr52"          |

| 5   | parameter_RZN2H_bsp_LED_3.bin | Data            | folder. Note2                          |

| 6   | parameter_RZN2H_bsp_LED_4.bin | Data            | (The application's bin file was        |

| 7   | initial_image_RZN2H_xspi0.bin | Data            | generated by the IAR Compiler project) |

| 8   | RZN2H_bsp_LED_3.bin           | Software        | projecty                               |

| 9   | RZN2H_bsp_LED_4.bin           | Software        |                                        |

| 10  | RZN2H_bsp_LED_x.zip           | Software        |                                        |

| 11  | RZN2H_bsp_LED_x_CPU1.zip      | Software        |                                        |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

Table 1.8 Firmware Update Sample Program Common Package Contents for RZ/N2H Cortex®-A55

| No. | File Path                       | Classification  | Remarks                                |

|-----|---------------------------------|-----------------|----------------------------------------|

| 1   | RZN2H_EVB_CA55_FWUpdate_Rev310. | Software        | Sample program code for RZ/N2H         |

|     | zip                             |                 | Cortex®-A55 Note1                      |

| 2   | RZN2H_EVB_CA55_FWUpdate.bin     | Software        | Programs and data for RZ/N2H           |

| 3   | RZN2H_EVB_CA55_SSBL.bin         | Software        | Cortex®-A55 stored in the "Pre-built   |

| 4   | RZN2H_EVB_SSBL_xspi0.bin        | Software & data | parameters and programs/ca55"          |

| 5   | parameter_RZN2H_bsp_LED_3.bin   | Data            | folder. Note2                          |

| 6   | parameter_RZN2H_bsp_LED_4.bin   | Data            | (The application's bin file was        |

| 7   | initial_image_RZN2H_xspi0.bin   | Data            | generated by the IAR Compiler project) |

| 8   | RZN2H_bsp_LED_3.bin             | Software        | project)                               |

| 9   | RZN2H_bsp_LED_4.bin             | Software        |                                        |

| 10  | RZN2H_bsp_LED_x_CA55_Core0.zip  | Software        |                                        |

| 11  | RZN2H_bsp_LED_x_CA55_Core1.zip  | Software        |                                        |

| 12  | RZN2H_bsp_LED_x_CA55_Core2.zip  | Software        |                                        |

| 13  | RZN2H_bsp_LED_x_CA55_Core3.zip  | Software        |                                        |

Note1 Contains sample program projects for GCC and IAR compilers.

Note2 These files are used in Chapters 3 and 4 of this document as a reference for building the environment.

## 1.5 Related Documents

Table 1.9 lists documents related to this document.

**Table 1.9 Related Documents**

| Title                                                          | Document Number |

|----------------------------------------------------------------|-----------------|

| RZ/T2M Group Renesas Starter Kit+ for RZ/T2M User's Manual     | R20UT4939EG**** |

| RZ/T2M Group Renesas Starter Kit+ for RZ/T2M Quick Start Guide | R20UT4941EG**** |

| RZ/T2, RZ/N2 Getting Started with Flexible Software Package    | R01AN6434EJ**** |

| RZ/T2M Group User's Manual: Hardware                           | R01UH0916EJ**** |

| RZ/T2, RZ/N2 Device Setup Guide for Flash boot                 | R01AN6471EJ**** |

| RZ/T2L Group Renesas Starter Kit+ for RZ/T2L User's Manual     | R20UT5164EJ**** |

| RZ/T2L Group Renesas Starter Kit+ for RZ/T2L Quick Start Guide | R20UT5235EJ**** |

| RZ/T2L Group User's Manual: Hardware                           | R01UH0985EJ**** |

| RZ/N2L Group Renesas Starter Kit+ for RZ/N2L User's Manual     | R20UT4984EG**** |

| RZ/N2L Group Renesas Starter Kit+ for RZ/N2L Quick Start Guide | R20UT4986EG**** |

| RZ/N2L Group User's Manual: Hardware                           | R01UH0955EJ**** |

| RZ/T2H and RZ/N2H Groups User's Manual: Hardware               | R01UH1039EJ**** |

| RZ/T2H Group RZ/T2H Evaluation Board User's Manual             | R20UT5405EJ**** |

| RZ/N2H Group RZ/N2H Evaluation Board User's Manual             | R20UT5522EJ**** |

## 1.6 Explanation of Terms

The meanings of terms used in this document are indicated below.

| Term Used in This Document | Meaning of Term                                                        |

|----------------------------|------------------------------------------------------------------------|

| Update program             | The program, contained in the sample program package, used to          |

|                            | update user application programs.                                      |

| User application program   | Program that can be updated with this sample program package.          |

| Update file                | The program to be updated.                                             |

| Firmware update system     | The file containing the program to be updated.                         |

| SSBL                       | Second stage boot loader, referred to as a loader program in following |

|                            | documents:                                                             |

|                            | RZ/T2M Group Renesas Starter Kit+ for RZ/T2M User's Manual             |

|                            | RZ/T2L Group Renesas Starter Kit+ for RZ/T2L User's Manual             |

|                            | RZ/N2L Group Renesas Starter Kit+ for RZ/N2L User's Manual             |

|                            | RZ/T2H Group RZ/T2H Evaluation Board User's Manual                     |

|                            | RZ/N2H Group RZ/N2H Evaluation Board User's Manual                     |

| Loader program             | SSBL, Second stage boot loader                                         |

## 2. Firmware Update Mechanism

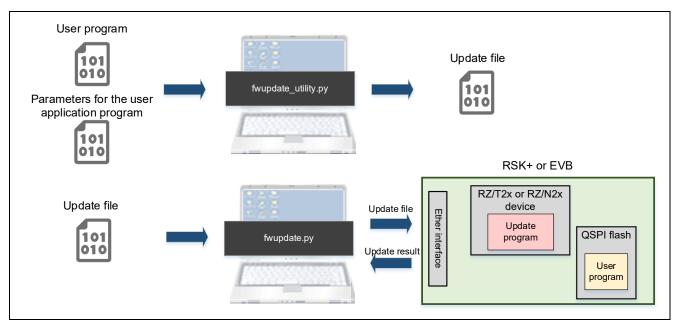

The sample program can update user application programs written to the external flash memory on the boards. Figure 2.1 illustrates the system structure of the sample program.

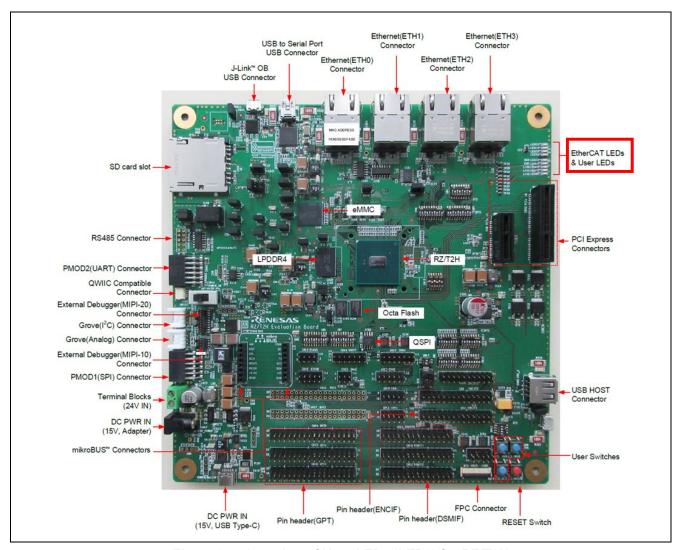

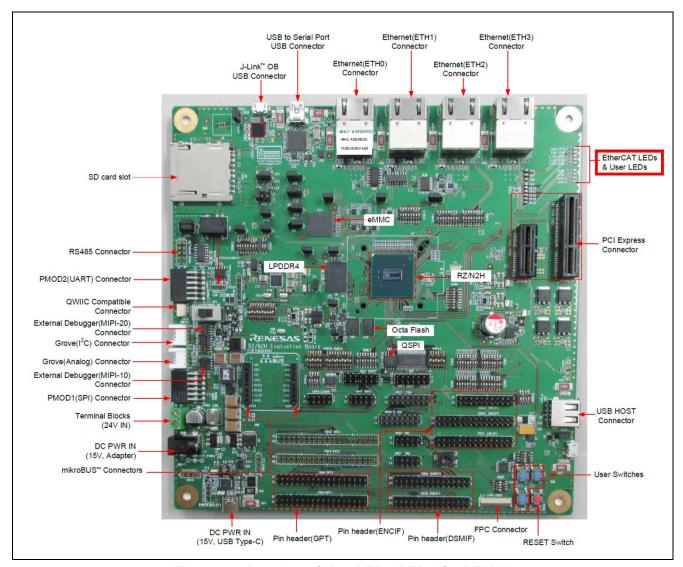

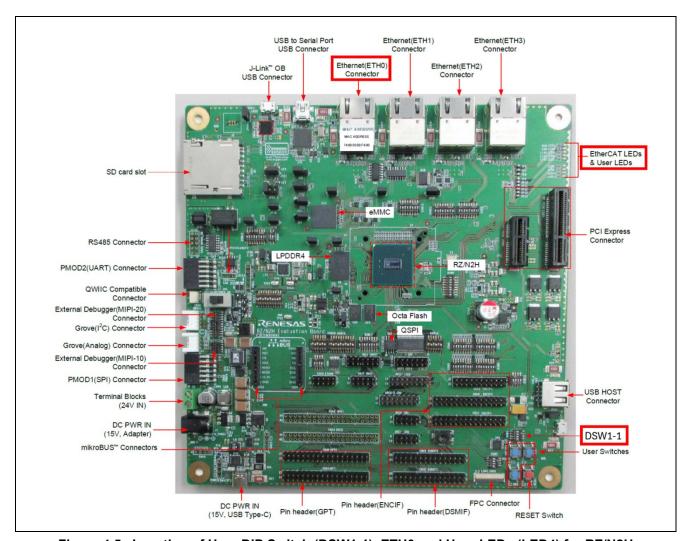

The target devices are RZ/T2M, RZ/T2L, RZ/T2H, RZ/N2L or RZ/N2H. The target boards are the Renesas Starter Kit+ (hereinafter referred to as RSK+) for RZ/T2M, RZ/T2L, RZ/N2L or Evaluation Board for RZ/T2H, RZ/N2H (hereinafter referred to as EVB).

Figure 2.1 System Structure of Firmware Update Sample Program

The sample program updates user application programs through the following sequence of steps:

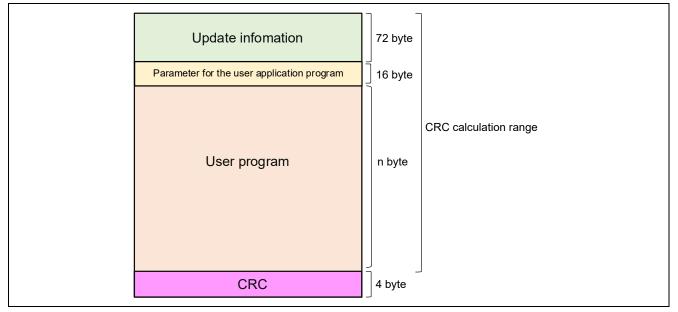

- Using fwupdate\_utility.py, the user creates an update file containing the user application program to be applied as an update and information on its location in the external flash memory. Refer to 5.4.1 for details of fwupdate\_utility.py and to 5.1 for details of the update file.

- 2. The user starts the device in update mode.

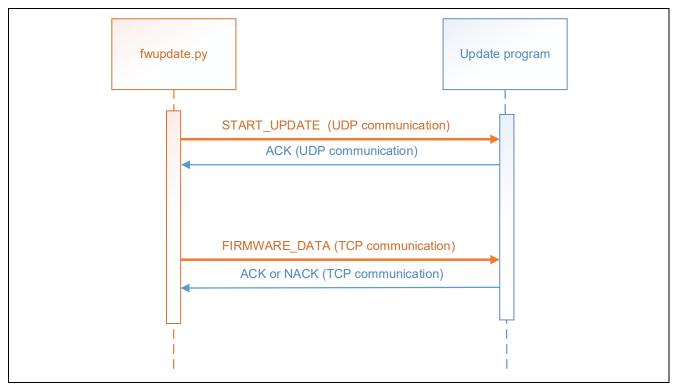

- 3. Using fwupdate.py, the user sends the update file from the host PC to the device via an Ethernet connection. Refer to 5.2 for the communication protocols used between the host PC and the board and the packet format of the communication protocols.

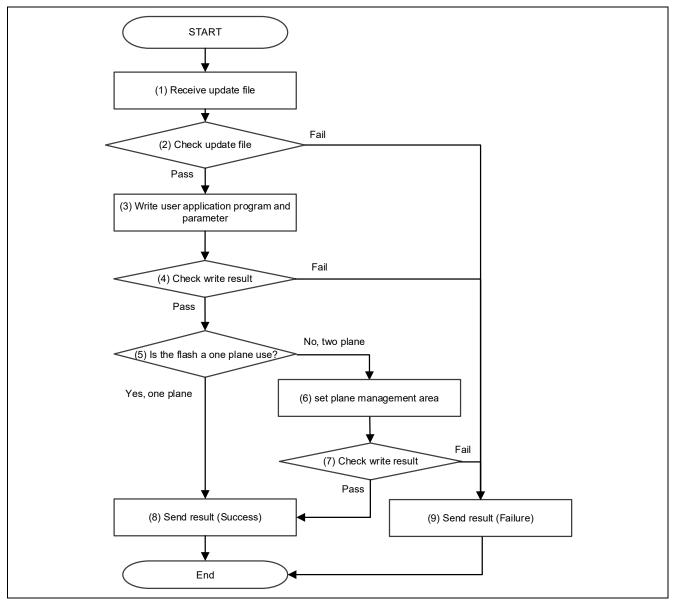

- 4. When the update file is received by the device, the update program on the device extracts the user application program and writes it to the external flash memory. Refer to 5.3 for details of the update program.

## 2.1 Operating Modes

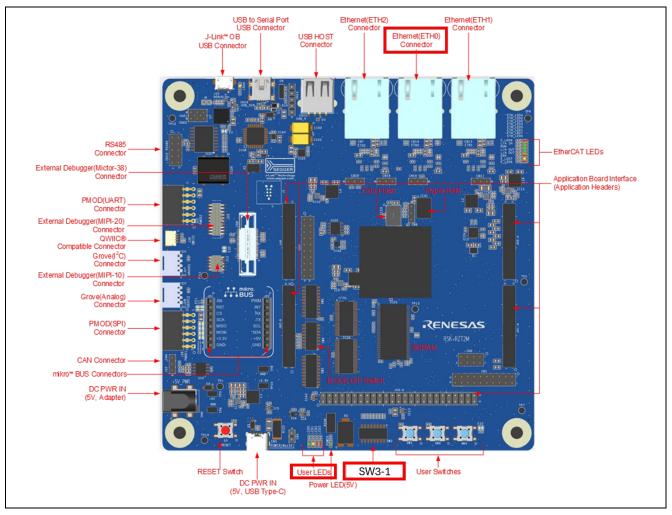

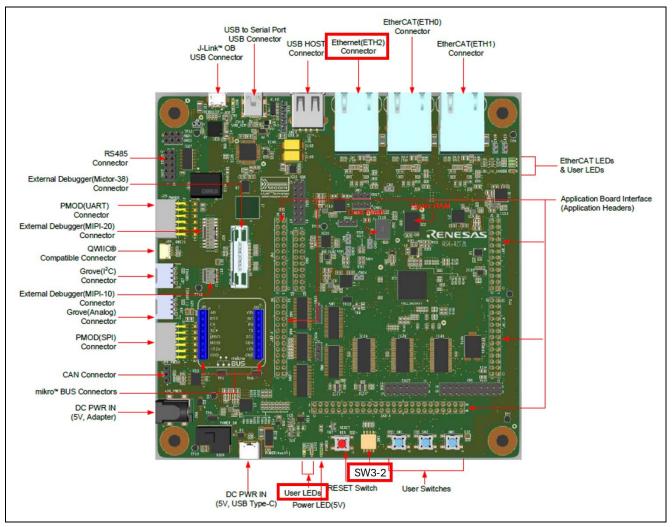

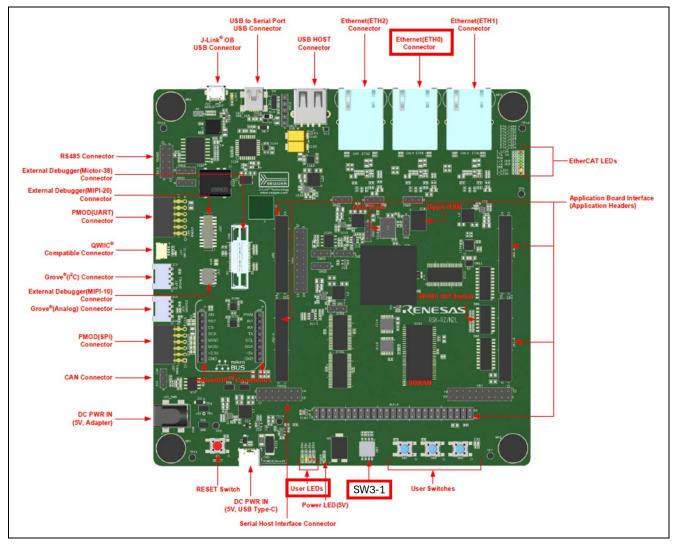

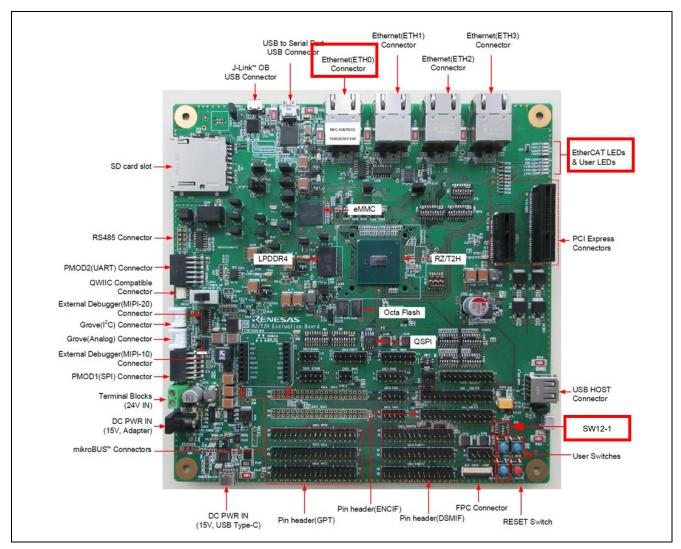

You can select the operating mode of the sample program by means of switch settings on the evaluation board. Refer to Table 2.1 for the operating mode selection method.

| Board       | Switch | MCU Port | MCU Pin | Operating Mode        |

|-------------|--------|----------|---------|-----------------------|

| RZ/T2M RSK+ | SW3-1  | P11_0    | Y18     | OFF: Application mode |

|             |        |          |         | ON: Update mode       |

| RZ/T2L RSK+ | SW3-2  | P04_1    | F1      | OFF: Application mode |

|             |        |          |         | ON: Update mode       |

| RZ/N2L RSK+ | SW3-1  | P13_6    | M13     | OFF: Application mode |

|             |        |          |         | ON: Update mode       |

| RZ/T2H EVB  | SW12-1 | P35_3    | V22     | OFF: Application mode |

|             |        |          |         | ON: Update mode       |

| RZ/N2H EVB  | DSW1-1 | P27_2    | B24     | OFF: Application mode |

|             |        | _        |         | ON: Update mode       |

Table 2.1 Switches Used for Operating Mode Selection

The update program is launched at startup when update mode is selected as the operating mode, and the user application program is launched at startup when application mode is selected. Therefore, the sample program cannot perform an update while a user application program is running.

## 2.2 Sample Program Configuration

Operating mode checking and launching of the program corresponding to the operating mode is performed by a loader program. In this document, the loader program is referred to as SSBL.

## 2.3 Using External Flash Memory

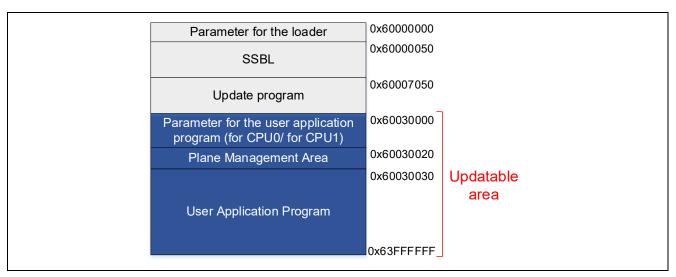

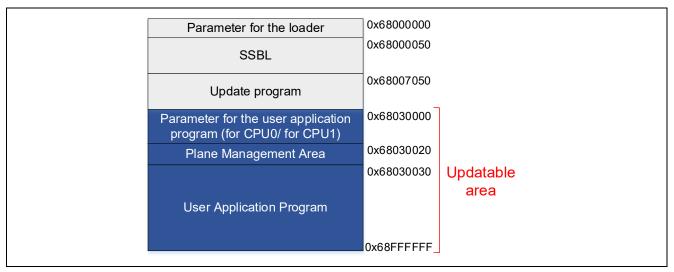

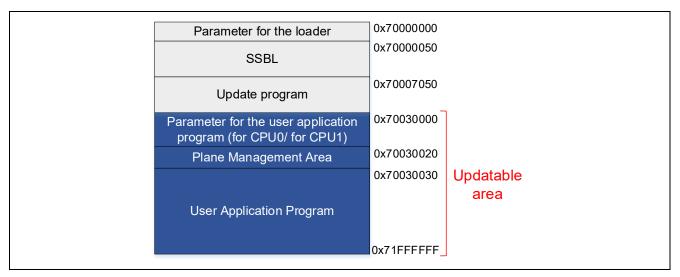

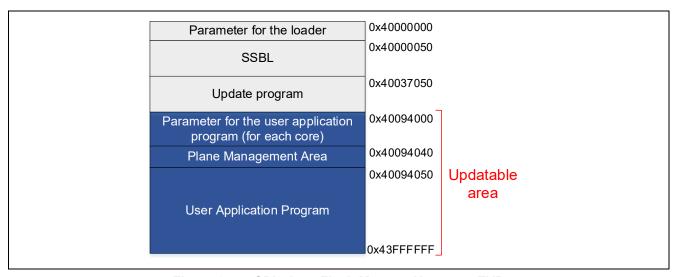

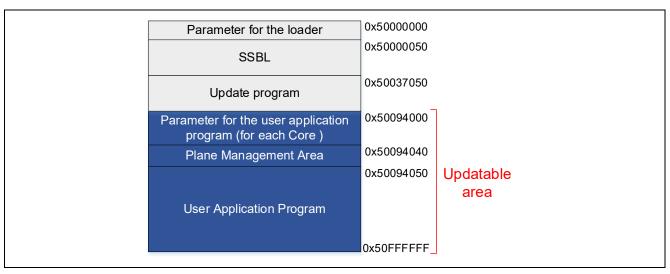

The sample program stores the programs that comprise the system in the external flash memory on the evaluation board, then loads them into the RAM and runs them. Figure 2.2, Figure 2.3, Figure 2.4, Figure 2.5 and Figure 2.6 show how the sample program utilizes the external flash memory.

The sample program updates the target user application program, but it does not update the loader program and update program. Therefore, when updating fails, any number of update attempts may be performed until the update succeeds.

In this sample program, you can configure whether the user application program area of the external flash memory that can be updated by the update program is treated as one plane or divided into two planes. If the user application program area of the external flash memory is treated as one plane, updating the user application program will overwrite a user application program in the external flash memory. If the user application program area is divided into two planes, updating the user application program area will update the user application program area on one side of the two planes in the external flash memory and leave the program before the update in the other user application program area.

Figure 2.2 xSPI0 Area Flash Memory Usage on RSK+

Figure 2.3 xSPI1 Area Flash Memory Usage on RSK+

Figure 2.4 External Bus Area Flash Memory Usage on RSK+

Figure 2.5 xSPI0 Area Flash Memory Usage on EVB

Figure 2.6 xSPI1 Area Flash Memory Usage on EVB

## 3. Configuring the Firmware Update System

The system configuration procedures for updating user application programs using the pre-built items supplied as part of the sample program package are explained in Sections 3.1 to 3.5 for each corresponding MPU.

If you want to build an update program, SSBL and user application by building the sample project instead of using the pre-built items as they are, please refer to Sections 3.6 to 3.8.

## 3.1 Configuring the Firmware Update System for RZ/T2M

Table 3.1 shows the environment required for configuring the RZ/T2M RSK+. Table 3.2 lists the user application program written during device setup for RZ/T2M.

Table 3.1 Setup Environment for RZ/T2M RSK+

| Name                                | Remarks                                                                                             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|

| Renesas Starter Kit+ for RZ/T2M     | RZ/T2M RSK+                                                                                         |

| USB cables                          | 1 (Mini-B, type-A)                                                                                  |

|                                     | 1 (Type-C, type-A)                                                                                  |

| Windows host PC                     | IAR Embedded Workbench or e <sup>2</sup> studio installed                                           |

| parameter_generator.py Note         | Generation tool for the parameter for the loader and the parameter for the user application program |

| device_setup.py Note                | Command sending tool for device setup                                                               |

| RZT2M_RSK_DeviceSetup.out.srec Note | S-Record format device setup sample program                                                         |

Note Included in the sample program package for RZ/T2, RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*).

Table 3.2 User Application Program Set Up for RZ/T2M

| File Name                     | Description                                                       |

|-------------------------------|-------------------------------------------------------------------|

| RZT2M_bsp_LED_0.bin           | A user application program based on the Blinky sample application |

|                               | included in the Flexible Software Package RZ/T2M pack.            |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The program is assigned from 0x00000000 in the ATCM area.         |

|                               | The following LEDs will light up at startup.                      |

|                               | User LED0: BSP_IO_PORT_19_PIN_6                                   |

| parameter_RZT2M_bsp_LED_0.bin | Parameter for the user application program                        |

|                               | (RZT2M_bsp_LED_0.bin). This file is created after building        |

|                               | RZT2M_bsp_LED_0.bin.                                              |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The parameter file sets the following xSPI0 address space.        |

|                               | External flash address where the program is stored: 0x60030030    |

|                               | RAM address where the program is loaded: 0x00000000               |

### 3.1.1 Concatenate Program and Parameter

Use fwupdate\_utility.py to concatenate the Update program, SSBL including the parameter for the loader, and the parameter for the user application program. The concatenated data is programmed at the beginning of the external flash. See Table 5.13 for memory maps of the concatenated data.

Open a command prompt on the host PC and run the following command.

[Only for multi-core configuration] You must specify both the user application parameters for CPU0 (--param\_cpu\_core0) and the user application parameters for CPU1 (--param\_cpu\_core\_1).

The following command will generate initial\_image\_RZT2M\_xspi0.bin:

```

python fwupdate_utility.py setupfile --param_loader RZT2M_RSK_SSBL_xspi0.bin

--param_cpu_core_0 parameter_RZT2M_bsp_LED_0.bin --mpu rzt2m --update_prog

RZT2M RSK FWUpdate.bin -o initial image RZT2M xspi0.bin

```

### 3.1.2 Program to Flash

Programming the update program and user application program are accomplished using device setup tool and sample program. Refer to chapter 2 in RZ/T2, RZ/N2 Device Setup Guide for Flash boot for the procedure.

1. Write program files to external flash on RSK+ using device\_setup.py. Open a command prompt on the host PC and run the following command.

The programmable area changes depending on the set boot mode. Please check 5.3.5 for boot modes and corresponding memory maps.

The initial image file (initial\_image\_RZ\*\_xspi0.bin) is programmed at the top of the external. The user application (RZ\*\_bsp\_LED\_\*.bin) is programmed with the flash address specified during parameter generation.

#### RZ/T2M:

```

> python device_setup.py writeflash --port COM4 --addr 60000000 -i

initial_image_RZT2M_xspi0.bin

writeflash : Setup success.

> python device_setup.py writeflash --port COM4 --addr 60030030 -i

RZT2M_bsp_LED_0.bin

writeflash : Setup success.

```

2. Set the SW on the RSK+ board to the following, User DIP Switch SW3-1 to OFF and press the reset button S3

After that, to confirm that the user application program starts and User LED0 on the board blinks.

#### RZ/T2M:

| SW    | Setting | Description                              |

|-------|---------|------------------------------------------|

| SW4.1 | ON      | xSPI0 boot mode (x1 boot Serial flash)   |

| SW4.2 | ON      |                                          |

| SW4.3 | ON      |                                          |

| SW4.4 | ON      | JTAG Authentication by Hash is disabled. |

| SW4.5 | OFF     | ATCM 1 wait                              |

| SW6.1 | ON      | Enable LED0                              |

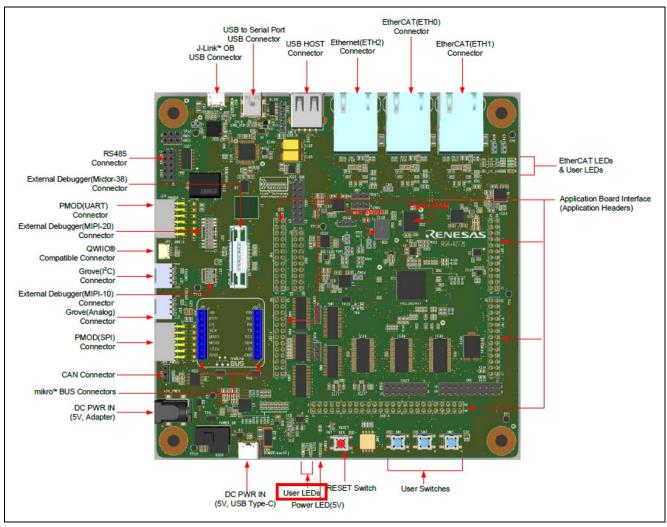

Figure 3.1 Location of User LEDs (LED0) for RZ/T2M

## 3.2 Configuring the Firmware Update System for RZ/T2L

Table 3.3 shows the environment required for configuring the RZ/T2L RSK+. Table 3.4 lists the user application program written during device setup for RZ/T2L.

Table 3.3 Setup Environment for RZ/T2L RSK+

| Name                                    | Remarks                                                                                             |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------|

| Renesas Starter Kit+ for RZ/T2L         | RZ/T2L RSK+                                                                                         |

| USB cables                              | 1 (Mini-B, type-A)                                                                                  |

|                                         | 1 (Type-C, type-A)                                                                                  |

| Windows host PC                         | IAR Embedded Workbench or e <sup>2</sup> studio installed                                           |

| parameter_generator.py Note             | Generation tool for the parameter for the loader and the parameter for the user application program |

| device_setup.py Note                    | Command sending tool for device setup                                                               |

| RZT2L_RSK_DeviceSetup_usb.out.srec Note | S-Record format device setup sample program                                                         |

Note Included in the sample program package for RZ/T2, RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*).

Table 3.4 User Application Program Set Up for RZ/T2L

| File Name                     | Description                                                       |

|-------------------------------|-------------------------------------------------------------------|

| RZT2L_bsp_LED_1.bin           | A user application program based on the Blinky sample application |

|                               | included in the Flexible Software Package RZ/T2L pack.            |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The program is assigned from 0x00000000 in the ATCM area.         |

|                               | The following LEDs will light up at startup.                      |

|                               | User LED0: BSP_IO_PORT_17_PIN_6                                   |

| parameter_RZT2L_bsp_LED_1.bin | Parameter for the user application program                        |

|                               | (RZT2L_bsp_LED_1.bin). This file is created after building        |

|                               | RZT2L_bsp_LED_1.bin.                                              |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The following OSPI flash addresses are set in the parameter file. |

|                               | External flash address where the program is stored: 0x60030030    |

|                               | RAM address where the program is loaded: 0x00000000               |

## 3.2.1 Concatenate Program and Parameter

Use fwupdate\_utility.py to concatenate the Update program, SSBL including the parameter for the loader, and the parameter for the user application program. The concatenated data is programmed at the beginning of the external flash. See Table 5.13 for memory maps of the concatenated data.

Open a command prompt on the host PC and run the following command.

The following command will generate initial image RZT2L xspi0.bin:

python fwupdate\_utility.py setupfile --param\_loader RZT2L\_RSK\_SSBL\_xspi0.bin

--param\_cpu\_core\_0 parameter\_RZT2L\_bsp\_LED\_1.bin --mpu rzt2l --update\_prog

RZT2L RSK FWUpdate.bin -o initial image RZT2L xspi0.bin

#### 3.2.2 Program to Flash

Programming the update program and user application program are accomplished using device setup tool and sample program. Refer to chapter 2 in *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* (*R01AN6471EJ\*\*\*\**) for the procedure.

1. Write program files to external flash on RSK+ using device\_setup.py. Open a command prompt on the host PC and run the following command.

The programmable area changes depending on the set boot mode. Please check 5.3.5 for boot modes and corresponding memory maps.

The initial image file (initial\_image\_RZ\*\_xspi0.bin) is programmed at the top of the external. The user application (RZ\*\_bsp\_LED\_\*.bin) is programmed with the flash address specified during parameter generation.

#### RZ/T2L:

```

> python device_setup.py writeflash --port COM4 --addr 60000000 -i

initial_image_RZT2L_xspi0.bin

writeflash : Setup success.

> python device_setup.py writeflash --port COM4 --addr 60030030 -i

RZT2L_bsp_LED_1.bin

writeflash : Setup success.

```

2. Set the SW on the RSK+ board to the following, User DIP Switch SW3-2 to OFF and press the reset button S3.

After that, to confirm that the user application program starts and User LED1 on the board blinks.

#### RZ/T2L:

| SW    | Setting | Description                              |

|-------|---------|------------------------------------------|

| SW4.1 | ON      | xSPI0 boot mode (x1 boot Serial flash)   |

| SW4.2 | ON      |                                          |

| SW4.3 | ON      |                                          |

| SW4.4 | OFF     | ATCM wait cycle = 1 wait.                |

| SW4.5 | ON      | JTAG Authentication by Hash is disabled. |

Figure 3.2 Location of User LEDs (LED1) for RZ/T2L

## 3.3 Configuring the Firmware Update System for RZ/N2L

Table 3.5 shows the environment required for configuring the RZ/N2L RSK+.

Table 3.6 lists the user application program written during device setup for RZ/N2L.

Table 3.5 Setup Environment for RZ/N2L RSK+

| Name                                     | Remarks                                                   |

|------------------------------------------|-----------------------------------------------------------|

| Renesas Starter Kit+ for RZ/N2L          | RZ/N2L RSK+                                               |

| USB cables                               | 1 (Mini-B, type-A)                                        |

|                                          | 1 (Type-C, type-A)                                        |

| Windows host PC                          | IAR Embedded Workbench or e <sup>2</sup> studio installed |

| parameter_generator.py Note              | Generation tool for the parameter for the loader and the  |

|                                          | parameter for the user application program                |

| device_setup.py Note                     | Command sending tool for device setup                     |

| RZN2L_RSK_DeviceSetup_qspi.out.srec Note | S-Record format device setup sample program               |

Note Included in the sample program package for RZ/T2, RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*).

Table 3.6 User Application Program Set Up for RZ/N2L

| File Name                     | Description                                                       |

|-------------------------------|-------------------------------------------------------------------|

| RZN2L_bsp_LED_0.bin           | A user application program based on the Blinky sample application |

|                               | included in the Flexible Software Package RZ/N2L pack.            |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The program is assigned from 0x00000000 in the ATCM area.         |

|                               | The following LEDs will light up at startup.                      |

|                               | User LED0: BSP_IO_PORT_18_PIN_2                                   |

| parameter_RZN2L_bsp_LED_0.bin | Parameter for the user application program                        |

|                               | (RZN2L_bsp_LED_0.bin). This file is created after building        |

|                               | RZN2L_bsp_LED_0.bin.                                              |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The parameter file sets the following xSPI0 address space.        |

|                               | External flash address where the program is stored: 0x60030030    |

|                               | RAM address where the program is loaded: 0x00000000               |

### 3.3.1 Concatenate Program and Parameter

Use fwupdate\_utility.py to concatenate the Update program, SSBL including the parameter for the loader, and the parameter for the user application program. The concatenated data is programmed at the beginning of the external flash. See Table 5.13 for memory maps of the concatenated data.

Open a command prompt on the host PC and run the following command.

The following command will generate initial\_image\_RZN2L\_xspi0.bin:

python fwupdate\_utility.py setupfile --param\_loader RZN2L\_RSK\_SSBL\_xspi0.bin

--param\_cpu\_core\_0 parameter\_RZN2L\_bsp\_LED\_0.bin --mpu rzn2l --update\_prog

RZN2L\_RSK\_FWUpdate.bin -o initial\_image\_RZN2L\_xspi0.bin

### 3.3.2 Program to Flash

Programming the update program and user application program are accomplished using device setup tool and sample program. Refer to chapter 2 in *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* (*R01AN6471EJ\*\*\*\**) for the procedure.

1. Write program files to external flash on RSK+ using device\_setup.py. Open a command prompt on the host PC and run the following command.

The programmable area changes depending on the set boot mode. Please check 5.3.5 for boot modes and corresponding memory maps.

The initial image file (initial\_image\_RZ\*\_xspi0.bin) is programmed at the top of the external. The user application (RZ\*\_bsp\_LED\_\*.bin) is programmed with the flash address specified during parameter generation.

#### RZ/N2L:

```

> python device_setup.py writeflash --port COM4 --addr 60000000 -i

initial_image_RZN2L_xspi0.bin

writeflash : Setup success.

> python device_setup.py writeflash --port COM4 --addr 60030030 -i

RZN2L_bsp_LED_0.bin

writeflash : Setup success.

```

2. Set the SW on the RSK+ board to the following, User DIP Switch SW3-1 to OFF and press the reset button S3.

After that, to confirm that the user application program starts and User LED0 on the board blinks.

### RZ/N2L:

| SW    | Setting | Description                              |

|-------|---------|------------------------------------------|

| SW4.1 | ON      | xSPI0 boot mode (x1 boot Serial flash)   |

| SW4.2 | ON      |                                          |

| SW4.3 | ON      |                                          |

| SW4.4 | ON      | JTAG Authentication by Hash is disabled. |

Figure 3.3 Location of User LEDs (LED0) for RZ/N2L

## 3.4 Configuring the Firmware Update System for RZ/T2H

Table 3.7 shows the environment required for configuring the RZ/T2H EVB. Table 3.8 lists the user application program written during device setup for RZ/T2H Cortex®-R52. Table 3.9 lists the user application program written during device setup for RZ/T2H Cortex®-A55.

Table 3.7 Setup Environment for RZ/T2H EVB

| Name                                | Remarks                                                                                             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|

| RZ/T2H Evaluation Board             | RZ/T2H EVB                                                                                          |

| USB cables                          | 1 (Mini-B, type-A)                                                                                  |

|                                     | 1 (Type-C, type-A)                                                                                  |

| Windows host PC                     | IAR Embedded Workbench or e <sup>2</sup> studio installed                                           |

| parameter_generator.py Note         | Generation tool for the parameter for the loader and the parameter for the user application program |

| device_setup.py Note                | Command sending tool for device setup                                                               |

| RZT2H_EVB_DeviceSetup.out.srec Note | S-Record format device setup sample program                                                         |

Note Included in the sample program package for *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* (*R01AN6471EJ\*\*\*\**).

Table 3.8 User Application Program Set Up for RZ/T2H Cortex®-R52

| File Name                     | Description                                                       |

|-------------------------------|-------------------------------------------------------------------|

| RZT2H_bsp_LED_0.bin           | A user application program based on the Blinky sample application |

|                               | included in the Flexible Software Package RZ/T2H pack.            |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The program is assigned from 0x00000000 in the ATCM area.         |

|                               | The following LEDs will light up at startup.                      |

|                               | User LED0: BSP_IO_PORT_23_PIN_1                                   |

| parameter_RZT2H_bsp_LED_0.bin | Parameter for the user application program                        |

|                               | (RZT2H_bsp_LED_0.bin). This file is created after building        |

|                               | RZT2H_bsp_LED_0.bin.                                              |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The parameter file sets the following xSPI0 address space.        |

|                               | External flash address where the program is stored: 0x40094050    |

|                               | RAM address where the program is loaded: 0x00000000               |

Table 3.9 User Application Program Set Up for RZ/T2H Cortex®-A55

| File Name                     | Description                                                                                                                |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| RZT2H_bsp_LED_0.bin           | A user application program based on the Blinky sample application included in the Flexible Software Package RZ/T2H pack.   |

|                               | See section 3.8 for detailed creation instructions.                                                                        |

|                               | The program is assigned from 0x10050000 in the SystemRAM                                                                   |

|                               | area.                                                                                                                      |

|                               | The following LEDs will light up at startup.                                                                               |

|                               | User LED0: BSP_IO_PORT_23_PIN_1                                                                                            |

| parameter_RZT2H_bsp_LED_0.bin | Parameter for the user application program (RZT2H_bsp_LED_0.bin). This file is created after building RZT2H_bsp_LED_0.bin. |

|                               | See section 3.8 for detailed creation instructions.                                                                        |

|                               | The parameter file sets the following xSPI0 address space.                                                                 |

|                               | External flash address where the program is stored: 0x40094050                                                             |

|                               | RAM address where the program is loaded: 0x10050000                                                                        |

### 3.4.1 Concatenate Program and Parameter

Use fwupdate\_utility.py to concatenate the Update program, SSBL including the parameter for the loader, and the parameter for the user application program. The concatenated data is programmed at the beginning of the external flash. See Table 5.18 for memory maps of the concatenated data.

Open a command prompt on the host PC and run the following command.

#### RZ/T2H Cortex®-R52:

[Only for multi-core configuration] You must specify both the user application parameters for CPU0 (--param\_cpu\_core\_0) and the user application parameters for CPU1 (--param\_cpu\_core\_1).

The following command will generate initial\_image\_RZT2H\_xspi0.bin:

```

python fwupdate_utility.py setupfile --param_loader RZT2H_EVB_SSBL_xspi0.bin

--param_cpu_core_0 parameter_RZT2H_bsp_LED_0.bin --mpu rzt2h --update_prog

RZT2H EVB FWUpdate.bin -o initial image RZT2H xspi0.bin

```

#### RZ/T2H Cortex®-A55:

[Only for multi-core configuration] You must specify either the user application parameters for Core 1 (--param\_cpu\_core\_1), Core 2 (--param\_cpu\_core\_2) or Core 3 (--param\_cpu\_core\_3) along with the user application parameter for Core 0 (--param\_cpu\_core\_0).

The following command will generate initial\_image\_RZT2H\_xspi0.bin:

```

python fwupdate_utility.py setupfile --param_loader

RZT2H_EVB_CA55_SSBL_xspi0.bin --param_cpu_core_0

parameter_RZT2H_bsp_LED_0.bin --mpu rzt2h --update_prog

RZT2H_EVB_CA55_FWUpdate.bin -o initial_image_RZT2H_xspi0.bin

```

### 3.4.2 Program to Flash

Programming the update program and user application program are accomplished using device setup tool and sample program. Refer to chapter 2 in *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* for the procedure.

1. Write program files to external flash on EVB using device\_setup.py. Open a command prompt on the host PC and run the following command.

The programmable area changes depending on the set boot mode. Please check 5.3.6 for boot modes and corresponding memory maps.

The initial image file (initial\_image\_RZ\*\_xspi0.bin) is programmed at the top of the external. The user application (RZ\*\_bsp\_LED\_\*.bin) is programmed with the flash address specified during parameter generation.

#### RZ/T2H Cortex®-R52 or Cortex®-A55:

```

> python device_setup.py writeflash --port COM4 --addr 40000000 -i

initial_image_RZT2H_xspi0.bin

writeflash : Setup success.

> python device_setup.py writeflash --port COM4 --addr 40094050 -i

RZT2H_bsp_LED_0.bin

writeflash : Setup success.

```

2. Set the SW on the EVB to the following, User DIP Switch SW12-1 to OFF and press the reset button SW13

After that, to confirm that the user application program starts and User LED0 on the board blinks.

### RZ/T2H:

| SW     | Setting | Description                                |

|--------|---------|--------------------------------------------|

| SW14.1 | ON      | xSPI0 boot mode (x1 boot Serial flash)     |

| SW14.2 | ON      |                                            |

| SW14.3 | ON      |                                            |

| SW14.4 | OFF     | Cortex®-R52 CPU0 ATCM 1 wait               |

| SW14.5 | OFF     | Cortex®-R52 CPU1 ATCM 1 wait               |

| SW14.6 | OFF     | Supply voltage of boot peripheral is 3.3 V |

| SW14.7 | ON      | JTAG Authentication by Hash is disabled.   |

Figure 3.4 Location of User LEDs (LED0) for RZ/T2H

## 3.5 Configuring the Firmware Update System for RZ/N2H

Table 3.10 shows the environment required for configuring the RZ/N2H EVB. Table 3.11 lists the user application program written during device setup for RZ/N2H Cortex®-R52. Table 3.12 lists the user application program written during device setup for RZ/N2H Cortex®-A55.

Table 3.10 Setup Environment for RZ/N2H EVB

| Name                                | Remarks                                                                                             |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| RZ/N2H Evaluation Board             | RZ/N2H EVB                                                                                          |  |

| USB cables                          | 1 (Mini-B, type-A)                                                                                  |  |

|                                     | 1 (Type-C, type-A)                                                                                  |  |

| Windows host PC                     | IAR Embedded Workbench or e <sup>2</sup> studio installed                                           |  |

| parameter_generator.py Note         | Generation tool for the parameter for the loader and the parameter for the user application program |  |

| device_setup.py Note                | Command sending tool for device setup                                                               |  |

| RZN2H_EVB_DeviceSetup.out.srec Note | S-Record format device setup sample program                                                         |  |

Note Included in the sample program package for *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* (*R01AN6471EJ\*\*\*\**).

Table 3.11 User Application Program Set Up for RZ/N2H Cortex®-R52

| File Name                     | Description                                                       |

|-------------------------------|-------------------------------------------------------------------|

| RZN2H_bsp_LED_3.bin           | A user application program based on the Blinky sample application |

|                               | included in the Flexible Software Package RZ/N2H pack.            |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The program is assigned from 0x00000000 in the ATCM area.         |

|                               | The following LEDs will light up at startup.                      |

|                               | User LED3: BSP_IO_PORT_31_PIN_6                                   |

| parameter_RZN2H_bsp_LED_3.bin | Parameter for the user application program                        |

|                               | (RZN2H_bsp_LED_3.bin). This file is created after building        |

|                               | RZN2H_bsp_LED_3.bin.                                              |

|                               | See section 3.8 for detailed creation instructions.               |

|                               | The parameter file sets the following xSPI0 address space.        |

|                               | External flash address where the program is stored: 0x40094050    |

|                               | RAM address where the program is loaded: 0x00000000               |

Table 3.12 User Application Program Set Up for RZ/N2H Cortex®-A55

| File Name                     | Description                                                                                                              |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| RZN2H_bsp_LED_3.bin           | A user application program based on the Blinky sample application included in the Flexible Software Package RZ/N2H pack. |

|                               | See section 3.8 for detailed creation instructions.                                                                      |

|                               | The program is assigned from 0x10050000 in the SystemRAM                                                                 |

|                               | area.                                                                                                                    |

|                               | The following LEDs will light up at startup.                                                                             |

|                               | User LED3: BSP_IO_PORT_31_PIN_6                                                                                          |

| parameter_RZN2H_bsp_LED_3.bin | Parameter for the user application program                                                                               |

|                               | (RZN2H_bsp_LED_3.bin). This file is created after building                                                               |

|                               | RZN2H_bsp_LED_3.bin.                                                                                                     |

|                               | See section 3.8 for detailed creation instructions.                                                                      |

|                               | The parameter file sets the following xSPI0 address space.                                                               |

|                               | External flash address where the program is stored: 0x40094050                                                           |

|                               | RAM address where the program is loaded: 0x10050000                                                                      |

### 3.5.1 Concatenate Program and Parameter

Use fwupdate\_utility.py to concatenate the Update program, SSBL including the parameter for the loader, and the parameter for the user application program. The concatenated data is programmed at the beginning of the external flash. See Table 5.18 for memory maps of the concatenated data.

Open a command prompt on the host PC and run the following command.

#### RZ/N2H Cortex®-R52:

[Only for multi-core configuration] You must specify both the user application parameters for CPU0 (--param\_cpu\_core0) and the user application parameters for CPU1 (--param\_cpu\_core\_1).

The following command will generate initial image RZN2H xspi0.bin:

```

python fwupdate_utility.py setupfile --param_loader RZN2H_EVB_SSBL_xspi0.bin

--param_cpu_core_0 parameter_RZN2H_bsp_LED_3.bin --mpu rzn2h --update_prog

RZN2H EVB FWUpdate.bin -o initial image RZN2H xspi0.bin

```

#### RZ/N2H Cortex®-A55:

[Only for multi-core configuration] You must specify either the user application parameters for Core 1 (--param\_cpu\_core\_1), Core 2 (--param\_cpu\_core\_2) or Core 3 (--param\_cpu\_core\_3) along with the user application parameter for Core 0 (--param\_cpu\_core\_0).

The following command will generate initial\_image\_RZN2H\_xspi0.bin:

```

python fwupdate_utility.py setupfile --param_loader

RZN2H_EVB_CA55_SSBL_xspi0.bin --param_cpu_core_0

parameter_RZN2H_bsp_LED_3.bin --mpu rzn2h --update_prog

RZN2H_EVB_CA55_FWUpdate.bin -o initial_image_RZN2H_xspi0.bin

```

## 3.5.2 Program to Flash

Programming the update program and user application program are accomplished using device setup tool and sample program. Refer to chapter 2 in *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot* for the procedure.

1. Write program files to external flash on EVB using device\_setup.py. Open a command prompt on the host PC and run the following command.

The programmable area changes depending on the set boot mode. Please check 5.3.6 for boot modes and corresponding memory maps.

The initial image file (initial\_image\_RZ\*\_xspi0.bin) is programmed at the top of the external. The user application (RZ\*\_bsp\_LED\_\*.bin) is programmed with the flash address specified during parameter generation.

#### RZ/N2H Cortex®-R52 or Cortex®-A55:

```

> python device_setup.py writeflash --port COM4 --addr 40000000 -i

initial_image_RZN2H_xspi0.bin

writeflash : Setup success.

> python device_setup.py writeflash --port COM4 --addr 40094050 -i

RZN2H_bsp_LED_3.bin

writeflash : Setup success.

```

2. Set the SW on the EVB to the following, User DIP Switch DSW1-1 to OFF and press the reset button SW5

After that, to confirm that the user application program starts and User LED3 on the board blinks.

### RZ/N2H:

| SW     | Setting | Description                                |

|--------|---------|--------------------------------------------|

| DSW3.1 | ON      | xSPI0 boot mode (x1 boot Serial flash)     |

| DSW3.2 | ON      |                                            |

| DSW3.3 | ON      |                                            |

| DSW3.4 | OFF     | Cortex®-R52 CPU0 ATCM 1 wait               |

| DSW3.5 | OFF     | Cortex®-R52 CPU1 ATCM 1 wait               |

| DSW3.6 | OFF     | Supply voltage of boot peripheral is 3.3 V |

| DSW3.7 | ON      | JTAG Authentication by Hash is disabled.   |

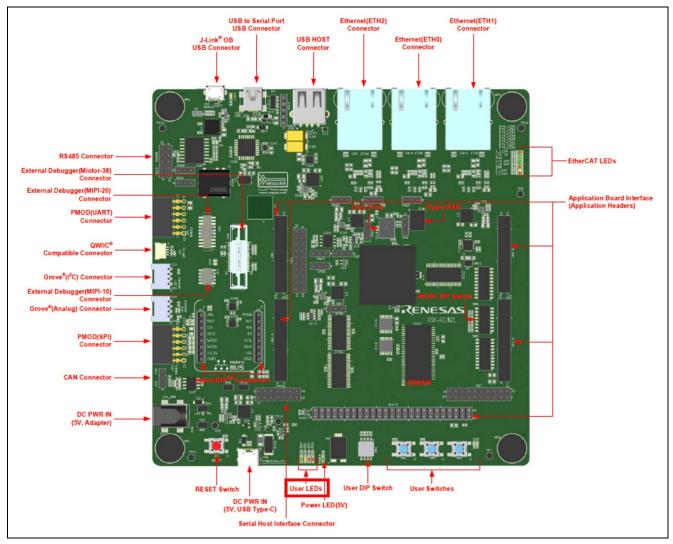

Figure 3.5 Location of User LEDs (LED3) for RZ/N2H

## 3.6 Update Program Configuration

IAR Embedded Workbench for ARM is used as the development environment of the update program.

Open the following workspace, select the update program project (RZ\*\_\*\_FWUpdate), and build the project.

In the default configuration, the update program is for xSPI0 boot mode and flash one plane. The configurations of the update program can be changed with the following files.

RZ\* \* FWUpdate Rev\*\src\fwupdate cfg.h

For RZ/N2L only, if you use 16-bit bus boot mode, you also need to change the sample program project settings by referring to Section 5.3.7.

The configuration of the update program is shown in Table 3.13.

Table 3.13 Configurations for update program

| Configuration items | Configurable values        | Description                        |

|---------------------|----------------------------|------------------------------------|

| FWUPDATE_CFG_BOOT_  | BOOT_MODE_XSPI0            | Default settings.                  |

| MODE_SELECT         |                            | Specified when using in xSPI0      |

|                     |                            | boot mode (x1 boot serial flash).  |

|                     | BOOT_MODE_XSPI1            | Specified when using in xSPI1      |

|                     |                            | boot mode (x1 boot serial flash).  |

|                     | BOOT_MODE_NOR              | Specified when using in 16-bit bus |

|                     |                            | boot mode (NOR flash).             |

|                     |                            | Not supported on RZ/T2H and        |

|                     |                            | RZ/N2H.                            |

| FWUPDATE_CFG_FLASH  | FLASH_MNG_AREA_SINGLE_BANK | Default settings.                  |

| _MNG_AREA           |                            | Specify when using the user        |

|                     |                            | application program area on the    |

|                     |                            | external flash for one plane       |

|                     |                            | management.                        |

|                     | FLASH_MNG_AREA_DUAL_BANK   | Specify this when using the user   |

|                     |                            | application program area of the    |

|                     |                            | external flash for two plane       |

|                     |                            | management.                        |

### 3.7 SSBL Configuration

IAR Embedded Workbench for ARM is used as the development environment of SSBL.

Open the following workspace, select the SSBL project (RZ\*\_\*\_SSBL), and build the project.

In the default configuration, the update program is for xSPI0 boot mode, single core, and flash one plane. The configurations of the SSBL can be changed with the following files.

RZ\* \* SSBL Rev\*\src\ssbl cfg.h

For RZ/N2L only, if you use 16-bit bus boot mode, you also need to change the sample program project settings by referring to Section 5.3.7.

[Only for multi-core configuration] If you want to run the user application on Cortex®-R52 CPU1 or Cortex®-A55 Core 1, Core 2, and Core 3, you will need SSBL that has been changed to multi-core settings.

The configuration of SSBL is shown in Table 3.14.

Table 3.14 Configurations for SSBL

| Configuration items           | Configurable values               | Description                                                                                      |

|-------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|

| SSBL_CFG_BOOT_MODE            | BOOT_MODE_XSPI0                   | Default settings.                                                                                |

| _SELECT                       |                                   | Specified when using in xSPI0                                                                    |

|                               |                                   | boot mode (x1 boot serial flash).                                                                |

|                               | BOOT_MODE_XSPI1                   | Specified when using in xSPI1                                                                    |

|                               |                                   | boot mode (x1 boot serial flash).                                                                |

|                               | BOOT_MODE_NOR                     | Specified when using in 16-bit bus boot mode (NOR flash).                                        |

|                               |                                   | Not supported on RZ/T2H and RZ/N2H.                                                              |

| SSBL_CFG_OPERATING_           | SINGLE_CORE                       | Default settings.                                                                                |

| CORE_MODE                     |                                   | Single-core configuration. Specify when using as a single core.                                  |

|                               | MULTI_CORE                        | Multi-core configuration. Specify when using as Cortex®-R52 dual core or Cortex®-A55 multi core. |

| SSBL_CFG_MULTI_CORE           | DISABLE                           | Default settings.                                                                                |

| _CA55_CORE_1 Note             |                                   | Disables user application launch                                                                 |

|                               |                                   | on Cortex®-A55 Core 1.                                                                           |

|                               | ENABLE                            | Enables user application launch on Cortex®-A55 Core 1.                                           |

| SSBL_CFG_MULTI_CORE           | DISABLE                           | Default settings.                                                                                |

| _CA55_CORE_2 Note             |                                   | Disables user application launch on Cortex®-A55 Core 2.                                          |

|                               | ENABLE                            | Enables user application launch on Cortex®-A55 Core 2.                                           |

| SSBL_CFG_MULTI_CORE           | DISABLE                           | Default settings.                                                                                |

| _CA55_CORE_3 Note             |                                   | Disables user application launch on Cortex®-A55 Core 3.                                          |

|                               | ENABLE                            | Enables user application launch on Cortex®-A55 Core 3.                                           |

| SSBL_CFG_FLASH_MNG_           | FLASH_MNG_AREA_SINGLE_BANK        | Default settings.                                                                                |

| AREA                          |                                   | Specify when using the user                                                                      |

|                               |                                   | application program area on the                                                                  |

|                               |                                   | external flash for one plane                                                                     |

|                               |                                   | management.                                                                                      |

|                               | FLASH_MNG_AREA_DUAL_BANK          | Specify this when using the user                                                                 |

|                               |                                   | application program area of the                                                                  |

|                               |                                   | external flash for two plane                                                                     |

| Note: This confinite wood who | <br>n.SSBL CEG OPERATING CORE MOI | management.                                                                                      |

Note This config is used when SSBL\_CFG\_OPERATING\_CORE\_MODE is MULTI\_CORE and the operating core is Cortex®-A55 core.

After building SSBL (RZ\*\_RSK\_SSBL.bin), generate parameter for the loader for SSBL (hereinafter referred to as parameter for SSBL).

The SSBL program size (binary data size) must be a multiple of 512 bytes and less than the maximum size shown in Table 3.15. If the binary data size after the user program build is not a multiple of 512 bytes, add dummy data after the binary data to adjust it to a multiple of 512 bytes. For information on how to adjust the binary data to 512-byte units by adding project settings, refer to Section 3.3.7 in *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*)*.

Parameter for SSBL is generated using the tool parameter\_generator.py, which is included in the sample program package for the *RZ/T2*, *RZ/N2 Device Setup Guide for Flash boot (R01AN6471EJ\*\*\*\*)*.

In section 3.7.1 to 3.7.6, the procedure for generating data that concatenates the parameter for SSBL and SSBL program is explained for each MCU type.

Table 3.15 Maximum user program size

| Products          | First booting CPU core | Maximum user program size |

|-------------------|------------------------|---------------------------|

| RZ/T2M            | Cortex®-R52            | 56 KB                     |

| RZ/T2L            | Cortex®-R52            | 56 KB                     |

| RZ/N2L            | Cortex®-R52            | 120 KB                    |

| RZ/T2H and RZ/N2H | Cortex®-R52            | 52 KB                     |

|                   | Cortex®-A55            | 2036 KB                   |

#### 3.7.1 Concatenate SSBL and Parameter for RZ/T2M

The following shows an example of tool execution when xSPI0 address space flash is specified:

- External flash address where the program is stored (--src\_addr): 0x60000050

- RAM address where the program is loaded (--dest\_addr): 0x00102000

The following command generates RZT2M\_RSK\_SSBL\_xspi0.bin in which the parameter for the loader and the SSBL program are concatenated:

```

python parameter_generator.py loader --mpu rzt2m --target_cpu cr52 --mode

xspi0 --src_addr 60000050 --dest_addr 00102000 -i RZT2M_RSK_SSBL.bin -o

RZT2M RSK SSBL xspi0.bin --concat loader

```

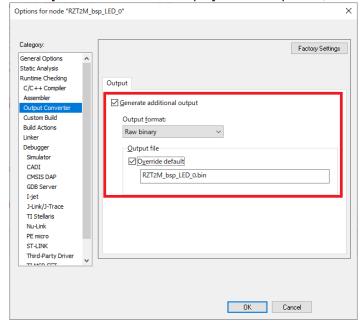

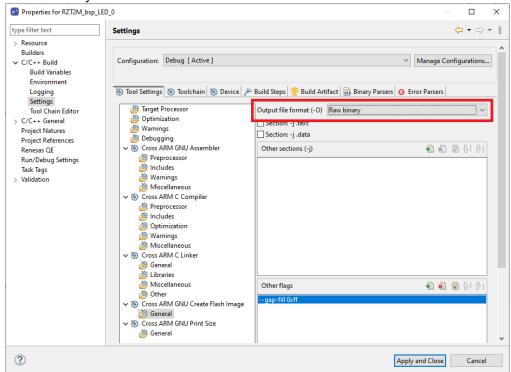

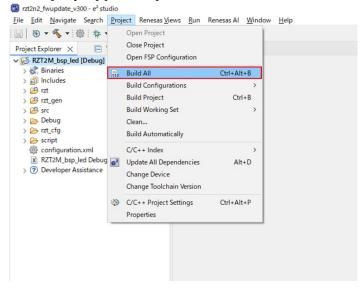

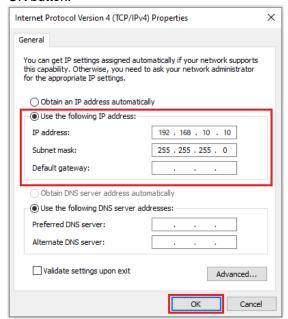

#### 3.7.2 Concatenate SSBL and Parameter for RZ/T2L