# RL78/G13

## Measurement of Standby Mode Supply Current CC-RL

R01AN4039EJ0100 Rev.1.00 Sep. 28, 2018

### Introduction

This application note describes the method for measuring the supply current of the RL78/G13 in the STOP mode or the HALT mode.

### **Target Device**

RL78/G13

When applying the sample program covered in this application note to another microcomputer, modify the program according to the specifications for the target microcomputer and conduct an extensive evaluation of the modified program.

### Contents

| 1. | Spec  | vifications                                                                 | 3    |

|----|-------|-----------------------------------------------------------------------------|------|

| 1  | .1    | Standby mode function                                                       | 4    |

| 1  | .2    | Supply current of standby mode                                              | 5    |

| 1  | .3    | Example of Circuit Configuration for Measuring Standby Mode Supply Currents | 6    |

| 1  | .4    | Important Points When Measuring Supply Currents                             | 7    |

| 2. | Oper  | ation Check Conditions                                                      | 8    |

| 3. | Rela  | ted Application Notes                                                       | 9    |

| 4. | Hard  | ware Explanation                                                            | . 10 |

| 4  | .1    | Hardware Configuration Example                                              | . 10 |

| 4  | .2    | Used Pin List                                                               | . 10 |

| 5. | Softv | vare Explanation                                                            | . 11 |

| 5  | .1    | Operation Outline                                                           | . 11 |

| -  | .2    | Option Byte Settings                                                        | . 12 |

| 5  | .3    | Functions                                                                   |      |

| -  | .4    | Function Specifications                                                     |      |

| 5  | .5    | Flowcharts                                                                  |      |

|    | 5.5.1 |                                                                             |      |

|    | 5.5.2 | 5                                                                           |      |

|    | 5.5.3 |                                                                             |      |

|    | 5.5.4 |                                                                             |      |

|    | 5.5.5 | 0                                                                           |      |

|    | 5.5.6 | Main Initializes Settings                                                   | . 23 |

| 6. | Sam   | ple Code                                                                    | . 24 |

| 7. | Refe  | rence Documents                                                             | . 24 |

#### 1. Specifications

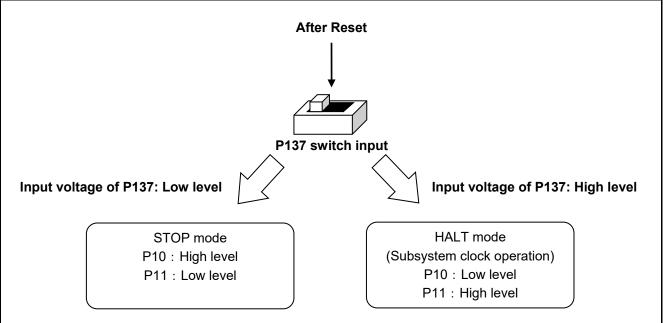

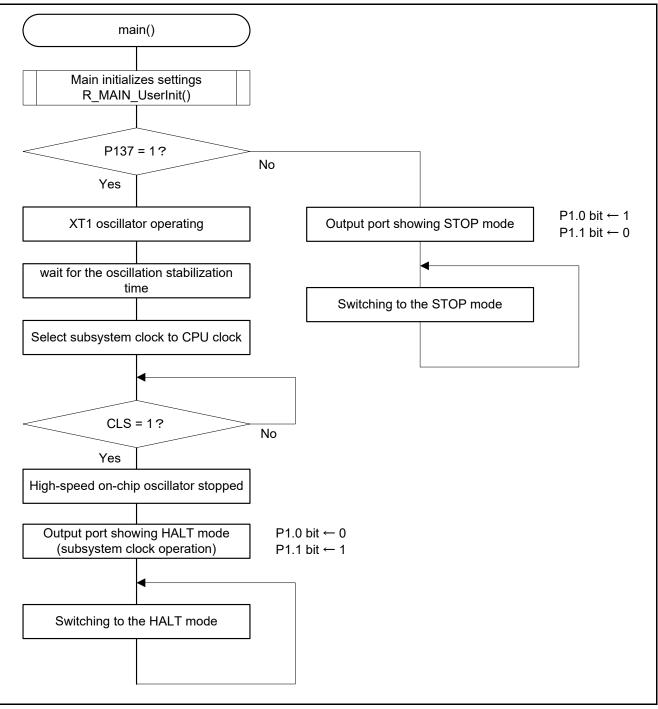

In this application note, after a reset is released, a standby mode (STOP mode, or HALT mode during CPU operation using the subsystem clock) is selected through the value of the input voltage at the P137 pin.

The transition to a standby mode can be confirmed from the output states of P10 and P11. In order to correctly measure the supply current in a standby mode, P10 and P11 must be in output mode and must be unconnected (open).

Table 1.1 lists peripheral functions to be used and their uses. Figure 1.1 shows the outline of operation, and Table 1.2 shows operation in each of the operation modes.

| Peripheral Function | Application  |

|---------------------|--------------|

| P137                | Switch input |

| P10-P11             | Status check |

|                     |              |

|                     |              |

Figure 1.1 Outline of Operation

| Table 1.2 | Explanation of the standby mode in this application note |

|-----------|----------------------------------------------------------|

|           | Explanation of the standby mode in the application note  |

| Standby mode                | CPU/peripheral hardware clock (fc∟κ)           | Port output |            |

|-----------------------------|------------------------------------------------|-------------|------------|

| Standby mode                |                                                | P10         | P11        |

| STOP mode                   | High-speed on-chip oscillator clock $(f_{IH})$ | High level  | Low level  |

| HALT mode                   | Subsystem clock (f <sub>SUB</sub> ) Note1      | Low level   | High level |

| (Subsystem clock operation) |                                                |             |            |

Note 1. The oscillation mode of the XT1 oscillator is set to ultra-low power consumption oscillation (oscillation margin: small).

### 1.1 Standby mode function

The standby mode functions used in this application note are as follows.

#### ① STOP mode

In the STOP mode, the high-speed system clock oscillator and the high-speed on-chip oscillator are stopped, to stop clocks in the entire system. The CPU operating current can be greatly reduced as a result.

Moreover, the STOP mode can be released by an interrupt request, and so by periodically switching between normal operation and standby operation, the average power supply operating current can be reduced. However, when the STOP mode is released, an oscillation stabilization time must be secured for the high -speed system clock oscillator and the high-speed on-chip oscillator.

The STOP mode is entered by executing the STOP instruction. However, a transition to the STOP mode is not possible in a state in which the subsystem clock is selected for the CPU clock.

#### ② HALT mode (subsystem clock operation)

In the HALT mode, the CPU operation clock is stopped. The real-time clock (RTC) and 12-bit interval timer, operating before the HALT mode is set, can continue operation even during the HALT mode.

This mode is useful when there is a need to promptly execute interrupt processing without waiting the length of the oscillation stabilization time, and when there is a need for frequent intermittent operation.

By executing the HALT command during normal operation using the subsystem clock, the HALT mode is entered during CPU operation using the subsystem clock.

### 1.2 Supply current of standby mode

The Hardware edition of the RL78/G13 User Manual gives typical and maximum values for the supply current in standby modes. Table 1.3 and Table 1.4 indicate whether the operating currents are included in the typical and maximum values of supply currents for standby modes set in this application note.

| Operating current                                                                                       | TYP. value   | MAX. value   |

|---------------------------------------------------------------------------------------------------------|--------------|--------------|

| Current flowing into VDD, EVDD0                                                                         | Included     | Included     |

| the input leakage current flowing when the level of the input pin is fixed to VDD, EVDD0, or VSS, EVSS0 | Included     | Included     |

| A/D converter operating current                                                                         | Not included | Not included |

| LVD operating current                                                                                   | Not included | Not included |

| Current flowing through the I/O port                                                                    | Not included | Not included |

| Current flowing through on-chip pull-up/pull-down resistors                                             | Not included | Not included |

| Current flowing when rewriting data flash                                                               | Not included | Not included |

| Real-time clock operating current                                                                       | Not included | Not included |

| 12-bit interval timer operating current                                                                 | Not included | Not included |

| Watchdog dog timer operating current                                                                    | Not included | Not included |

| Operating current of other peripheral functions                                                         | Not included | Included     |

#### Table 1.3 Supply current in STOP mode (TYP. value, MAX. value)

Table 1.4 Supply current in HALT mode (subsystem clock operating) (TYP. value, MAX. value)

| Operating current                                                                                       | TYP. value   | MAX. value   |

|---------------------------------------------------------------------------------------------------------|--------------|--------------|

| Current flowing into VDD, EVDD0                                                                         | Included     | Included     |

| the input leakage current flowing when the level of the input pin is fixed to VDD, EVDD0, or VSS, EVSS0 | Included     | Included     |

| A/D converter operating current                                                                         | Not included | Not included |

| LVD operating current                                                                                   | Not included | Not included |

| Current flowing through the I/O port                                                                    | Not included | Not included |

| Current flowing through on-chip pull-up/pull-down resistors                                             | Not included | Not included |

| Current flowing when rewriting data flash                                                               | Not included | Not included |

| Real-time clock operating current                                                                       | Included     | Included     |

| 12-bit interval timer operating current                                                                 | Not included | Not included |

| Watchdog dog timer operating current                                                                    | Not included | Not included |

| Operating current of other peripheral functions                                                         | Not included | Included     |

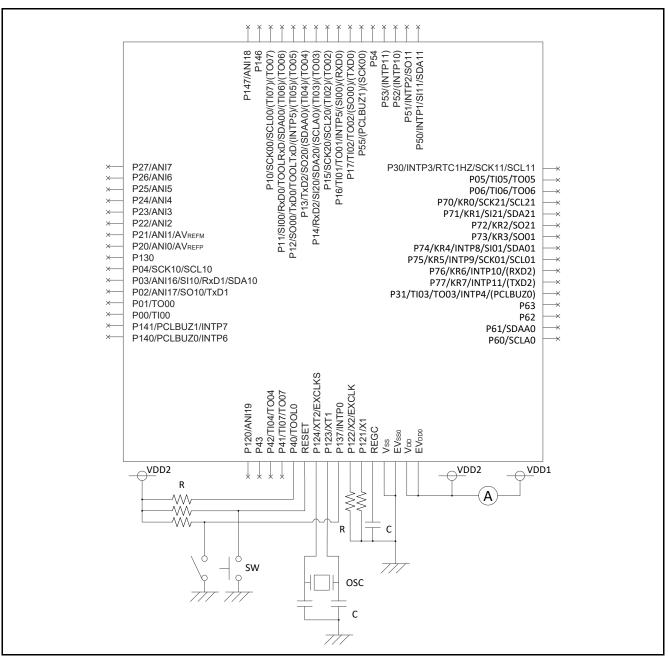

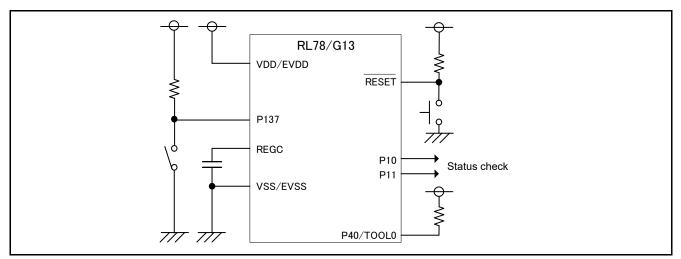

#### 1.3 Example of Circuit Configuration for Measuring Standby Mode Supply Currents

This application note provides sample code that assumes RL78/G13 peripheral circuitry as shown in Figure 1.2. By using the circuit configuration shown in Figure 1.2, the standby mode supply currents described in the Hardware edition of the RL78/G13 User Manual can be measured.

Figure 1.2 schematic

#### 1.4 Important Points When Measuring Supply Currents

The following are important points to be noted when measuring the supply currents described in the Hardware edition of the RL78/G13 User Manual.

#### ① Regarding unused pins

Unused pins should be handled properly without fail. If an unused pin is set as an input port and is unconnected (open), an intermediate potential is applied to the pin and there is the possibility that a through-current may flow. If a through-current flows, standby mode supply currents cannot be accurately measured.

#### 2 Regarding currents flowing in ports

When measuring supply currents, confirm that no port currents are flowing.

③ Regarding operating ambient temperature

Check the ambient temperature when measuring the supply currents. The typical values for supply currents given in the Hardware edition of the RL78/G13 User Manual are values for an ambient temperature of 25°C.

④ Regarding supply of a clock to peripheral hardware

The PER0 register should be used to select "Stops input clock supply" for each of the peripheral functions. If "Enables input clock supply" is selected, an operating current flows even in a state in which the peripheral functions have stopped operation.

(5) Regarding subsystem clock supply

The OSMC register should be used to select "Stops supply of subsystem clock to peripheral functions other than the real-time clock and the 12-bit interval timer" (RTCLPC = 1).

If "Enables supply of subsystem clock to peripheral functions" is selected, then there is the possibility that minute operating currents may flow even in a state in which operation of peripheral functions is stopped.

#### 6 Regarding on-chip debugging operations

In a state in which an emulator such as E1 is connected, operating currents cannot be accurately measured. Software should be written into the microcomputer and the operating current of the microcomputer alone should be measured.

### 2. Operation Check Conditions

The sample code described in this application note has been checked under the conditions listed in the table below.

| Item                                                          | Description                                                                                                |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| MCU used                                                      | RL78/G13 (R5F100LE)                                                                                        |

| Operating frequencies                                         | <ul> <li>High-speed on-chip oscillator clock: 8MHz</li> <li>CPU/peripheral hardware clock: 8MHz</li> </ul> |

| Operating voltage                                             | 3.3V (operating range 1.8V to 5.5V)                                                                        |

|                                                               | LVD operations (V <sub>LVD</sub> ): LVD off                                                                |

| Integrated development<br>environment (CS+)                   | CS+ for CC V6.00.00 from Renesas Electronics Corp.                                                         |

| C compiler (CS+)                                              | CC-RL V1.06.00 from Renesas Electronics Corp.                                                              |

| Integrated development<br>environment (e <sup>2</sup> studio) | e <sup>2</sup> studio V6.3.0 from Renesas Electronics Corp.                                                |

| C compiler (e <sup>2</sup> studio)                            | CC-RL V1.06.00 from Renesas Electronics Corp.                                                              |

| Table 2.1 | <b>Operation Check Conditions</b> |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

### 3. Related Application Notes

Application notes related to this document are shown below. Please refer to these as needed.

RL78/G13 CPU Clock Changing and Standby Settings (C Language) CC-RL (R01AN3128EJ) Application note RL78/G13 low-power Consumption Operation CC-RL (R01AN2591EJ) Application note

#### 4. Hardware Explanation

### 4.1 Hardware Configuration Example

Figure 4.1 shows an example of the hardware configuration used in this application note.

Figure 4.1 Hardware Configuration

Note: 1. This simplified circuit diagram was created to show an overview of connections only. When actually designing your circuit, make sure the design includes sufficient pin processing and meets electrical characteristic requirements. (Connect each input-only port to V<sub>DD</sub> or V<sub>SS</sub> through a resistor.)

#### 4.2 Used Pin List

Table 4.1 provides List of Pins and Functions.

| Table 4.1 | List of | Pins and | Functions |

|-----------|---------|----------|-----------|

|-----------|---------|----------|-----------|

| Pin name       | Input/Output | Function                |

|----------------|--------------|-------------------------|

| P137           | Input        | Switch input port       |

| P10-P11 Output |              | Output for status check |

#### 5. Software Explanation

#### 5.1 Operation Outline

In this application note, after a reset is released, the input voltage value of the P137 pin is used to select a standby mode (STOP mode, or HALT mode during CPU operation using the subsystem clock). The standby mode state can be determined from the output states of P10 and P11.

Details are explained in ① through ⑤ below.

① Initialize the CPU clock.

<CPU clock setup conditions>

- The 8 MHz high-speed on-chip oscillator clock is set as the CPU/peripheral hardware clock ( $f_{CLK}$ ).

- The subsystem clock pin operating mode is set to XT1 oscillation mode.

② Initialize the input/output ports.

<Input/output port setup conditions>

- Set P10-P11 to low level.

- Set P10-P11 output mode.

- ③ Check the P137 input level. Transition to the STOP mode if the P137 input is at low level, and to the HALT mode (subsystem clock operation) if it is at high level. For the STOP mode, execute ④, and for the HALT mode (subsystem clock operation), execute ⑤.

- ④ After setting P10 to high level output and P11 to low level output, transition to the STOP mode.

- (5) Switch the CPU clock from the high-speed system clock to the subsystem clock. Then, set P10 to low level output and P11 to high level output, and transition to the HALT mode.

### 5.2 Option Byte Settings

Table 5.1 lists the option byte settings.

| Address       | Setting Value | Contents                                                           |

|---------------|---------------|--------------------------------------------------------------------|

| 000C0H/010C0H | 1110 1111B    | Watchdog timer operation is stopped (count is stopped after reset) |

| 000C1H/010C1H | 1111 1111B    | LVD off                                                            |

| 000C2H/010C2H | 1010 1010B    | LS mode, High-speed on-chip oscillator<br>clock: 8MHz              |

| 000C3H/010C3H | 0000 0100B    | On-chip debugging disabled                                         |

Table 5.1 Option Byte Settings

### 5.3 Functions

Table 5.2 lists the functions.

Table 5.2 Functions

| Function name   | Outline             |

|-----------------|---------------------|

| main            | Main processing     |

| R_MAIN_UserInit | Main initial seting |

### 5.4 Function Specifications

This part describes function specifications of the sample code.

| [Function Name] | main                                                                                                                                                                                                                       |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Outline         | Main processing                                                                                                                                                                                                            |

| Header          | r_cg_macrodriver.h、r_cg_cgc.h、r_cg_port.h、r_cg_intp.h、r_cg_userdefine.h                                                                                                                                                    |

| Declaration     | _                                                                                                                                                                                                                          |

| Description     | After execution of the main user initialization function, transitions to the STOP mode if the P137 input is at low level, and transitions to the HALT mode (subsystem clock operation) if the P137 input is at high level. |

| Arguments       | None                                                                                                                                                                                                                       |

| Remarks         | None                                                                                                                                                                                                                       |

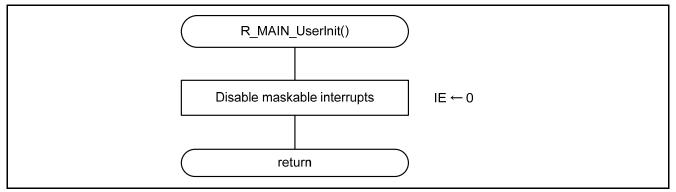

| [Function Name] | R_MAIN_UserInit                                                         |

|-----------------|-------------------------------------------------------------------------|

| Outline         | Main initial setting                                                    |

| Header          | r_cg_macrodriver.h、r_cg_cgc.h、r_cg_port.h、r_cg_intp.h、r_cg_userdefine.h |

| Declaration     | void R_MAIN_UserInit(void);                                             |

| Description     | Disables interrupt processing by the DI instruction.                    |

| Arguments       | None                                                                    |

| Remarks         | None                                                                    |

#### 5.5 Flowcharts

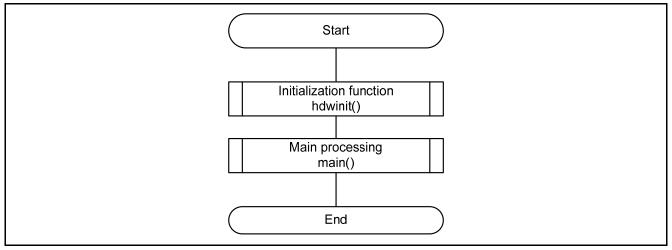

Figure 5.1 shows an overall from of the sample code.

Figure 5.1 Overall Flow

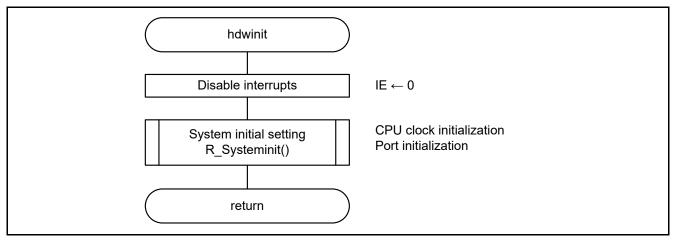

#### 5.5.1 Initialization Function

Figure 5.2 shows the flowchart for the initialization function.

Figure 5.2 Initialization Function

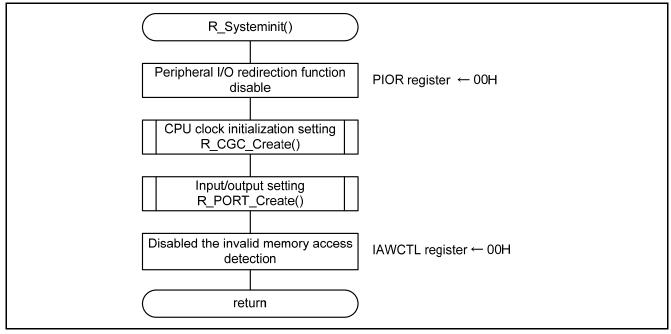

#### 5.5.2 System initial Setting

Figure 5.3 shows the flowchart for the system initial setting.

Figure 5.3 System Initial Setting

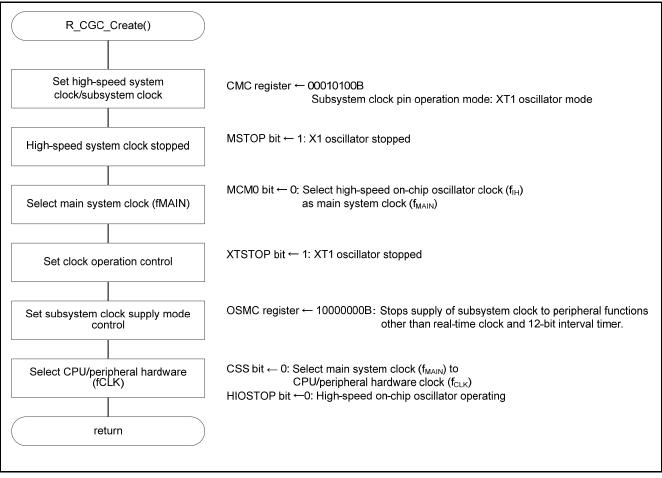

### 5.5.3 CPU Initial Setting

Figure 5.4 shows the flowchart for the CPU initial setting.

Figure 5.4 CPU Initial Setting

#### Clock operation mode setting

Clock operation mode control register (CMC)

High-speed system clock pin operation mode: input port mode

Subsystem clock pin operation mode: XT1 oscillation mode

Symbol: CMC

| 7     | 6      | 5      | 4       | 3 | 2      | 1      | 0    |

|-------|--------|--------|---------|---|--------|--------|------|

| EXCLK | OSCSEL | EXCLKS | OSCSELS | 0 | AMPHS1 | AMPHS0 | AMPH |

| 0     | 0      | 0      | 1       | 0 | 1      | 0      | 0    |

Bits 7-6

| EXCLK | OSCSEL | High-seed oscillation clock pin<br>operation mode | X1/P121 Port                         | X2/EXCLK/P122 Port   |  |

|-------|--------|---------------------------------------------------|--------------------------------------|----------------------|--|

| 0     | 0      | Input port mode                                   | Input port                           |                      |  |

| 0     | 1      | X1 oscillation mode                               | Crystal/ceramic resonator connection |                      |  |

| 1     | 0      | Input port mode                                   | Input port                           |                      |  |

| 1     | 1      | External clock input mode                         | Input port                           | External clock input |  |

#### Bits 5-4

| EXCLKS | OSCSELS | Subsystem clock pin operation mode | XT1/P123 Port XT2/EXCLKS/P124 P |                      |  |

|--------|---------|------------------------------------|---------------------------------|----------------------|--|

| 0      | 0       | Input port mode                    | Input port                      |                      |  |

| 0      | 1       | XT1 oscillation mode               | Crystal resonator connection    |                      |  |

| 1      | 0       | Input port mode                    | Input port                      |                      |  |

| 1      | 1       | External clock input mode          | Input port                      | External clock input |  |

#### Bits 2-1

| AMPHS1 | AMPHS0 | XT1 oscillator oscillation mode selection   |

|--------|--------|---------------------------------------------|

| 0      | 0      | Low-power consumption oscillation (default) |

| 0      | 1      | Normal oscillation                          |

| 1      | 0      | Ultra-low power consumption oscillation     |

| 1      | 1      | Setting prohibited                          |

Bit 0

| AMPH | Control of X1 clock oscillation frequency |

|------|-------------------------------------------|

| 0    | $1MHz \le f_X \le 10MHz$                  |

| 1    | $10MHz < f_X \le 20MHz$                   |

#### Operation control of clocks

Clock operation status control register (CSC) High-speed system clock operation control: X1 oscillator stopped Subsystem clock operation control: XT1 oscillator stopped HOCO clock operation control: HOCO operating

Symbol: CSC

| 7     | 6      | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|--------|---|---|---|---|---|---------|

| MSTOP | XTSTOP | 0 | 0 | 0 | 0 | 0 | HIOSTOP |

| 1     | 1      | 0 | 0 | 0 | 0 | 0 | 0       |

Bit 7

| MOTOD | High-                   | speed system clock operatior             | n control       |

|-------|-------------------------|------------------------------------------|-----------------|

| MSTOP | X1 oscillation mode     | External clock input mode                | Input port mode |

| 0     | X1 oscillator operating | External clock from EXCLK pin is valid   |                 |

| 1     | X1 oscillator stopped   | External clock from EXCLK pin is invalid | Input port      |

Bit 6

| XTSTOP | Subsystem clock operation control |                                              |                 |  |  |  |  |

|--------|-----------------------------------|----------------------------------------------|-----------------|--|--|--|--|

|        | XT1 oscillation mode              | External clock input mode                    | Input port mode |  |  |  |  |

| 0      | XT1 oscillator operating          | External clock from<br>EXCLKS pin is valid   | Level and       |  |  |  |  |

| 1      | XT1 oscillator<br>stopped         | External clock from<br>EXCLKS pin is invalid | Input port      |  |  |  |  |

Bit 0

| HIOSTOP | High-speed on-chip oscillator clock operation control |  |  |  |  |

|---------|-------------------------------------------------------|--|--|--|--|

| 0       | 0 High-speed on-chip oscillator operating             |  |  |  |  |

| 1       | High-speed on-chip oscillator stopped                 |  |  |  |  |

#### Subsystem clock supply mode control

Subsystem clock supply mode control register (OSMC)

Setting in STOP mode or in HALT mode while subsystem clock is selected as CPU clock: disable subsystem clock supply to peripheral functions

#### Symbol: OSMC

| 7      | 6 | 5 | 4            | 3 | 2 | 1 | 0 |

|--------|---|---|--------------|---|---|---|---|

| RTCLPC | 0 | 0 | WUTMM<br>CK0 | 0 | 0 | 0 | 0 |

| 1      | 0 | 0 | 0            | 0 | 0 | 0 | 0 |

Bit 7

| RTCLPC | Setting in STOP mode or in HALT mode while subsystem clock is selected as CPU clock              |  |  |  |

|--------|--------------------------------------------------------------------------------------------------|--|--|--|

| 0      | Enables supply of subsystem clock to peripheral functions                                        |  |  |  |

| 1      | supply of subsystem clock to peripheral functions other than ne clock and 12-bit interval timer. |  |  |  |

$CPU/peripheral\ hardware\ clock\ (f_{CLK})\ setting$

• System clock control register (CKC) Status of fcLк: main system clock Selection of fcLк: high-speed on-chip oscillator clock (fін) Symbol: CKC

| 7   | 6   | 5   | 4    | 3 | 2 | 1 | 0 |

|-----|-----|-----|------|---|---|---|---|

| CLS | CSS | MCS | MCM0 | 0 | 0 | 0 | 0 |

| 0   | 0   | 0   | 0    | 0 | 0 | 0 | 0 |

Bit 6

| CSS | Selection of CPU/peripheral hardware clock (fclk) |  |

|-----|---------------------------------------------------|--|

| 0   | Main system clock (f <sub>MAIN</sub> )            |  |

| 1   | Subsystem clock $(f_{S \cup B})$                  |  |

Bit 4

| MCM0 | Main system clock (f <sub>MAIN</sub> ) operation control                  |  |

|------|---------------------------------------------------------------------------|--|

| 0    | Selects HOCO clock ( $f_{IH}$ ) as main system clock ( $f_{MAIN}$ )       |  |

| 1    | Selects high-speed system clock (f_{MX}) as main system clock (f_{MAIN}). |  |

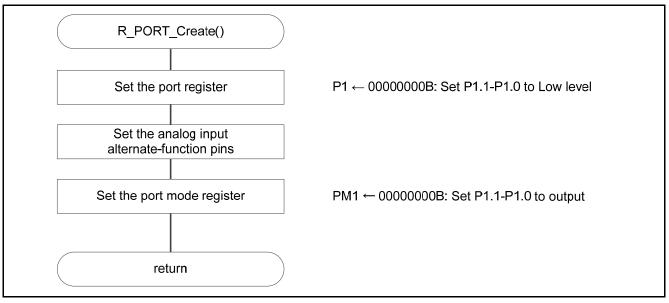

### 5.5.4 Input/Output Port Settings

Figure 5.5 shows the flowchart for the input/output port settings.

Figure 5.5 Input/Output Port Settings

- Note: Refer to the initialization flowchart in the RL78/G13 Initialization (R01AN2575J) Application Note for details on how to set unused ports.

- Caution: When designing circuits, always make sure unused ports are properly processed and all electrical characteristics are met. Also make sure each unused input-only port is connected to  $V_{DD}$  or  $V_{SS}$  through a resister.

### 5.5.5 Main Processing

Figure 5.6 shows the flowchart for the main processing.

Figure 5.6 Main Processing

### 5.5.6 Main Initializes Settings

Figure 5.7 shows the flowchart for the main initializes settings.

Figure 5.7 Main Initializes Settings

#### 6. Sample Code

Sample code can be downloaded from the Renesas Electronics website.

#### 7. Reference Documents

RL78/G13 User's Manual: Hardware (R01UH0146E) RL78 Family User's Manual: Software (R01US0015E) The latest versions can be downloaded from the Renesas Electronics website.

Technical Update/Technical News The latest information can downloaded from the Renesas Electronics website.

### Website and Support

Renesas Electronics website <u>http://www.renesas.com</u>

Inquiries http://www.renesas.com/contact/

All trademarks and registered trademarks are the property of their respective owners.

## **Revision History**

|      |               | Description |                      |

|------|---------------|-------------|----------------------|

| Rev. | Date          | Page        | Summary              |

| 1.00 | Sep. 28, 2018 | _           | First edition issued |

|      |               |             |                      |

#### General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Handling of Unused Pins

Handle unused pins in accordance with the directions given under Handling of Unused Pins in the manual.

- <sup>3</sup>⁄<sub>4</sub> The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- <sup>3</sup>⁄<sub>4</sub> The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- <sup>3</sup>⁄<sub>4</sub> The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

<sup>3</sup>⁄<sub>4</sub> The characteristics of Microprocessing unit or Microcontroller unit products in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.