# RA Family IEC 60730/60335 Self Test Library for RA MCU (RA4\_CM33)

R01AN5901EJ0101 Rev.1.01 May. 31. 2024

#### Introduction

Today, as automatic electronic controls systems continue to expand into many diverse applications, the requirement of reliability and safety are becoming an ever increasing factor in system design.

For example, the introduction of the IEC60730 safety standard for household appliances requires manufactures to design automatic electronic controls that ensure safe and reliable operation of their products.

The IEC60730 standard covers all aspects of product design but Annex H is of key importance for design of Microcontroller based control systems. This provides three software classifications for automatic electronic controls:

- 1. Class A: Control functions, which are not intended to be relied upon for the safety of the equipment. Examples: Room thermostats, humidity controls, lighting controls, timers, and switches.

- 2. Class B: Control functions, which are intended to prevent unsafe operation of the controlled equipment. Examples: Thermal cut-offs and door locks for laundry equipment.

- 3. Class C: Control functions, which are intended to prevent special hazards

Examples: Automatic burner controls and thermal cut-outs for closed.

Appliances such as washing machines, dishwashers, dryers, refrigerators, freezers, and Cookers/Stoves will tend to fall under the classification of Class B.

This Application Note provides guidelines of how to use flexible sample software routines to assist with compliance with IEC60730 class B safety standards. These routines have been certified by VDE Test and Certification Institute GmbH and a copy of the Test Certificate is available in the download package for this Application Note (See Note 1 below).

Although these routines were developed using IEC60730 compliance as a basis, they can be implemented in any system for self testing of Renesas MCUs.

The software routines provided are to be used after reset and also during the program execution. The end user has the flexibility of how to integrate these routines into their overall system design but this document and the accompanying sample code provide an example of how to do this.

It is worth noting that the definition of error handling routines is demanded to the user as well as interrupt handler routines. Since errors that are covered by the software routines are very critical (e.g. PC failure) and the correct SW functionality cannot be assured it is strongly recommended to the user to not only rely on SW error handling, but to also use HW safety mechanisms, e.g. the utilization of the Independent Watchdog (IWDT).

Note 1. This document is based on the European Norm EN60335-1:2002/A1:2004 Annex R, in which the Norm IEC 60730-1 (EN60730-1:2000) is used in some points. The *Annex R* of the mentioned Norm contains just a single sheet that jumps to the IEC 60730-1 for definitions, information and applicable paragraphs.

### **Target**

- Device:

- Renesas RA Family (Arm® Cortex®-M33) \* See next page for series and groups.

- · Development environment (one of the following):

- < RA6M4>

- GNU-GCC ARM Embedded 9.2.1.20191025 / e2 studio 2020-10

- IAR / EWARM Version 8.50.1

- < RA4M3>

- GNU-GCC ARM Embedded 9.2.1.20191025 / e2 studio 2020-10

- IAR / EWARM Version 8.50.9

The term "RA MCU" used in this document refers to the following products.

Table 1. RA MCU Self-Test Function List

| CPU Core      |                                   | Arm® Cortex®-M33                 |        |                                  |            |

|---------------|-----------------------------------|----------------------------------|--------|----------------------------------|------------|

| Series        |                                   | R                                | RA6 RA |                                  | <b>A</b> 4 |

| Group         |                                   | RA6M4<br>RA6M5<br>RA6E2<br>RA6T3 | RA6E1  | RA4M3<br>RA4M2<br>RA4E2<br>RA4T1 | RA4E1      |

|               | CPU                               | 0                                | 0      | 0                                | 0          |

|               | ROM                               | 0                                | 0      | 0                                | 0          |

|               | RAM                               | 0                                | 0      | 0                                | 0          |

| ion           | Clock                             | 0                                | 0      | 0                                | 0          |

| Test Function | Independent Watchdog Timer (IWDT) | 0                                | 0      | 0                                | 0          |

| st Fi         | Voltage                           | 0                                | 0      | 0                                | 0          |

| Tes           | ADC12                             | 0                                | 0      | 0                                | 0          |

|               | Temperature                       | 0                                | -      | 0                                | -          |

|               | Port Output Enable (POE)          | 0                                | 0      | 0                                | 0          |

| GPIO          |                                   | 0                                | 0      | 0                                | 0          |

## Support for Arm® TrustZone®

This self-test library is assumed to be executed in the secure region of Arm® TrustZone®. The operation has been confirmed using a "flat project" by RA Project Generator (PG)\*.

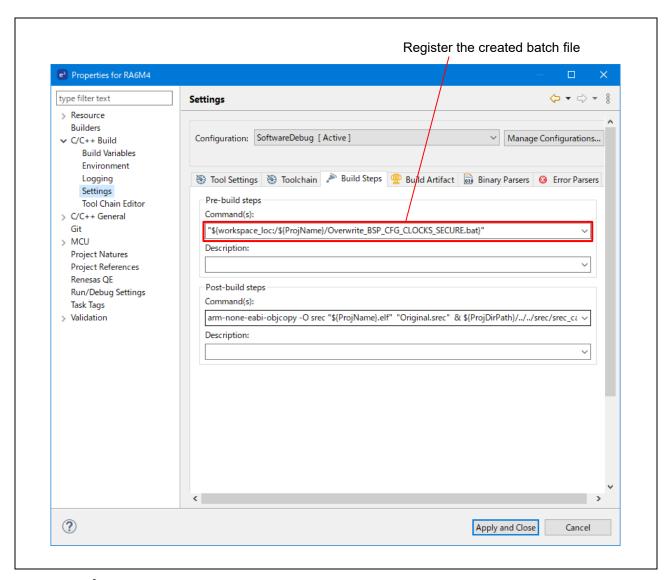

### Precautions Regarding Secure Settings of Clocks (Applicable only to RA6M4)

Immediately after the reset, the clock-related module is set to non-secure mode by FSP (SC (Smart Configurator) when using IAR/EWARM) (bsp\_clock\_cfg.h file in the ra\_cfg folder).

In "Flat Project" (the whole project is a secure area), if the program is executed as it is, an error will occur. Therefore, be sure to switch this setting to secure mode before building the program.

This bsp\_clock\_cfg.h file is overwritten by the FSP or SC and must be modified each time the user presses the Generate Project Contents button. For the specific correction method, refer to "4. Appendix: How to correct the secure settings of clock-related modules".

This support may change in the future depending on the version of FSP and SC.

<sup>\*:</sup> For more information on RA Project Generator, see the RA FSP (Flexible Software Package) documentation.

# **Table of Contents**

| 1. Tests                                         | 5  |

|--------------------------------------------------|----|

| 1.1 CPU                                          | 5  |

| 1.1.1 CPU Software API                           | 7  |

| 1.2 ROM                                          | 16 |

| 1.2.1 CRC32 Algorithm                            | 16 |

| 1.2.2 CRC Software API                           | 16 |

| 1.3 RAM                                          | 20 |

| 1.3.1 RAM Test Algorithms                        | 20 |

| 1.3.2 RAM Software API                           | 22 |

| 1.4 Clock                                        | 32 |

| 1.4.1 Main Clock Frequency Monitoring by CAC     |    |

| 1.4.2 Oscillation Stop Detection of Main Clock   |    |

| 1.5 Independent Watchdog Timer (IWDT)            |    |

| 1.6 Voltage                                      |    |

| 1.7 ADC                                          | 39 |

| 1.8 Temperature                                  | 44 |

| 1.9 Port Output Enable (POE)                     | 47 |

| 1.10 GPIO                                        | 53 |

| 2. Example Usage                                 | 54 |

| 2.1 CPU                                          |    |

| 2.1.1 Power-On                                   |    |

| 2.1.2 Periodic                                   |    |

| 2.2 ROM                                          |    |

| 2.2.1 Reference CRC Value Calculation in Advance |    |

| 2.2.2 Power-On                                   |    |

| 2.2.3 Periodic                                   | 60 |

| 2.3 RAM                                          | 60 |

| 2.3.1 Power-On                                   | 60 |

| 2.3.2 Periodic                                   | 60 |

| 2.4 Clock                                        | 61 |

| 2.5 Independent Watchdog Timer (IWDT)            | 63 |

| 2.6 Voltage                                      | 66 |

| 2.7 ADC                                          | 66 |

| 2.7.1 Power-On                                   | 66 |

| 2.7.2 Periodic                                   | 66 |

| 2.8 Temperature                                  | 67 |

| 2.8.1 Power-On                                   | 67 |

| 2.8.2 Periodic                                   | 67 |

| 2.9 Port Output Enable (POE)                                            | 67             |

|-------------------------------------------------------------------------|----------------|

| 2.9.1 Settings of I/O Port                                              | 68             |

| 2.9.2 Settings of Interrupt                                             | 68             |

| 2.10 GPIO                                                               | 70             |

| 3. Benchmarking                                                         | 71             |

| 3.1 RA6M4 Measurement Results                                           | 71             |

| 3.1.1 CPU                                                               | 72             |

| 3.1.2 ROM                                                               | 72             |

| 3.1.3 RAM                                                               | 72             |

| 4. Appendix: How to Correct the Secure Settings of Clock-Related Module | es (Applicable |

| only to RA6M4)                                                          | 75             |

| 4.1 For e <sup>2</sup> studio + GNU-GCC                                 | 75             |

| 4.2 For IAR/EWARM                                                       | 76             |

| Website and Support                                                     | 77             |

| Revision History                                                        | 78             |

#### 1. Tests

#### 1.1 CPU

This section describes CPU tests routines. (Reference: *IEC 60730: 1999+A1:2003 Annex H - Table H.11.12.1 CPU*) This software tests the following CPU registers.

Table 1.1 List of Registers to Be Tested

|             | CPU Core                          | Arm® Cor                 | tex®-M33              |  |

|-------------|-----------------------------------|--------------------------|-----------------------|--|

|             | Group                             | RA6M4                    | RA4M3                 |  |

|             |                                   | RA6M5                    | RA4M2                 |  |

|             |                                   | RA6E2                    | RA4E2                 |  |

|             |                                   | RA6T3                    | RA4T1                 |  |

|             |                                   | RA6E1                    | RA4E1                 |  |

|             | General-purpose Register          | R0-l                     | R12                   |  |

|             | Control Register                  | MSP_S, N                 | MSP_NS,               |  |

|             |                                   | PSP_S, F                 | PSP_S, PSP_NS,        |  |

|             |                                   | LF                       | LR,                   |  |

| р           |                                   | xPSR (APSR, IPSR, EPSR), |                       |  |

| Tested      |                                   | PRIMASK_S, PRIMASK_NS,   |                       |  |

|             |                                   | CONTROL_S, (             | CONTROL_NS,           |  |

| pe          |                                   | FAULTM                   |                       |  |

| r to        |                                   | FAULTM                   |                       |  |

| ste         |                                   | BASEPRI_S, I             |                       |  |

| Register to |                                   | MSPLIM_S, N              | MSPLIM_NS,            |  |

| 2           |                                   | PSPLIM_S,                | PSPLIM_NS             |  |

|             | Program Counter                   | P                        | C                     |  |

|             | FPU Extension Register (S0 - S31) | S0-                      | S31                   |  |

|             | FPU Control Register (*1)         | ·                        | CCR, FPCAR,<br>FPDSCR |  |

<sup>\*1:</sup> Even if the register names are the same, the bit field configuration may differ depending on the device.

The source file cpu\_test.c provides implementation of the CPU test using C language and relies on assembly language function to access the registers (that is, CPU\_Test\_Control). File cpu\_test\_coupling.c is also required to use the coupling test version of the General Purpose Registers. Coupling test relies on assembly language functions:

- TestGPRsCouplingStart\_A

- TestGPRsCouplingR1\_R3\_A

- TestGPRsCouplingR4\_R6\_A

- TestGPRsCouplingR7\_R9\_A

- TestGPRsCouplingR10 R12 A

- TestGPRsCouplingR0\_A

- TestGPRsCouplingStart\_B

- TestGPRsCouplingR1\_R3\_B

- TestGPRsCouplingR4\_R6\_B

- TestGPRsCouplingR7 R9 B

- TestGPRsCouplingR10\_R12\_B

- TestGPRsCouplingR0\_B

- TestGPRsCouplingEnd

Alternatively, CPU\_Test\_General\_Low, CPU\_Test\_General\_High assembly language functions are used to test General-purpose registers.

The cpu\_test.c source file relies also on FPU\_Control assembly language function to access the FPU control registers. File fpu\_test\_coupling.c is also required if using the coupling test version of the FPU extension registers.

- TestFPUCouplingStart\_A

- TestFPUCouplingS0\_S3\_A

- TestFPUCouplingS4\_S7\_A

- TestFPUCouplingS8\_S11\_A

- TestFPUCouplingS12\_S15\_A

- TestFPUCouplingS16 S19 A

- TestFPUCouplingS20\_S23\_A

- TestFPUCouplingS24\_S27\_A

- TestFPUCouplingS28\_S31\_A

- TestFPUCouplingStart\_B

- TestFPUCouplingS0\_S3\_B

- TestFPUCouplingS4 S7 B

- TestFPUCouplingS8\_S11\_B

- TestFPUCouplingS12\_S15\_B

- TestFPUCouplingS16\_S19\_B

- TestFPUCouplingS20\_S23\_B

- TestFPUCouplingS24\_S27\_BTestFPUCouplingS28 S31 B

- TestFPUCouplingEnd

Alternatively, FPU Exten assembly language function is used to test FPU extension registers.

The header file cpu test.h header file provides the interface to the CPU tests.

These tests are testing such fundamental aspects of the CPU operation; the API functions do not have return values to indicate the result of a test. Instead the user of these tests must create an error handling function with the following declaration:

extern void CPU\_Test\_ErrorHandler(void);

The CPU test will jump to this function if an error is detected. This function must not return.

All the test functions follow the rules of register preservation following a C function call. Therefore the user can call these functions like any normal C function without any additional responsibilities for saving register values beforehand.

## 1.1.1 CPU Software API

| Table 1.2 Software API Source Files |

|-------------------------------------|

| File Name                           |

| cpu_test.h                          |

| fpu_test.h                          |

| cpu_test.c                          |

| cpu_test_coupling.c                 |

| fpu_test_coupling.c                 |

| TestGPRsCouplingStart_A.asm         |

| TestGPRsCouplingR0_A.asm            |

| TestGPRsCouplingR1_R3_A.asm         |

| TestGPRsCouplingR4_R6_A.asm         |

| TestGPRsCouplingR7_R9_A.asm         |

| TestGPRsCouplingR10_R12_A.asm       |

| TestGPRsCouplingStart_B.asm         |

| TestGPRsCouplingR0_B.asm            |

| TestGPRsCouplingR1_R3_B.asm         |

| TestGPRsCouplingR4_R6_B.asm         |

| TestGPRsCouplingR7_R9_B.asm         |

| TestGPRsCouplingR10_R12_B.asm       |

| TestGPRsCouplingEnd.asm             |

| CPU_Test_Control.asm                |

| CPU_Test_General_Low.asm            |

| CPU_Test_General_High.asm           |

| fpu_control.asm                     |

| fpu_exten.asm                       |

| TestFPUCouplingStart_A.asm          |

| TestFPUCouplingS0_S3_A.asm          |

| TestFPUCouplingS4_S7_A.asm          |

| TestFPUCouplingS8_S11_A.asm         |

| TestFPUCouplingS12_S15_A.asm        |

| TestFPUCouplingS16_S19_A.asm        |

| TestFPUCouplingS20_S23_A.asm        |

| TestFPUCouplingS24_S27_A.asm        |

| TestFPUCouplingS28_S31_A.asm        |

| TestFPUCouplingStart_B.asm          |

| TestFPUCouplingS0_S3_B.asm          |

| TestFPUCouplingS4_S7_B.asm          |

| TestFPUCouplingS8_S11_B.asm         |

| TestFPUCouplingS12_S15_B.asm        |

| TestFPUCouplingS16_S19_B.asm        |

| TestFPUCouplingS20_S23_B.asm        |

| TestFPUCouplingS24_S27_B.asm        |

| TestFPUCouplingS28_S31_B.asm        |

TestFPUCouplingEnd.asm

■ cpu test.c File

#### **Syntax**

void CPU\_Test\_All(void)

#### **Description**

Runs through all the tests detailed below in the following order:

1. If using Coupling General Purpose Registers tests (\*1. see below):

2. If not using Coupling General Purpose Registers test:

- CPU\_Test\_Control

- 4. CPU\_Test\_PC

- 5. If using Coupling FPU extension registers tests (\*2. see below):

```

FPU_Test_FPUCouplingPartA

FPU_Test_FPUCouplingPartB

```

6. If not using Coupling FPU extension registers test:

```

FPU_Exten

```

7. FPU\_Control

It is the calling function's responsibility to ensure that the processor is in Privileged Mode. If this function is called in unprivileged mode, the test will fail as some of the register bits are not accessible in unprivileged mode.

The CPU\_Test\_Control function tests the stack pointer registers (MSP and PSP), so monitoring of the stack pointer by the MSPLIM and PSPLIM registers is temporarily disabled during the test.

It is the calling function's responsibility to ensure no interrupts occur during this test.

If an error is detected then external function CPU\_Test\_ErrorHandler will be called.

See the individual tests for a full description.

- \*1. A #define USE\_TEST\_GPRS\_COUPLING in the code is used to select which functions will be used to test the General Purpose Registers.

- \*2. A #define USE\_TEST\_FPU\_COUPLING in the code is used to select which functions will be used to test the FPU extension registers.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### **Syntax**

void CPU\_Test\_PC(void)

#### **Description**

This function tests the Program Counter (PC) register.

This provides a confidence check that the PC is working.

It tests that the PC is working by calling a function that is located in its own section so that it can be located away from this function, so that when it is called more of the PC Register bits are required for it to work.

So that this function can be sure that the function has actually been executed it returns the inverse of the supplied parameter. This return value is checked for correctness.

If an error is detected then external function CPU\_Test\_ErrorHandler will be called.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### ■ CPU\_Test\_General\_Low.asm File

#### **Syntax**

void CPU\_Test\_General\_Low(void)

#### Description

Tests general-purpose registers R0, R1, R2, R3, R4, R5, R6 and R7. Registers are tested in pairs.

For each pair of registers:

- 8. Write h'55555555 to both.

- 9. Read both and check they are equal.

- 10. Write h'AAAAAAA to both.

- 11. Read both and check they are equal.

It is the calling function's responsibility to disable exception during this test.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### ■ CPU Test General High.asm File

### **Syntax**

void CPU\_Test\_General\_High(void)

### **Description**

Tests general-purpose registers R8, R9, R10, R11 and R12. These are the general purpose registers. Registers are tested in pairs.

For each pair of registers:

- 1. Write h'55555555 to both.

- 2. Read both and check they are equal.

- 3. Write h'AAAAAAA to both.

- 4. Read both and check they are equal.

It is the calling function's responsibility to disable exceptions during this test.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### ■ CPU Test Control.asm File

#### **Syntax**

void CPU\_Test\_Control(void)

#### Description

Tests control registers (Refer to "Table 1.1 List of Registers to Be Tested" because it depends on the device).

This test assumes registers R1 to R4 are working.

Generally the test procedure for each register is as follows.

For each register:

- 1. Write h'5555555 to.

- 2. Read back and check value equals h'55555555.

- 3. Write h'AAAAAAA to.

- 4. Read back and check value equals h'AAAAAAA.

Note however that there are some cases where restrictions on specific bits within a register do not allow this procedure. For these cases other test values have been chosen.

It is the calling function's responsibility to ensure that the processor is in Privileged Mode. If this function is called in Unprivileged Mode the test will fail as some of the register bits are not accessible in Unprivileged Mode. It is also the calling function's responsibility to disable exceptions during this test.

Note: FAULTMASK and PRIMASK are not tested since this test requires exceptions be disabled. Thus they are not activated during the test modifying FAULTMASK and PRIMASK.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### ■ cpu test coupling.c File

| c. |       |  |

|----|-------|--|

| 3) | /ntax |  |

void CPU\_Test\_GPRsCouplingPartA(void)

### Description

Tests general-purpose registers R0 to R12. Coupling faults between the registers are detected.

The general-purpose register test consists of Part A and Part B, and this function is Part A.

It is the calling function's responsibility to ensure no interrupts occur during this test.

If an error is detected then external function CPU Test ErrorHandler will be called.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

#### **Syntax**

void CPU\_Test\_GPRsCouplingPartB(void)

#### **Description**

Tests general-purpose registers R0 to R12. Coupling faults between the registers are detected.

The general-purpose register test consists of Part A and Part B, and this function is Part B.

It is the calling function's responsibility to ensure no interrupts occur during this test.

| Input Parameters  |     |

|-------------------|-----|

| NONE              | N/A |

| Output Parameters |     |

| NONE              | N/A |

| Return Values     |     |

| NONE              | N/A |

### ■ fpu test coupling.c File

| c. |       |  |

|----|-------|--|

| 3) | /ntax |  |

void FPU\_Test\_FPUCouplingPartA (void)

### **Description**

Tests FPU extension registers S0 to S31. Coupling faults between the registers are detected.

The FPU extension registers test consists of Part A and Part B, and this function is Part A.

It is the calling function's responsibility to ensure no interrupts occur during this test.

If an error is detected then external function CPU\_Test\_ErrorHandler will be called.

| Input Parameters  |     |

|-------------------|-----|

| NONE              | N/A |

| Output Parameters |     |

| NONE              | N/A |

| Return Values     |     |

| NONE              | N/A |

### **Syntax**

void FPU\_Test\_FPUCouplingPartB(void)

#### Description

Tests FPU extension registers S0 to S31. Coupling faults between the registers are detected.

The FPU extension registers test consists of Part A and Part B, and this function is Part B.

It is the calling function's responsibility to ensure no interrupts occur during this test.

| Input Parameters  |     |

|-------------------|-----|

| NONE              | N/A |

| Output Parameters |     |

| NONE              | N/A |

| Return Values     |     |

| NONE              | N/A |

### ■ fpu exten.asm File

| c. |       |  |

|----|-------|--|

| 3) | /ntax |  |

void FPU\_Exten(void)

### Description

Test FPU extension registers S0 to S31. Registers are tested in pairs.

For each pair of registers:

- 1. Write h'55555555 to both.

- 2. Read both and check they are equal.

- 3. Write h'AAAAAAA to both.

- 4. Read both and check they are equal.

It is the calling function's responsibility to disable exception during this test.

| Input Parameters  |     |

|-------------------|-----|

| NONE              | N/A |

| Output Parameters |     |

| NONE              | N/A |

| Return Values     |     |

| NONE              | N/A |

### ■ fpu control.asm File

#### **Syntax**

void FPU\_Control(void)

### **Description**

Tests FPU control registers (Refer to "Table 1.1 List of Registers to Be Tested" because it depends on the device). This test assumes registers R1 to R10 are working.

Generally the test procedure for each register is as follows.

For each register:

- 5. Write h'55555555 to.

- 6. Read back and check value equals h'55555555.

- 7. Write h'AAAAAAA to.

- 8. Read back and check value equals h'AAAAAAA.

Note however that there are some cases where restrictions on specific bits within a register do not allow this procedure. For these cases other test values have been chosen.

It is the calling function's responsibility to ensure that the processor is in Privileged Mode. If this function is called in Unprivileged Mode the test will fail as some of the register bits are not accessible in Unprivileged Mode. It is also the calling function's responsibility to disable exceptions during this test.

| Input Parameters  |     |

|-------------------|-----|

| NONE              | N/A |

| Output Parameters |     |

| NONE              | N/A |

| Return Values     |     |

| NONE              | N/A |

#### 1.2 **ROM**

This section describes the ROM/Flash memory test using CRC routines. (Reference: *IEC 60730: 1999+A1:2003 Annex H - H2.19.4.1 CRC - Single Word*)

CRC is a fault/error control technique which generates a single word or checksum to represent the contents of memory. A CRC checksum is the remainder of a binary division with no bit carry (XOR used instead of subtraction) of the message bit stream, by a predefined (short) bit stream of length n + 1. which represents the coefficients of a polynomial with degree n. Before the division, n zeros are appended to the message stream. CRCs are often used because they are simple to implement in binary hardware and are easy to analyze mathematically.

The ROM test can be achieved by generating a CRC value for the contents of the ROM and saving it.

During the memory self-test, the same CRC algorithm is used to generate another CRC value, which is compared with the saved CRC value. The technique recognizes all one-bit errors and a high percentage of multi-bit errors.

The complicated part of using CRCs is if you need to generate a CRC value that will then be compared with other CRC values produced by other CRC generators. This proves difficult because there are a number of factors that can change the resulting CRC value even if the basic CRC algorithm is the same. This includes the combination of the order that the data is supplied to the algorithm, the assumed bit order in any look-up table used and the required order of the bits of the actual CRC value. This complication has arisen because big- and little-endian systems were developed to work together that employed serial data transfers where bit order became important. Also, some debuggers implement a software break on ROM, in which case the contents of ROM may be rewritten during debugging.

The method of calculating the reference CRC value depends on the toolchain used. For the detailed procedure, refer to Section 2.2 ROM in 2.Example Usage

### 1.2.1 CRC32 Algorithm

The RA MCU includes a CRC module that includes support for the CRC32. This software set the CRC module to produce a 32-bit CRC32.

- Polynomial =  $0x04C11DB7 (x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1)$

- Width = 32 bits

- Initial value = 0xFFFFFFFF

- XOR with h'FFFFFFF is performed on the output CRC

#### 1.2.2 CRC Software API

The functions in the reminder of this section are used to calculate a CRC value and verify its correctness against a value stored in ROM.

All software is written in ANSI C. The renesas.h header file includes definition of RA MCU registers.

**Table 1.3 CRC Software API Source Files**

| File Name    |

|--------------|

| crc.h        |

| crc_verify.h |

| crc.c        |

| CRC_Verify.c |

## ■ CRC\_Verify.c File

| Syntax                                                                                                          |                                                     |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| bool_t CRC_Verify(const uint32_t ui32_NewCRCValue, const uint32_t ui32_AddrRefCRC)                              |                                                     |

| Description                                                                                                     |                                                     |

| This function compares a new CRC value with a reference CRC by supplying address where reference CRC is stored. |                                                     |

| Input Parameters                                                                                                |                                                     |

| const uint32_t<br>ui32_NewCRCValue                                                                              | Value of calculated new CRC value.                  |

| const uint32_t<br>ui32_AddrRefCRC                                                                               | Address where 32 bit reference CRC value is stored. |

| Output Parameters                                                                                               |                                                     |

| NONE                                                                                                            | N/A                                                 |

| Return Values                                                                                                   |                                                     |

| bool_t                                                                                                          | True = Passed, False = Failed                       |

### ■ crc.c File

| Syntax                         |                                                                                                        |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| <pre>void CRC_Init(void)</pre> | void CRC_Init(void)                                                                                    |  |  |

| Description                    |                                                                                                        |  |  |

| Initializes the CRC module. T  | Initializes the CRC module. This function must be called before any of the other CRC functions can be. |  |  |

| Input Parameters               |                                                                                                        |  |  |

| NONE                           | N/A                                                                                                    |  |  |

| Output Parameters              |                                                                                                        |  |  |

| NONE                           | N/A                                                                                                    |  |  |

| Return Values                  |                                                                                                        |  |  |

| NONE                           | N/A                                                                                                    |  |  |

| Syntax                                                                   |                                          |  |

|--------------------------------------------------------------------------|------------------------------------------|--|

| uint32_t CRC_Calculate(const uint32_t* pui32_Data, uint32_t ui32_Length) |                                          |  |

| Description                                                              |                                          |  |

| This function calculates the CRC of a single specified memory area.      |                                          |  |

| Input Parameters                                                         |                                          |  |

| const uint32_t*<br>pui32_Data                                            | Pointer to start of memory to be tested. |  |

| uint32_t ui32_Length                                                     | Length of the data in long words.        |  |

| Output Parameters                                                        |                                          |  |

| NONE                                                                     | N/A                                      |  |

| Return Values                                                            |                                          |  |

| Uint32_t                                                                 | The 32-bit calculated CRC32 value.       |  |

The following functions are used when the memory area cannot simply be specified by a start address and length. They provide a way of adding memory areas in ranges/sections. This can also be used if function CRC\_Calculate takes too long in a single function call.

### ■ crc.c File

| Syntax                           |                                                                          |  |

|----------------------------------|--------------------------------------------------------------------------|--|

| void CRC_Start(void)             |                                                                          |  |

| Description                      |                                                                          |  |

| Prepares the module for starting | ng to receive data. Call this once prior to using function CRC_AddRange. |  |

| Input Parameters                 |                                                                          |  |

| NONE                             | N/A                                                                      |  |

| Output Parameters                |                                                                          |  |

| NONE                             | N/A                                                                      |  |

| Return Values                    |                                                                          |  |

| NONE                             | N/A                                                                      |  |

### **Syntax**

### Description

Use this function rather than CRC\_Calculate to calculate the CRC on data made up of more than one address range. Call CRC\_Start first then CRC\_AddRange for each address range required and then call CRC\_Result to get the CRC value.

| Input Parameters              |                                                |  |

|-------------------------------|------------------------------------------------|--|

| const uint32_t*<br>pui32_Data | Pointer to start of memory range to be tested. |  |

| uint32_t ui32_Length          | Length of the data in long words.              |  |

| Output Parameters             |                                                |  |

| NONE                          | N/A                                            |  |

| Return Values                 |                                                |  |

| NONE                          | N/A                                            |  |

### **Syntax**

uint32\_t CRC\_Result(void)

#### Description

Calculates the CRC value for all the memory ranges added using function CRC\_AddRange since CRC\_Start was called.

| Input Parameters  |                             |  |

|-------------------|-----------------------------|--|

| NONE              | N/A                         |  |

| Output Parameters |                             |  |

| NONE              | N/A                         |  |

| Return Values     |                             |  |

| uint32_t          | The calculated CRC32 value. |  |

RENESAS

#### 1.3 **RAM**

March tests are a family of tests that are well recognized as an effective way of testing RAM.

A March test consists of a finite sequence of March elements. A March element is a finite sequence of operations applied to every cell in the memory array before proceeding to the next cell.

In general, the more March elements the algorithm consists of, the better its fault coverage will be but at the expense of a slower execution time.

The algorithms themselves are destructive (they do not preserve the current RAM values) but the supplied test functions provide a non-destructive option so that memory contents can be preserved. This is achieved by copying the memory to a supplied buffer before running the actual algorithm and then restoring the memory from the buffer at the end of the test. The API includes an option for automatically testing the buffer as well as the RAM test area.

The area of RAM being tested cannot be used for anything else while it is being tested. This makes the testing of RAM used for the stack particularly difficult. To help with this problem the API includes functions which can be used for testing the stack.

The following section introduces the specific March Tests. Following that is the specification of the software APIs.

### 1.3.1 RAM Test Algorithms

### (1) March C

The March C algorithm (van de Goor 1991) consists of 6 March elements with a total of 10 operations. It detects the following faults.

- 1. Stuck-At Faults (SAF)

- The logic value of a cell or a line is always 0 or 1.

- 2. Transition Faults (TF)

- A cell or a line that fails to undergo a  $0\rightarrow 1$  or a  $1\rightarrow 0$  transition.

- 3. Coupling Faults (CF)

- A write operation to one cell changes the content of a second cell.

- 4. Address Decoder Faults (AF)

Any fault that affects the address decoder.

- With a certain address, no cell will be accessed.

- A certain cell is never accessed.

- With a certain address, multiple cells are accessed simultaneously.

- A certain cell can be accessed by multiple addresses.

These are the 6 March elements.

- 1. Write all zeros to array.

- 2. Starting at lowest address, read zeros, write ones, increment up array bit by bit.

- 3. Starting at lowest address, read ones, write zeros, increment up array bit by bit.

- 4. Starting at highest address, read zeros, write ones, decrement down array bit by bit.

- 5. Starting at highest address, read ones, write zeros, decrement down array bit by bit.

- 6. Read all zeros from array.

### (2) March X

Note: This algorithm has not been implemented for the RA MCU and is only presented here for information as it relates to the March X WOM version below.

The March X algorithm consists of 4 March elements with a total of 6 operations. It detects the following faults.

- 1. Stuck-At Faults (SAF)

- 2. Transition Faults (TF)

- 3. Inversion Coupling Faults (CFin)

- 4. Address Decoder Faults (AF)

These are the 4 March elements.

- 1. Write all zeros to array.

- 2. Starting at lowest address, read zeros, write ones, increment up array bit by bit.

- 3. Starting at highest address, read ones, write zeros, decrement down array bit by bit.

- 4. Read all zeros from array.

### (3) March X (Word-Oriented Memory Version)

The March X Word-Oriented Memory (WOM) algorithm has been created from a standard March X algorithm in two stages. First, the standard March X is converted from using a single-bit data pattern to using a data pattern equal to the memory access width. At this stage the test is primarily detecting inter-word faults including Address Decoder faults. The second stage is to add an additional two March elements. The first uses a data pattern of alternating high/low bits then the second uses the inverse. The addition of these elements is to detect intra-word coupling faults.

These are the 6 March elements.

- 1. Write all zeros to array.

- 2. Starting at lowest address, read zeros, write ones, increment up array word by word.

- 3. Starting at highest address, read ones, write zeros, decrement down word by word.

- 4. Starting at lowest address, read zeros, write h'AAs, increment up array word by word.

- 5. Starting at highest address, read h'AAs, write h'55s, decrement down word by word.

- 6. Read all h'55s from array.

#### 1.3.2 RAM Software API

Two implementations of the RAM tests are available.

- (a) Standard implementation.

- (b) HW (Hardware) implementation:

This version uses the DOC (Data Operation Circuit) and optionally a DTC (Data Transfer Controller) to help perform the tests.

Both implementations share the same core API but the 'HW' implementation has some additional functions. Please see details in Section 1.3.2 (3).

#### (1) March C API

This test can be configured to use 8-, 16- or 32-bit RAM accesses.

This is achieved by #defining RAMTEST\_MARCH\_C\_ACCESS\_SIZE in the header file to be one of the following.

- RAMTEST\_MARCH\_C\_ACCESS\_SIZE\_8BIT

- 2. RAMTEST\_MARCH\_C\_ACCESS\_SIZE\_16BIT

- RAMTEST\_MARCH\_C\_ACCESS\_SIZE\_32BIT

Sometimes limiting the maximum size of RAM that can be tested with a single function call can speed the test up as well as reducing stack and code size. This is done by limiting the size of the variable used to hold the number of 'words' that the test area contains. The 'word' size is the selected access width.

This is achieved by #defining RAMTEST\_MARCH\_C\_MAX\_WORDS in the header file to be one of the following.

- RAMTEST\_MARCH\_C\_MAX\_WORDS\_8BIT (Max words in test area is 0xFF)

RAMTEST\_MARCH\_C\_MAX\_WORDS\_16BIT (Max words in test area is 0xFFFF)

- 3. RAMTEST\_MARCH\_C\_MAX\_WORDS\_32BIT (Max words in test area is 0xFFFFFFFF)

#### Table 1.4 March C API Source Files

| Implementation | Header Files       | Source Files         |

|----------------|--------------------|----------------------|

| Standard       | ramtest_march_c.h  | ramtest_march_c.c    |

| HW             | ramtest_march_c.h  | ramtest_march_c_HW.c |

|                | ramtest_march_HW.h | ramtest_march_HW.c   |

Select either the standard implementation or the HW implementation fileset for the compiler build target.

The source is written in ANSI C and uses renesas.h header file to access peripheral registers.

Note: The API allows just a single word to be tested with a function call. However, for coupling faults to be tested between words, it is important to use the functions to test a data range bigger than one word.

### ■ ramtest march c.c File

| Syntax                           | Syntax                                                                                                                                                                                                                                     |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| bool_t RamTest_Man               | bool_t RamTest_March_C(const uint32_t ui32_StartAddr,                                                                                                                                                                                      |  |  |

| Description                      |                                                                                                                                                                                                                                            |  |  |

| RAM memory test using            | g March C (Goor 1991) algorithm.                                                                                                                                                                                                           |  |  |

| Input Parameters                 | Input Parameters                                                                                                                                                                                                                           |  |  |

| const uint32_t<br>ui32_StartAddr | The address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                                                                                             |  |  |

| const uint32_t<br>ui32_EndAddr   | The address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr.                                                                            |  |  |

| void* const<br>p_RAMSafe         | For a destructive memory test, set to NULL.  For a non-destructive memory test, set to the start of a buffer that is large enough to copy the contents of the test area into it and that is aligned with the selected memory access width. |  |  |

| Output Parameters                |                                                                                                                                                                                                                                            |  |  |

| NONE                             | N/A                                                                                                                                                                                                                                        |  |  |

| Return Values                    |                                                                                                                                                                                                                                            |  |  |

| bool_t                           | True = Test passed, False = Test or parameter check failed.                                                                                                                                                                                |  |  |

| _   |   |   |   |   |

|-----|---|---|---|---|

| Sv  |   | 1 | _ |   |

| ~ W | n | т | 2 | v |

|     |   |   |   |   |

### **Description**

Non Destructive RAM memory test using March C (Goor 1991) algorithm.

This function differs from the RamTest\_March\_C function by testing the 'RAMSafe' buffer before using it. If the test of the 'RAMSafe' buffer fails then the test will be aborted and the function will return false.

| Input Parameters                 |                                                                                                                                                                 |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| const uint32_t<br>ui32_StartAddr | The address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                  |  |

| const uint32_t<br>ui32_EndAddr   | The address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr. |  |

| void* const<br>p_RAMSafe         | Set to the start of a buffer that is large enough to copy the contents of the test area into it and that is aligned with the selected memory access width.      |  |

| Output Parameters                |                                                                                                                                                                 |  |

| NONE                             | N/A                                                                                                                                                             |  |

| Return Values                    |                                                                                                                                                                 |  |

| bool_t                           | True = Test passed, False = Test or parameter check failed.                                                                                                     |  |

### (2) March X WOM API

This test can be configured to use 8-, 16- or 32-bit RAM accesses.

This is achieved by #defining RAMTEST\_MARCH\_X\_WOM\_ACCESS\_SIZE in the header file to be one of the following.

- RAMTEST\_MARCH\_X\_WOM\_ACCESS\_SIZE\_8BIT

- RAMTEST MARCH X WOM ACCESS SIZE 16BIT

- RAMTEST\_MARCH\_X\_WOM\_ACCESS\_SIZE\_32BIT

In order to speed up the run time of the test you can choose to limit the maximum size of RAM that can be tested with a single function call. This is done by limiting the size of the variable used to hold the number of 'words' that the test area contains. The 'word' size is the same as the selected access width.

This is achieved by #defining RAMTEST MARCH X WOM MAX WORDS in the header file to be one of the following.

| • | RAMTEST_MARCH_X_WOM_MAX_WORDS_8BIT  | (Max words in test area is 0xFF)      |

|---|-------------------------------------|---------------------------------------|

| • | RAMTEST_MARCH_X_WOM_MAX_WORDS_16BIT | (Max words in test area is 0xFFFF)    |

| • | RAMTEST_MARCH_X_WOM_MAX_WORDS_32BIT | (Max words in test area is 0xFFFFFFF) |

#### Table 1.5 March X WOM Source Files

| Implementation | Header Files          | Source Files             |

|----------------|-----------------------|--------------------------|

| Standard       | ramtest_march_x_wom.h | ramtest_march_x_wom.c    |

| HW             | ramtest_march_x_wom.h | ramtest_march_x_wom_HW.c |

|                | ramtest_march_HW.h    | ramtest_march_HW.c       |

Select either the standard implementation or the HW implementation fileset for the compiler build target.

The source is written in ANSI C and uses renesas.h header file to access peripheral registers.

Note: The API allows just a single word to be tested with a function call. However, for coupling faults to be tested between words it is important to use the functions to test a data range bigger than one word.

#### ■ ramtest march x wom.c File

| Syntax                                                            |                                                                                                                                                             |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bool_t RamTest_March_X_WOM(const uint32_t ui32_StartAddr,         |                                                                                                                                                             |  |

| Description                                                       |                                                                                                                                                             |  |

| RAM memory test based on March X algorithm converted for WOM.     |                                                                                                                                                             |  |

| Input Parameters                                                  |                                                                                                                                                             |  |

| const uint32_t<br>ui32_StartAddr                                  | Address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                  |  |

| const uint32_t<br>ui32_EndAddr                                    | Address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr. |  |

| void* const p_RAMSafe For a destructive memory test, set to NULL. |                                                                                                                                                             |  |

| Output Parameters                                                 |                                                                                                                                                             |  |

| NONE                                                              | N/A                                                                                                                                                         |  |

| Return Values                                                     |                                                                                                                                                             |  |

| bool_t                                                            | True = Test passed, False = Test or parameter check failed.                                                                                                 |  |

| Syntax | S١ | /nt | ax |

|--------|----|-----|----|

|--------|----|-----|----|

### Description

Non-Destructive RAM memory test based on March X algorithm converted for WOM.

This function differs from the  $RamTest\_March\_X\_WOM$  function by testing the 'RAMSafe' buffer before using it. If the test of the 'RAMSafe' buffer fails then the test will be aborted and the function will return false.

| Input Parameters                 |                                                                                                                                                                 |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| const uint32_t<br>ui32_StartAddr | The address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                  |  |

| const uint32_t<br>ui32_EndAddr   | The address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr. |  |

| void* const p_RAMSafe            | Set to the start of a buffer that is large enough to copy the contents of the test area into it and that is aligned with the selected memory access width.      |  |

| Output Parameters                |                                                                                                                                                                 |  |

| NONE                             | N/A                                                                                                                                                             |  |

| Return Values                    |                                                                                                                                                                 |  |

| bool_t                           | True = Test passed, False = Test or parameter check failed.                                                                                                     |  |

### (3) March C and March X WOM HW Implementation Specific API.

The 'HW' implementations of the March C and the March X WOM tests use the DOC (Data Operation Circuit) and optionally a DTC to help perform the tests. The DTC is used to initialize the RAM under test and the DOC is used to compare values read back from RAM with expected values.

It is the user's responsibility to ensure that nothing else accesses the DOC or chosen DTC during the RAM tests.

**Table 1.6 HW Implementation Files**

| Test                       | Header Files          | Source Files             |

|----------------------------|-----------------------|--------------------------|

| (1) March C                | ramtest_march_c.h     | ramtest_march_c_HW.c     |

| (2) March X WOM            | ramtest_march_x_wom.h | ramtest_march_x_wom_HW.c |

| HW Initialization (Common) | ramtest_march_HW.h    | ramtest_march_HW.c       |

The optional use of the DTC is controlled using the following #defines.

**Table 1.7 Defining DTC Options**

| File Containing Definitions | #define         | Meaning if #defined    |

|-----------------------------|-----------------|------------------------|

| ramtest_march_HW.h          | RAMTEST_USE_DTC | Initialize and use DTC |

#### ■ ramtest march HW.c File (Initialization)

| _  |   |    |   |

|----|---|----|---|

| S١ | m | ta | X |

void RamTest\_March\_HW\_Init(void)

#### Description

$Initialize \ the \ hardware \ (DOC \ and \ optionally \ DTC) \ used \ by \ the \ 'HW' \ implementations \ of \ the \ RAM \ tests.$

The DTC is only used if RAMTEST\_USE\_DTC is defined.

Call this function before using any other RAM Test function that uses a HW implementation.

| Input Parameters  |     |  |

|-------------------|-----|--|

| NONE              | N/A |  |

| Output Parameters |     |  |

| NONE              | N/A |  |

| Return Values     |     |  |

| NONE              | N/A |  |

### **Syntax**

bool\_t RamTest\_March\_HW\_PreTest(void)

### **Description**

This may be used to check if the hardware (DOC and DTC) are functioning correctly before using. A quick functional test of the DOC and (if RAMTEST\_USE\_DTC is defined) the DTC is performed.

| Input Parameters  |                                          |

|-------------------|------------------------------------------|

| NONE              | N/A                                      |

| Output Parameters |                                          |

| NONE              | N/A                                      |

| Return Values     |                                          |

| bool_t            | True = Test passed, False = Test failed. |

#### **Syntax**

bool\_t RamTest\_March\_HW\_Is\_Init(void)

### **Description**

Checks if RamTest\_March\_HW\_Init has been called.

This is used by specific RAM tests to check that the HW has been initialized before trying to use it. A user does not have to use this function.

| Input Parameters  |                                                             |  |

|-------------------|-------------------------------------------------------------|--|

| NONE              | N/A                                                         |  |

| Output Parameters |                                                             |  |

| NONE              | N/A                                                         |  |

| Return Values     |                                                             |  |

| bool_t            | True = Test passed, False = Test or parameter check failed. |  |

## ■ ramtest\_march\_c\_HW.c File

| Syntax                                                               | Syntax                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>bool_t RamTest_March_C_DTC(const uint32_t ui32_StartAddr,</pre> |                                                                                                                                                                                                                                            |  |  |

| Description                                                          | Description                                                                                                                                                                                                                                |  |  |

| [HW implementations                                                  | [HW implementations version] RAM memory test using March C (Goor 1991) algorithm.                                                                                                                                                          |  |  |

| Input Parameters                                                     |                                                                                                                                                                                                                                            |  |  |

| const uint32_t<br>ui32_StartAddr                                     | The address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                                                                                             |  |  |

| const uint32_t<br>ui32_EndAddr                                       | The address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr.                                                                            |  |  |

| void* const<br>p_RAMSafe                                             | For a destructive memory test, set to NULL.  For a non-destructive memory test, set to the start of a buffer that is large enough to copy the contents of the test area into it and that is aligned with the selected memory access width. |  |  |

| Output Parameters                                                    |                                                                                                                                                                                                                                            |  |  |

| NONE                                                                 | N/A                                                                                                                                                                                                                                        |  |  |

| Return Values                                                        |                                                                                                                                                                                                                                            |  |  |

| bool_t                                                               | True = Test passed, False = Test or parameter check failed.                                                                                                                                                                                |  |  |

### ■ ramtest\_march\_x\_won\_HW.c File

| Syntax                                                                                     |                                                                                                                                                             |  |  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| bool_t RamTest_March_X_WOM_DTC(const uint32_t ui32_StartAddr,                              |                                                                                                                                                             |  |  |

| Description                                                                                | Description                                                                                                                                                 |  |  |

| [HW implementations version] RAM memory test based on March X algorithm converted for WOM. |                                                                                                                                                             |  |  |

| Input Parameters                                                                           |                                                                                                                                                             |  |  |

| const uint32_t<br>ui32_StartAddr                                                           | Address of the first word of RAM to be tested. This must be aligned with the selected memory access width.                                                  |  |  |

| const uint32_t<br>ui32_EndAddr                                                             | Address of the last word of RAM to be tested. This must be aligned with the selected memory access width and be a value greater or equal to ui32_StartAddr. |  |  |

| void* const p_RAMSafe                                                                      | For a destructive memory test, set to NULL.                                                                                                                 |  |  |

| Output Parameters                                                                          |                                                                                                                                                             |  |  |

| NONE                                                                                       | N/A                                                                                                                                                         |  |  |

| Return Values                                                                              |                                                                                                                                                             |  |  |

| bool_t                                                                                     | True = Test passed, False = Test or parameter check failed.                                                                                                 |  |  |

### (4) RAM Test Stack API

This API enables a RAM test to be performed on an area of RAM that includes the stack. As the function that performs the RAM test requires a stack these functions will, re-locate the stack to a supplied new RAM area allowing the original stack area to be tested. Three functions are provided that can be called depending upon which stack (Main or Process) is in the test area or if both are.

It is the calling function's responsibility to ensure that the processor is in Privileged Mode. If this function is called in unprivileged mode the test will fail as some of the register bits are not accessible in unprivileged mode.

Note: The stack testing functions make use of one of the March RAM tests presented previously by passing it in as a function pointer. If using a test that requires initialization before use it is the user's responsibility to ensure this has been done before trying to use the test by calling one of these functions.

Table 1.8 RAM Test Stack API Source Files

| File Name                 |  |  |

|---------------------------|--|--|

| ramtest_stack.h           |  |  |

| ramtest_stack.c           |  |  |

| StartBothTestAssembly.asm |  |  |

| StartMainTestAssembly.asm |  |  |

| StartProcTestAssembly.asm |  |  |

#### ramtest\_stack.c File

| Syntax                          |                          |

|---------------------------------|--------------------------|

| bool_t RamTest_Stack Main(const | uint32 t ui32 StartAddr, |

|                                 | uint32_t ui32_EndAddr,   |

| void*                           | const p_RAMSafe,         |

| const                           | uint32_t ui32_NewMSP,    |

| const                           | TEST_FUNC fpTest_Func)   |

| Description                     |                          |

#### Description

RAM test of an area that includes the Main Stack (but not includes the Process stack).

| Input Parameters                 |                                                                                                                                        |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| const uint32_t<br>ui32_StartAddr | The address of the first word of RAM to be tested. This must be compatible with the requirements of fpTest_Func.                       |

| const uint32_t<br>ui32_EndAddr   | The address of the last word of RAM to be tested. This must be compatible with the requirements of fpTest_Func.                        |

| void* const<br>p_RAMSafe         | Set to the start of a buffer that is the same size as the test RAM area. This must be compatible with the requirements of fpTest_Func. |

| const uint32_t<br>ui32_NewUSP    | New Stack pointer value for the Main stack to be relocated to.                                                                         |

| const TEST_FUNC fpTest_Func      | Function pointer of type TEST_FUNC to the actual memory test to be used.  Typedef bool_t(*TEST_FUNC)( uint32_t, uint32_t, void*);      |

| Tpresc_runc                      | For example, 'RamTest_March_X_WOM'.                                                                                                    |

| Output Parameters                |                                                                                                                                        |

| NONE                             | N/A                                                                                                                                    |

| Return Values                    |                                                                                                                                        |

| bool_t                           | True = Test passed, False = Test or parameter check failed.                                                                            |

### **Syntax**

### **Description**

RAM test of an area that includes the Process stack (but not includes the Main stack).

| Input Parameters                 |                                                                                                                                                                      |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| const uint32_t<br>ui32_StartAddr | The address of the first word of RAM to be tested. This must be compatible with the requirements of the fpTest_Func.                                                 |  |

| const uint32_t<br>ui32_EndAddr   | The address of the last word of RAM to be tested. This must be compatible with the requirements of the fpTest_Func.                                                  |  |

| void* const<br>p_RAMSafe         | Set to the start of a buffer that is the same size as the test RAM area. This must be compatible with the requirements of the fpTest_Func.                           |  |

| const uint32_t<br>ui32_NewPSP    | New Stack pointer value for the Process stack to be relocated to.                                                                                                    |  |

| const fpTest_Func                | Function pointer of type TEST_FUNC to the actual memory test to be used.  Typedef bool_t(*TEST_FUNC)(uint32_t, uint32_t, void*);  For example 'RamTest March X WOM'. |  |

| Output Parameters                |                                                                                                                                                                      |  |

| NONE                             | N/A                                                                                                                                                                  |  |

| Return Values                    |                                                                                                                                                                      |  |

| bool t                           | True = Test passed, False = Test or parameter check failed.                                                                                                          |  |

### **Syntax**

### **Description**

RAM test of an area that includs both the Main stack and the Process stack.

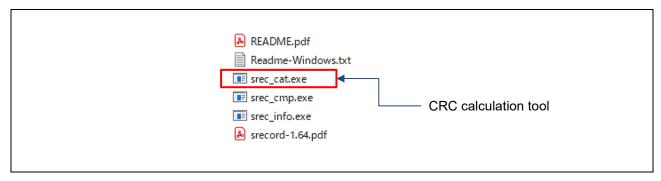

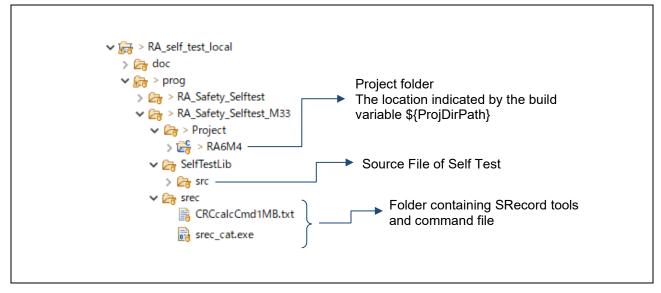

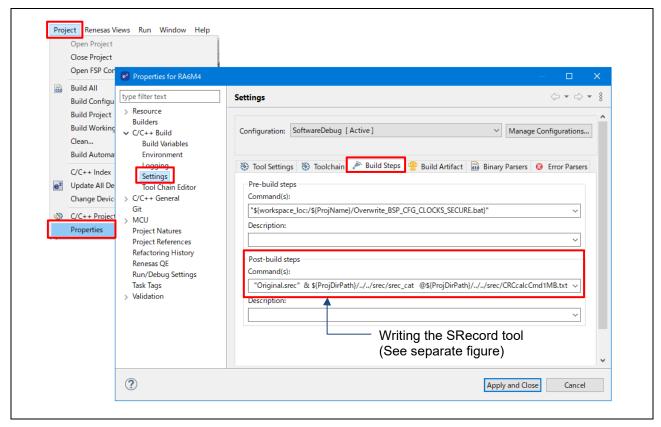

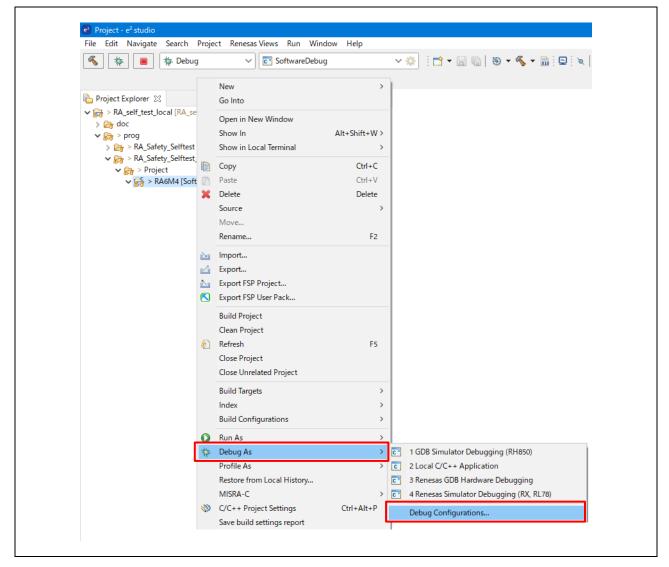

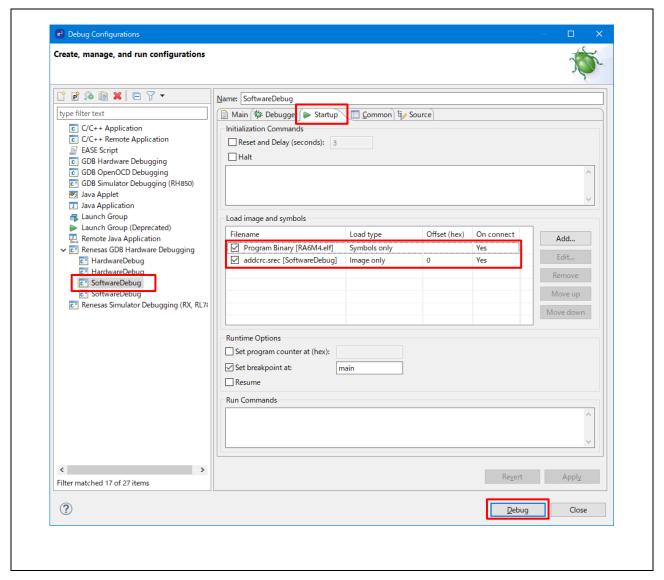

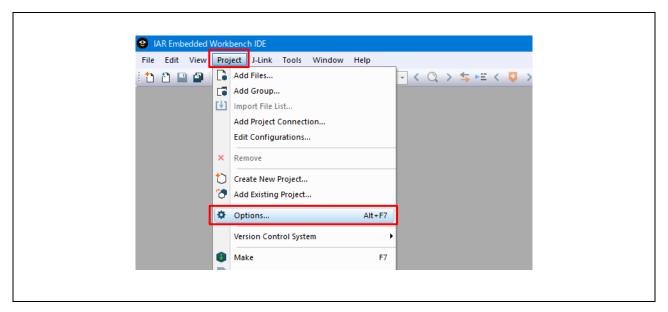

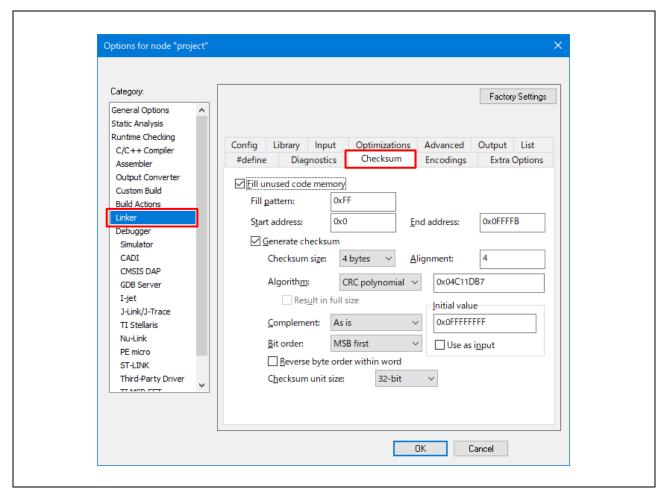

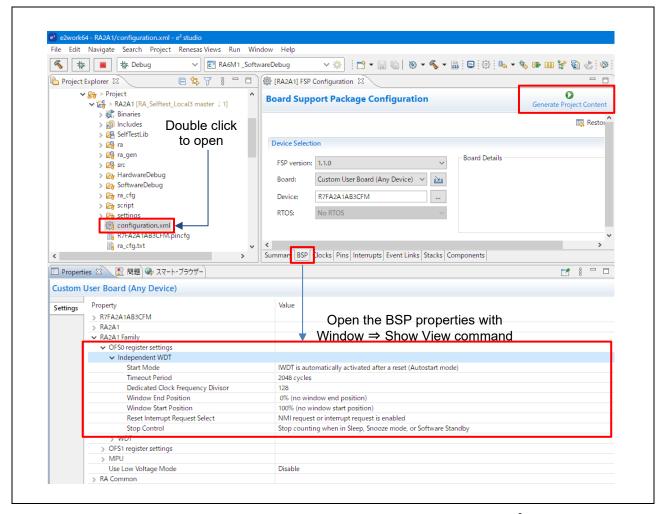

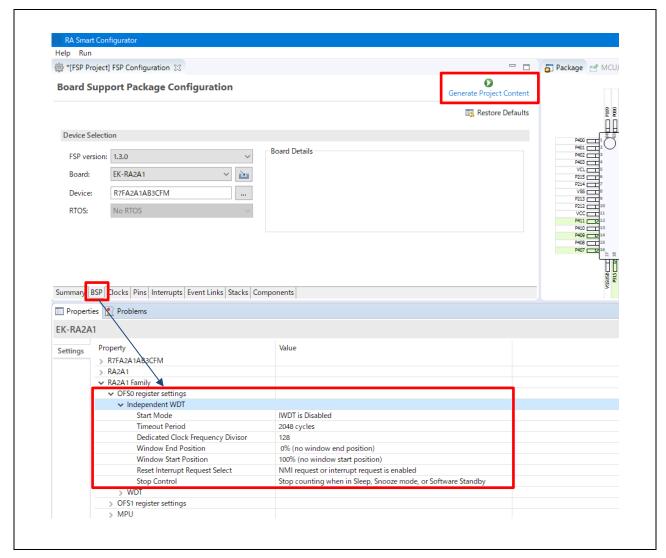

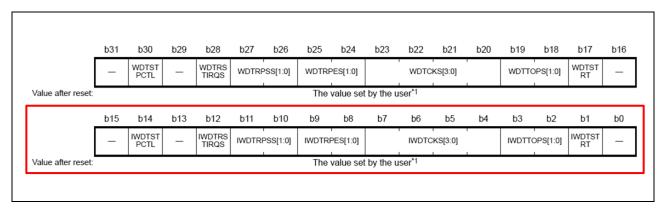

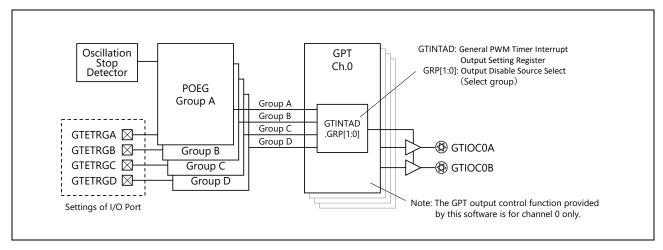

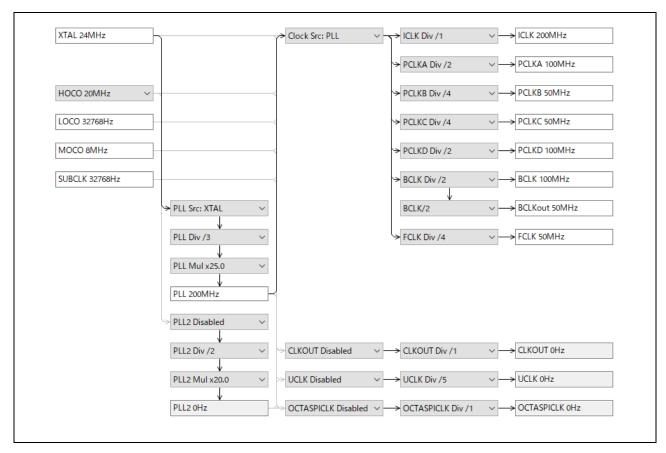

| Input Parameters                 |                                                                                                                                                                                      |