## RX66T Group, RX62T/RX62G Group

Differences Between the RX66T Group and the RX62T Group

## **Summary**

This application note is intended as a reference to points of difference between the peripheral functions, I/O registers, and pin functions of the RX66T Group and RX62T Group, as well as a guide to key points to consider when migrating between the two groups.

Unless specifically otherwise noted, the information in this application note applies to the 144-pin package version (with programmable gain amplifier (PGA), pseudo-differential input, and USB pins) of the RX66T Group and the 112-pin package version of the RX62T Group as the maximum specifications. To confirm details of differences in the specifications of the electrical characteristics, usage notes, and setting procedures, refer to the User's Manual: Hardware of the products in question.

#### **Target Devices**

RX66T Group and RX62T Group

## **Contents**

| 1.   | Comparison of Built-In Functions of RX66T Group and RX62T Group                  | 5   |

|------|----------------------------------------------------------------------------------|-----|

| 2.   | Comparative Overview of Specifications                                           | 7   |

| 2.1  | CPU                                                                              | 7   |

| 2.2  | Operating Modes                                                                  | 8   |

| 2.3  | Address Space                                                                    | 9   |

| 2.4  | Resets                                                                           | 12  |

| 2.5  | Voltage Detection Circuit                                                        | 13  |

| 2.6  | Clock Generation Circuit                                                         | 15  |

| 2.7  | Low Power Consumption                                                            | 19  |

| 2.8  | Exception Handling                                                               | 25  |

| 2.9  | Interrupt Controller                                                             | 26  |

| 2.10 | Buses                                                                            | 30  |

| 2.11 | Memory-Protection Unit                                                           | 32  |

| 2.12 | Data Transfer Controller                                                         | 33  |

| 2.13 | I/O Ports                                                                        | 35  |

| 2.14 | Multi-Function Timer Pulse Unit 3                                                | 41  |

| 2.15 | Port Output Enable 3                                                             | 48  |

| 2.16 | General PWM Timer                                                                | 63  |

| 2.17 | Compare Match Timer                                                              | 72  |

| 2.18 | Watchdog Timer                                                                   | 73  |

| 2.19 | Independent Watchdog Timer                                                       | 75  |

| 2.20 | Serial Communications Interface                                                  | 78  |

| 2.21 | I <sup>2</sup> C Bus Interface                                                   | 85  |

| 2.22 | CAN Module                                                                       | 88  |

| 2.23 | Serial Peripheral Interface                                                      | 91  |

| 2.24 | CRC Calculator                                                                   | 94  |

| 2.25 | 12-Bit A/D Converter                                                             | 96  |

| 2.26 | RAM                                                                              | 106 |

| 2.27 | Flash Memory                                                                     | 108 |

| 2.28 | Packages                                                                         | 113 |

| 3.   | Comparison of Pin Functions                                                      | 114 |

| 3.1  | 112-Pin Package                                                                  | 114 |

| 3.2  | 100-Pin Package (RX66T: With PGA Pseudo-Differential Input and USB Pins)         | 119 |

| 3.3  | 100-Pin Package (RX66T: With PGA Pseudo-Differential Input and Without USB Pins) | 124 |

| 3.4  | 100-Pin Package (RX66T: Without PGA Pseudo-Differential Input and USB Pins)      | 129 |

| 3.5  | 80-Pin Package (RX62T: LQFP (Other Than R5F562TxGDFF))                           | 134 |

| 3.6  | 80-Pin Package (RX62T: LQFP (R5F562TxGDFF))                                      | 138 |

| 3.7  | 64-Pin Package                                                                   | 142 |

| 4. lı  | mportant Information when Migrating Between MCUs                                  | 145 |

|--------|-----------------------------------------------------------------------------------|-----|

| 4.1    | Notes on Pin Design                                                               | 145 |

| 4.1.1  | VCL Pin (External Capacitor)                                                      | 145 |

| 4.1.2  | PLLVCC Pin                                                                        | 145 |

| 4.1.3  | Mode Setting Pins                                                                 | 145 |

| 4.1.4  | Inputting an External Clock                                                       | 145 |

| 4.1.5  | PGA Pseudo-Differential Input-Related Pins (P40 to P42, P44 to P46, PH0, and PH4) | 145 |

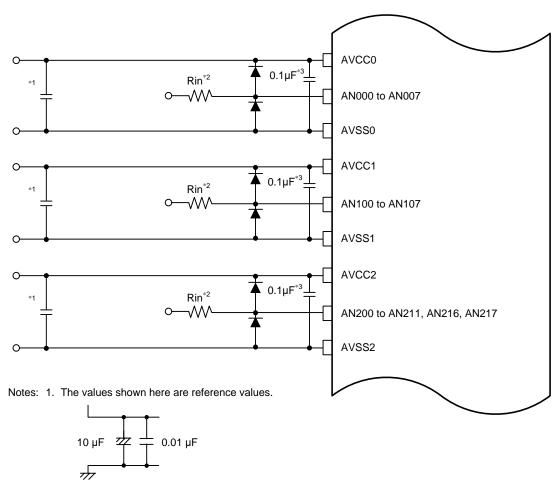

| 4.1.6  | Inserting Decoupling Capacitors between AVCC and AVSS Pins                        | 146 |

| 4.2    | Notes on Functional Design                                                        | 147 |

| 4.2.1  | RIIC Operating Voltage Setting                                                    | 147 |

| 4.2.2  | USB Operating Voltage Setting                                                     | 147 |

| 4.2.3  | Exception Vector Table                                                            | 147 |

| 4.2.4  | Voltage Level Setting                                                             | 147 |

| 4.2.5  | Endian Setting                                                                    | 147 |

| 4.2.6  | Option-Setting Memory                                                             | 147 |

| 4.2.7  | Clock Frequency Settings                                                          | 148 |

| 4.2.8  | Main Clock Oscillator                                                             | 148 |

| 4.2.9  | PLL Circuit                                                                       | 148 |

| 4.2.10 | Operation of Main Clock Oscillation Stop Detection Function                       | 148 |

| 4.2.11 | All-Module Clock Stop Mode                                                        | 148 |

| 4.2.12 | Input Buffer Control by DIRQnE Bits (n = 0 to 15)                                 | 148 |

| 4.2.13 | Register Write Protection Function                                                | 149 |

| 4.2.14 | Software Configurable Interrupts                                                  | 149 |

| 4.2.15 | Initialization of Port Direction Register (PDR)                                   | 149 |

| 4.2.16 | Note on Controlling Switching to General I/O Port Pin Operation by POE3           | 149 |

| 4.2.17 | Bus Priority                                                                      | 149 |

| 4.2.18 | Pin Assignments                                                                   | 149 |

| 4.2.19 | Operating Frequencies of the GPTW and MTU3d                                       | 149 |

| 4.2.20 | DMAC Activation by the MTU                                                        | 149 |

| 4.2.21 | MTIOC Pin Output Level when Counter Stopped                                       | 150 |

| 4.2.22 | Note on Timer Mode Register Setting for ELC Event Input                           | 150 |

| 4.2.23 | Port Output Enable                                                                | 150 |

| 4.2.24 | Control in Response to Output Disabling Request on Port Output Enable 3           | 150 |

| 4.2.25 | Setting the Active Level with MTU or GPTW Set to Inverted Output                  | 150 |

| 4.2.26 | Reading Pins in High-Impedance State                                              | 150 |

| 4.2.27 | Note on Using POE and POEG Together                                               | 150 |

| 4.2.28 | General PWM Timer                                                                 | 151 |

|        | Watchdog Timer and Independent Watchdog Timer                                     |     |

| 4.2.30 | Eliminating I <sup>2</sup> C Bus Interface Noise                                  | 151 |

| 4 2 31 | 12-Bit A/D Converter                                                              | 151 |

# Differences Between the RX66T Group and the RX62T Group

| 4.2.32 | A/D Conversion Start Bit                        | 151 |

|--------|-------------------------------------------------|-----|

| 4.2.33 | Restrictions on Comparison Function             | 151 |

| 4.2.34 | Generation of A/D Scan Conversion End Interrupt | 151 |

| 4.2.35 | D/A Converter Settings                          | 151 |

| 4.2.36 | Transferring Firmware to FCU RAM                | 151 |

| 4.2.37 | ROM Cache                                       | 152 |

| 4.2.38 | Using Flash Memory Programming Commands         | 152 |

| 5. R   | eference Documents                              | 153 |

| Revisi | on History                                      | 155 |

## 1. Comparison of Built-In Functions of RX66T Group and RX62T Group

A comparison of the built-in functions of the RX66T Group and RX62T Group is provided below. For details of the functions, see section 2, Comparative Overview of Specifications and section 5, Reference Documents.

Table 1.1 is a comparison of built-in functions of RX66T Group and RX62T Group.

Table 1.1 Comparison of Built-In Functions of RX66T Group and RX62T Group

| Function                                                                 | RX62T | RX66T    |

|--------------------------------------------------------------------------|-------|----------|

| <u>CPU</u>                                                               |       |          |

| Operating modes                                                          |       |          |

| Address space                                                            |       |          |

| Resets                                                                   |       |          |

| Option-setting memory (OFSM)                                             | *1    |          |

| Voltage detection circuit (LVD): RX62T, (LVDA): RX66T                    |       |          |

| Clock generation circuit                                                 |       |          |

| Clock frequency accuracy measurement circuit (CAC)                       | ×     | 0        |

| Low power consumption                                                    |       |          |

| Register write protection function                                       | ×     |          |

| Exception handling                                                       |       | <u> </u> |

| Interrupt controller (ICU): RX62T, (ICUC): RX66T                         |       |          |

| Buses                                                                    |       |          |

| Memory-protection unit (MPU)                                             |       | <u> </u> |

| DMA controller (DMACAa)                                                  | ×     |          |

| Data transfer controller (DTC): RX62T, (DTCa): RX66T                     |       |          |

| Event link controller (ELC)                                              | ×     |          |

| I/O ports                                                                |       |          |

| Multi-function pin controller (MPC)                                      | *2    |          |

| Multi-function timer pulse unit 3 (MTU3): RX62T, (MTU3d): RX66T          |       |          |

| Port output enable 3 (POE3): RX62T, (POE3B): RX66T                       |       |          |

| General PWM timer (GPT/GPTa): RX62T, (GPTW): RX66T                       |       | *3       |

| High resolution pwm waveform generation circuit (HRPWM)                  | *4    |          |

| GPTW port output enable (POEG)                                           | ×     | 0        |

| 8-Bit Timer (TMR)                                                        | ×     | 0        |

| Compare match timer (CMT)                                                |       |          |

| Watchdog timer (WDT): RX62T, (WDTA): RX66T                               |       | /_       |

| Independent watchdog timer (IWDT): RX62T, (IWDTa): RX66T                 |       |          |

| USB 2.0 FS Host/Function module (USBb)                                   | ×     | 0        |

| Serial communications interface (SCIb): RX62T, (SCIj, SCIi, SCIh): RX66T |       |          |

| I <sup>2</sup> C-bus interface (RIIC): RX62T, (RIICa): RX66T             |       |          |

| CAN module (CAN)                                                         |       |          |

| Serial peripheral interface (RSPI): RX62T, (RSPIc): RX66T                |       |          |

| CRC calculator (CRC): RX62T, (CRCA): RX66T                               |       |          |

| Trusted secure IP (TSIP-Lite)                                            | ×     | 0        |

| LIN module (LIN)                                                         | 0     | *5       |

| 12-Bit A/D converter (S12ADA): RX62T, (S12ADH): RX66T                    |       |          |

| 10-Bit A/D converter (ADA)                                               | 0     | X        |

| 12-Bit D/A converter (R12DAb)                                            | ×     | 0        |

| Temperature sensor (TEMPS)                                               | ×     | 0        |

| Comparator C (CMPC)                                                      | *6    | 0        |

| Function                     |   | RX66T |  |

|------------------------------|---|-------|--|

| Data operation circuit (DOC) | X | 0     |  |

| RAM                          |   | ●/▲   |  |

| Flash memory                 |   | /_    |  |

| Packages                     |   | /     |  |

○: Available, X: Unavailable, •: Differs due to added functionality,

▲: Differs due to change in functionality, ■: Differs due to removed functionality.

- Notes: 1. Functions of the RX62T Group and RX62G Group listed in the ROM (Flash Memory for Code Storage) section correspond to functions of the RX66T Group listed in the Option-Setting Memory (OFSM) section of the respective User's Manual: Hardware, Refer to section 4, Important Information when Migrating Between MCUs, for details.

- 2. Functions of the RX62T Group and RX62G Group listed in the I/O Ports section correspond to functions of the RX66T Group listed in the Multi-Function Pin Controller (MPC) section of the respective User's Manual: Hardware. Refer to section 4, Important Information when Migrating Between MCUs, for details.

- 3. The GPTa is implemented on the RX62G Group only.

- 4. Functions of the RX62T Group and RX62G Group listed in the General PWM Timer (GPT/GPTa) section correspond to functions of the RX66T Group listed in the High Resolution PWM Waveform Generation Circuit (HRPWM) section of the respective User's Manual: Hardware.

- 5. Functions of the RX66T Group listed in the Serial Communications Interface (SCIh) section correspond to functions of the RX62T Group and RX62G Group listed in the LIN Module (LIN) section of the respective User's Manual: Hardware.

- 6. Comparator functions of the RX62T Group and RX62G Group are listed in the 12-Bit A/D Converter (S12ADA) section of RX62T Group, RX62G Group: User's Manual: Hardware.

### 2. Comparative Overview of Specifications

This section presents a comparative overview of specifications, including registers.

In the comparative overview, red text indicates functions which are included only in one of the MCU groups and also functions for which the specifications differ between the two groups.

In the register comparison, red text indicates differences in specifications for registers that are included in both groups and black text indicates registers which are included only in one of the MCU groups. Differences in register specifications are not listed.

#### 2.1 CPU

Table 2.1 is a comparative overview of CPUs, and Table 2.2 is a comparison of CPU registers.

**Table 2.1 Comparative Overview of CPUs**

| Item | RX62T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RX66T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU  | <ul> <li>Maximum operating frequency: 100 MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution time: One instruction per state (cycle of the system clock)</li> <li>Address space: 4 GB linear</li> <li>Register set of the CPU  — General purpose: Sixteen 32-bit registers  — Control: Nine 32-bit registers  — Accumulator: One 64-bit register</li> <li>Basic instructions: 73</li> <li>Floating-point instructions: 8</li> <li>DSP instructions: 9</li> <li>Addressing modes: 10</li> <li>Data arrangement  — Instructions: Little endian  — Data: Selectable as little endian or big endian</li> <li>On-chip 32-bit multiplier: 32 × 32 → 64 bits</li> <li>On-chip divider: 32/32 → 32 bits</li> <li>Barrel shifter: 32 bits</li> <li>Memory-protection unit (MPU)</li> </ul> | <ul> <li>Maximum operating frequency: 160 MHz</li> <li>32-bit RX CPU (RXv3)</li> <li>Minimum instruction execution time: One instruction per state (cycle of the system clock)</li> <li>Address space: 4 GB linear</li> <li>Register set of the CPU  — General purpose: Sixteen 32-bit registers  — Control: Ten 32-bit registers  — Accumulator: Two 72-bit registers</li> <li>Basic instructions: 77</li> <li>Single precision floating point instructions: 11</li> <li>DSP instructions: 23</li> <li>Addressing modes: 11</li> <li>Data arrangement  — Instructions: Little endian  — Data: Selectable as little endian or big endian</li> <li>On-chip 32-bit multiplier: 32 × 32 → 64 bits</li> <li>On-chip divider: 32/32 → 32 bits</li> <li>Barrel shifter: 32 bits</li> <li>Memory-protection unit (MPU)</li> </ul> |

| FPU  | <ul> <li>Single precision (32-bit) floating point</li> <li>Data types and floating-point exceptions in conformance with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>Single precision (32-bit) floating point</li> <li>Data types and floating-point exceptions in conformance with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 2.2 Comparison of CPU Registers

| Register           | Bit | RX62T       | RX66T                        |

|--------------------|-----|-------------|------------------------------|

| EXTB               |     | _           | Exception table register     |

| ACC (RX62T)        |     | Accumulator | Accumulator 0, accumulator 1 |

| ACC0, ACC1 (RX66T) |     |             |                              |

## 2.2 Operating Modes

Table 2.3 is a comparative overview of operating modes, and Table 2.4 is a comparison of operating mode–related registers.

**Table 2.3 Comparative Overview of Operating Modes**

| Item                         | RX62T            | RX66T                              |

|------------------------------|------------------|------------------------------------|

| Selection of operating modes | Single-chip mode | Single-chip mode                   |

| by mode-setting pins on      | Boot mode        | Boot mode (SCI interface)          |

| release from reset state     | _                | Boot mode (USB interface)          |

|                              | _                | Boot mode (FINE interface)         |

|                              | _                | User boot mode                     |

| Selection of operating modes | Single-chip mode | Single-chip mode                   |

| by register settings         | _                | User boot mode                     |

|                              | _                | On-chip ROM disabled extended mode |

|                              | _                | On-chip ROM enabled extended mode  |

| Selection of endian          | MDE pin          | MDE register                       |

Table 2.4 Comparison of Operating Mode-Related Registers

| Register | Bit     | RX62T                                     | RX66T                       |

|----------|---------|-------------------------------------------|-----------------------------|

| MDMONR   | MD      | _                                         | MD Pin Status Flag          |

|          | MD0     | MD0 status flag                           | _                           |

|          | MD1     | MD1 status flag                           | _                           |

|          | MDE     | MDE status flag                           | _                           |

| MDSR     | IROM    | On-chip ROM startup status flag           | _                           |

|          | BOTS    | Boot mode startup flag                    | _                           |

|          | UBTS    | _                                         | User boot mode startup flag |

| SYSCR0   | EXBE    | _                                         | External bus enable         |

| SYSCR1   |         | System control register 1                 | System control register 1   |

|          |         | Initial values after a reset are differen | it.                         |

|          | ECCRAME | _                                         | ECCRAM enable               |

| VOLSR    |         | — Voltage level setting register          |                             |

#### 2.3 Address Space

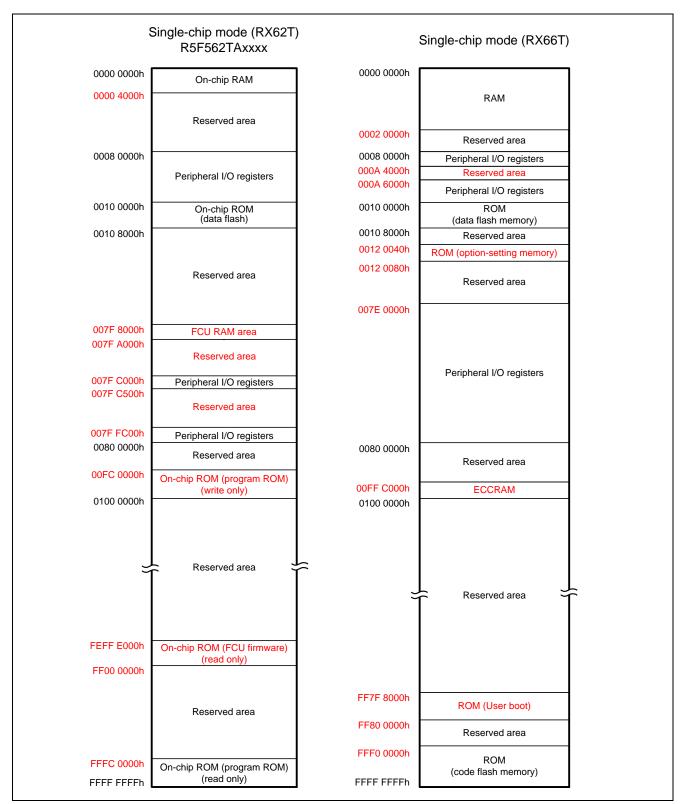

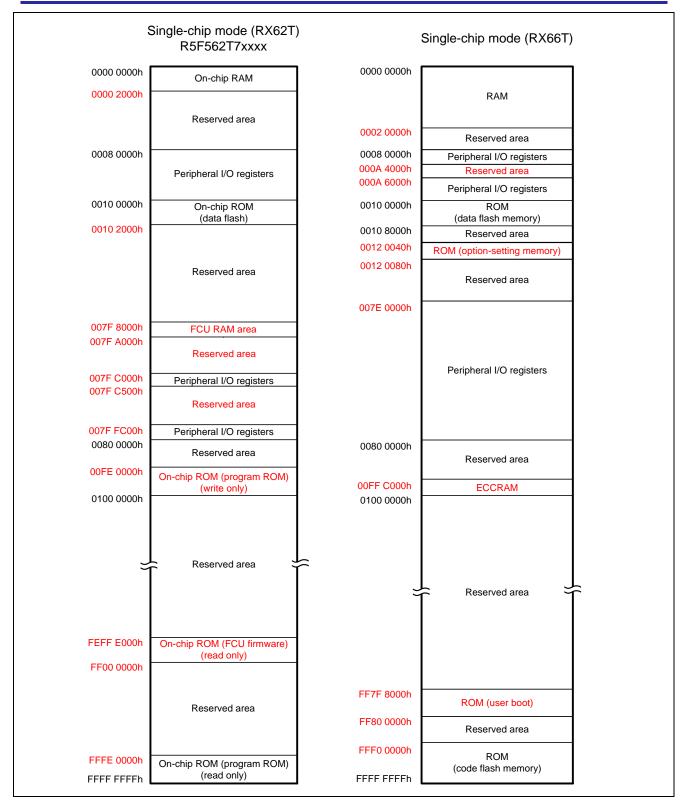

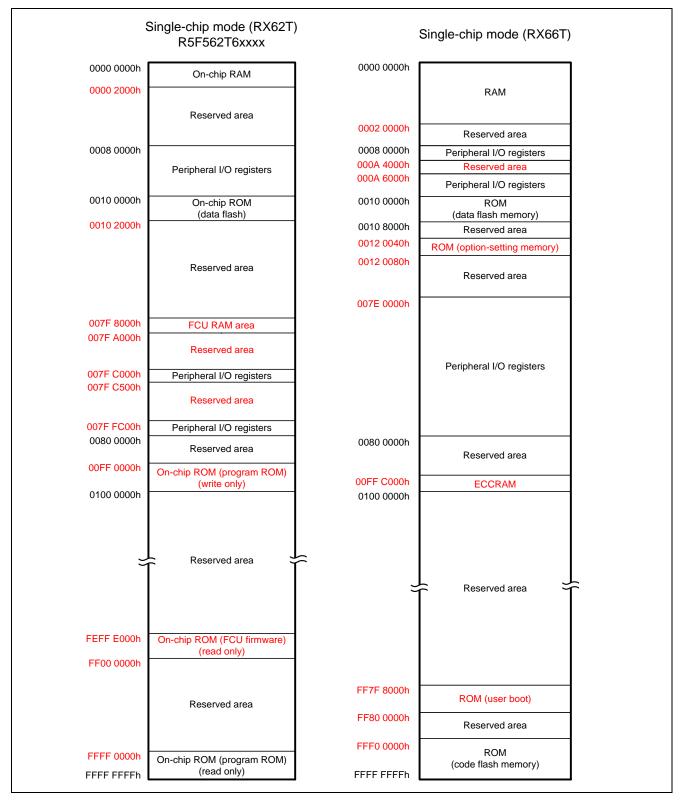

Figure 2.1 is a comparative memory map of single-chip mode (RX62T: R5F562TAxxxx), Figure 2.2 is a comparative memory map of single-chip mode (RX62T: R5F562T7xxxx), and Figure 2.3 is a comparative memory map of single-chip mode (RX62T: R5F562T6xxxx).

Figure 2.1 Comparative Memory Map of Single-Chip Mode (RX62T: R5F562TAxxxx)

Figure 2.2 Comparative Memory Map of Single-Chip Mode (RX62T: R5F562T7xxxx)

Figure 2.3 Comparative Memory Map of Single-Chip Mode (RX62T: R5F562T6xxxx)

## 2.4 Resets

Table 2.5 is a comparative overview of resets, and Table 2.6 is a comparison of reset-related registers.

**Table 2.5 Comparative Overview of Resets**

| Item                             | RX62T                                                                                | RX66T                                                                                |

|----------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| RES# pin reset                   | Generated when the RES# pin is driven low.                                           | Generated when the RES# pin is driven low.                                           |

| Power-on reset                   | Generated when VCC rises or VCC falls (monitored voltage: VPOR).                     | Generated when VCC rises (monitored voltage: VPOR).                                  |

| Voltage-monitoring 0 reset       | _                                                                                    | Generated when VCC falls (monitored voltage: Vdet0).                                 |

| Voltage-monitoring 1 reset       | Generated when VCC falls (monitored voltage: Vdet1).                                 | Generated when VCC falls (monitored voltage: Vdet1).                                 |

| Voltage-monitoring 2 reset       | Generated when VCC falls (monitored voltage: Vdet2).                                 | Generated when VCC falls (monitored voltage: Vdet2).                                 |

| Deep software standby reset      | Generated in response to an interrupt to trigger release from deep software standby. | Generated in response to an interrupt to trigger release from deep software standby. |

| Independent watchdog timer reset | Generated when the independent watchdog timer underflows.                            | Generated when the independent watchdog timer underflows, or a refresh error occurs. |

| Watchdog timer reset             | Generated when the independent watchdog timer overflows.                             | Generated when the watchdog timer underflows, or a refresh error occurs.             |

| Software reset                   | <u> </u>                                                                             | Generated by register setting.                                                       |

Table 2.6 Comparison of Registers for Resets

| Register | Bit | RX62T                         | RX66T                   |

|----------|-----|-------------------------------|-------------------------|

| RSTSR    | _   | Reset status register         | _                       |

| RSTSR0   | _   | _                             | Reset status register 0 |

| RSTSR1   | _   | _                             | Reset status register 1 |

| RSTSR2   | _   | _                             | Reset status register 2 |

| RSTCSR   | _   | Reset control/status register | _                       |

| IWDTSR   | _   | IWDT status register          | _                       |

| SWRR     | _   | _                             | Software reset register |

## 2.5 Voltage Detection Circuit

Table 2.7 is a comparative overview of the voltage detection circuits, and Table 2.8 is a comparison of voltage detection circuit registers.

**Table 2.7 Comparative Overview of Voltage Detection Circuits**

|                      |                          | RX62T (LVD)                                     |                                                                                       | RX66T (LVDA)                                                                         |                                                                                                             |                                                                                                             |

|----------------------|--------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|                      |                          | Voltage                                         | Voltage                                                                               | Voltage                                                                              | Voltage                                                                                                     | Voltage                                                                                                     |

| Item                 |                          | Monitoring 1                                    | Monitoring 2                                                                          | Monitoring 0                                                                         | Monitoring 1                                                                                                | Monitoring 2                                                                                                |

| VCC<br>monitoring    | Monitored voltage        | Vdet1                                           | Vdet2                                                                                 | Vdet0                                                                                | Vdet1                                                                                                       | Vdet2                                                                                                       |

|                      | Detected event           | Voltage drops<br>past Vdet1                     | Voltage drops past<br>Vdet2                                                           | Voltage drops past<br>Vdet0                                                          | Voltage rises or drops past Vdet1                                                                           | Voltage rises or drops past Vdet2                                                                           |

|                      | Detection<br>voltage     | One level only                                  | One level only                                                                        | Selectable from<br>among two different<br>levels by using<br>OFS1.VDSEL[1:0]<br>bits | Selectable from<br>among five different<br>levels by using<br>LVDLVLR.LVD1LVL<br>[3:0] bits                 | Selectable from<br>among five different<br>levels by using<br>LVDLVLR.LVD2LVL<br>[3:0] bits                 |

|                      | Monitoring flag          | None                                            | None                                                                                  | None                                                                                 | LVD1SR.LVD1MON<br>flag: Monitors<br>whether voltage is<br>higher or lower than<br>Vdet1                     | LVD2SR.LVD2MON<br>flag: Monitors<br>whether voltage is<br>higher or lower than<br>Vdet2                     |

|                      |                          |                                                 | RSTSR.LVD2F<br>flag: Vdet2<br>passage detection                                       | None                                                                                 | LVD1SR.LVD1DET<br>flag: Vdet1 passage<br>detection                                                          | LVD2SR.LVD2DET<br>flag: Vdet2 passage<br>detection                                                          |

| Process upon voltage | Reset                    |                                                 | Voltage monitoring 2 reset                                                            | 0 reset                                                                              | Voltage monitoring 1 reset                                                                                  | Voltage monitoring 2 reset                                                                                  |

| detection            |                          | > VCC: CPU restart after                        | Reset when Vdet2<br>> VCC: CPU<br>restart after<br>specified time with<br>VCC > Vdet2 | Reset when Vdet0 > VCC:<br>CPU restart after specified time with VCC > Vdet0         | Reset when Vdet1 > VCC: CPU restart timing selectable: after specified time with VCC > Vdet1 or Vdet1 > VCC | Reset when Vdet2 > VCC: CPU restart timing selectable: after specified time with VCC > Vdet2 or Vdet2 > VCC |

|                      | Interrupt                | Voltage<br>monitoring 1<br>interrupt            | Voltage monitoring 2 interrupt                                                        | No interrupt                                                                         | Voltage monitoring<br>1 interrupt                                                                           | Voltage monitoring 2 interrupt                                                                              |

|                      |                          | Non-maskable interrupt                          | Non-maskable<br>interrupt                                                             |                                                                                      | Non-maskable<br>interrupt or<br>maskable interrupt<br>selectable                                            | Non-maskable<br>interrupt or<br>maskable interrupt<br>selectable                                            |

|                      |                          | Interrupt request<br>issued when<br>Vdet1 > VCC | Interrupt request<br>issued when Vdet2<br>> VCC                                       |                                                                                      | Interrupt request<br>issued when Vdet1<br>> VCC and VCC ><br>Vdet1, or either                               | Interrupt request<br>issued when Vdet2<br>> VCC and VCC ><br>Vdet2, or either                               |

| Digital filter       | Enable/disable switching | Digital filter function not available           | Digital filter function not available                                                 | Digital filter function not available                                                | Available                                                                                                   | Available                                                                                                   |

|                      | Sampling time            |                                                 |                                                                                       | _                                                                                    | 1/n LOCO<br>frequency × 2<br>(n: 2, 4, 8, 16)                                                               | 1/n LOCO<br>frequency × 2<br>(n: 2, 4, 8, 16)                                                               |

| Event linking        |                          | None                                            | None                                                                                  | None                                                                                 | Available Output of event signals on detection of Vdet crossings                                            | Available Output of event signals on detection of Vdet crossings                                            |

**Table 2.8 Comparison of Voltage Detection Circuit Registers**

| Register | Bit | RX62T (LVD)                                                         | RX66T (LVDA)                                    |

|----------|-----|---------------------------------------------------------------------|-------------------------------------------------|

| RSTSR    | _   | Reset status register                                               | <del></del>                                     |

| LVDKEYR  | _   | Key code register for low-<br>voltage detection control<br>register |                                                 |

| LVDCR    | _   | Low-voltage detection control register                              | _                                               |

| LVD1CR1  | _   | _                                                                   | Voltage monitoring 1 circuit control register 1 |

| LVD1SR   | _   | _                                                                   | Voltage monitoring 1 circuit status register    |

| LVD2CR1  | _   | _                                                                   | Voltage monitoring 2 circuit control register 1 |

| LVD2SR   | _   | _                                                                   | Voltage monitoring 2 circuit status register    |

| LVCMPCR  | _   | _                                                                   | Voltage monitoring circuit control register     |

| LVDLVLR  | _   | _                                                                   | Voltage detection level select register         |

| LVD1CR0  | _   | _                                                                   | Voltage monitoring 1 circuit control register 0 |

| LVD2CR0  | _   | _                                                                   | Voltage monitoring 2 circuit control register 0 |

## 2.6 Clock Generation Circuit

Table 2.9 is a comparative overview of the clock generation circuits, and Table 2.10 is a comparison of clock generation circuit registers.

**Table 2.9 Comparative Overview of Clock Generation Circuits**

| Item | RX62T                                                                                            | RX66T                                                                                                                                                                                                                          |

|------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use  | Generates the system clock (ICLK) to<br>be supplied to the CPU, DTC, MTU3,<br>GPT, ROM, and RAM. | Generates the system clock (ICLK) to<br>be supplied to the CPU, DMAC, DTC,<br>code flash memory, and RAM.                                                                                                                      |

|      |                                                                                                  | <ul> <li>Generates the peripheral module clock<br/>(PCLKA) to be supplied to the RSPI,<br/>SCIi, MTU3 (internal peripheral buses),<br/>GPTW (internal peripheral buses), and<br/>HRPWM (internal peripheral buses).</li> </ul> |

|      | Generates the peripheral module clock<br>(PCLK) to be supplied to peripheral<br>modules.         | Generates the peripheral module clock<br>(PCLKB) to be supplied to peripheral<br>modules.                                                                                                                                      |

|      |                                                                                                  | Generates the counter reference clock<br>for the peripheral module to be<br>supplied to the MTU3 and GPTW, and<br>the reference clock (PCLKC) for the<br>HRPWM.                                                                |

|      |                                                                                                  | Generates the peripheral module<br>clocks (for analog conversion)<br>(PCLKD) to be supplied to S12AD.                                                                                                                          |

|      |                                                                                                  | Generates the flash-IF clock (FCLK) to<br>be supplied to the flash interface.                                                                                                                                                  |

|      |                                                                                                  | Generates the external bus clock<br>(BCLK) to be supplied to the external<br>bus.                                                                                                                                              |

|      |                                                                                                  | Generates the USB clock (UCLK) to be supplied to the PHY in the USBb.                                                                                                                                                          |

|      |                                                                                                  | Generates the CAC clock (CACCLK) to<br>be supplied to the CAC.                                                                                                                                                                 |

|      |                                                                                                  | Generates the CAN clock (CANMCLK) to be supplied to the CAN.                                                                                                                                                                   |

|      | Generates the on-chip oscillator clock<br>(IWDTCLK) to be supplied to the<br>IWDT.               | Generates the IWDT-dedicated clock<br>(IWDTCLK) to be supplied to the<br>IWDT.                                                                                                                                                 |

| Item            | RX62T                                                                            | RX66T                                                                                                                 |

|-----------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Operating       | ICLK: 8 MHz to 100 MHz                                                           | ICLK: 160 MHz (max.)                                                                                                  |

| frequency       | PCLK: 8 MHz to 50 MHz                                                            | <ul> <li>PCLKA: 120 MHz (max.)</li> </ul>                                                                             |

|                 |                                                                                  | PCLKB: 60 MHz (max.)                                                                                                  |

|                 |                                                                                  | PCLKC: 160 MHz (max.)                                                                                                 |

|                 |                                                                                  | PCLKD: 8 MHz to 60 MHz (for                                                                                           |

|                 |                                                                                  | conversion with 12-bit A/D converter)                                                                                 |

|                 |                                                                                  | FCLK:                                                                                                                 |

|                 |                                                                                  | <ul> <li>4 MHz to 60 MHz (for programming<br/>and erasing the code flash memory<br/>and data flash memory)</li> </ul> |

|                 |                                                                                  | <ul> <li>— 60 MHz (max.) (for reading from the data flash memory)</li> </ul>                                          |

|                 |                                                                                  | BCLK: 60 MHz (max.)                                                                                                   |

|                 |                                                                                  | BCLK pin output: 40 MHz (max.)                                                                                        |

|                 |                                                                                  | UCLK: 48 MHz (max.)                                                                                                   |

|                 |                                                                                  | CACCLK:                                                                                                               |

|                 |                                                                                  | Same as the clock from respective                                                                                     |

|                 |                                                                                  | oscillators                                                                                                           |

|                 | - IMPTOLIC 195 kHz (tup.)                                                        | CANMCLK: 24 MHz (max.)                                                                                                |

|                 | <ul><li>IWDTCLK: 125 kHz (typ.)</li><li>Restrictions for setting clock</li></ul> | IWDTCLK: 120 kHz                                                                                                      |

|                 | frequencies: ICLK ≥ PCLK                                                         | Restrictions for setting clock     frequencies:                                                                       |

|                 | requencies. IOER 2 1 OER                                                         | frequencies:<br>ICLK ≥ BCLK, PCLKC ≥ PCLKA ≥                                                                          |

|                 |                                                                                  | PCLKB                                                                                                                 |

| Main clock      | Resonator frequency:                                                             | Resonator frequency:                                                                                                  |

| oscillator      | 8 MHz to 12.5 MHz                                                                | 8 MHz to 24 MHz                                                                                                       |

|                 |                                                                                  | <ul> <li>External clock input frequency:<br/>24 MHz (max.)</li> </ul>                                                 |

|                 | Connectable resonator or additional circuit:                                     | <ul> <li>Connectable resonator or additional circuit:</li> </ul>                                                      |

|                 | ceramic resonator, crystal resonator                                             | ceramic resonator, crystal resonator                                                                                  |

|                 | Connection pin: EXTAL, XTAL                                                      | Connection pin: EXTAL, XTAL                                                                                           |

|                 | Oscillation stop detection function:                                             | Oscillation stop detection function:                                                                                  |

|                 | Switches to internal oscillation upon                                            | When an oscillation stop is detected                                                                                  |

|                 | detection of main clock oscillator stop,                                         | with the main clock, the system clock                                                                                 |

|                 | Sets the MTU3 and GPT pins to the high-impedance state                           | source is switched to LOCO. MTU3 and GPTW output can be                                                               |

|                 | Tilgh-impedance state                                                            | forcedly driven to the high-impedance.                                                                                |

| PLL frequency   | Input clock source: Main clock                                                   | Input clock source: Main clock, HOCO                                                                                  |

| synthesizer     | <ul> <li>Input pulse frequency division ratio: 1</li> </ul>                      | <ul> <li>Input pulse frequency division ratio:</li> <li>Selectable from 1, 2, and 3</li> </ul>                        |

|                 | Input frequency: 8 MHz to 12.5 MHz                                               | <ul> <li>Input frequency: 8 MHz to 24 MHz</li> </ul>                                                                  |

|                 | Frequency multiplication ratio: 8                                                | Frequency multiplication ratio:                                                                                       |

|                 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                          | Selectable from 10 to 30                                                                                              |

|                 | Output clock frequency of the PLL                                                | Output clock frequency of the PLL                                                                                     |

|                 | frequency synthesizer: 64 MHz to 100 MHz                                         | frequency synthesizer: 120 MHz to 240 MHz                                                                             |

| High-speed on-  |                                                                                  | Selectable from 16 MHz, 18 MHz, and                                                                                   |

| chip oscillator |                                                                                  | 20 MHz                                                                                                                |

| (HOCO)          |                                                                                  | HOCO power supply control                                                                                             |

| Low-speed on-   | -                                                                                | Oscillation frequency: 240 kHz                                                                                        |

| chip oscillator |                                                                                  |                                                                                                                       |

| (LOCO)          |                                                                                  |                                                                                                                       |

| Item                              | RX62T                          | RX66T                                                                                                        |

|-----------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------|

| IWDT-dedicated on-chip oscillator | Oscillation frequency: 125 kHz | Oscillation frequency: 120 kHz                                                                               |

| Control of output on the BCLK pin |                                | <ul> <li>BCLK clock output or high output is<br/>selectable</li> <li>BCLK or BCLK/2 is selectable</li> </ul> |

| Event linking (output)            | _                              | Detection of stopping of the main clock oscillator                                                           |

| Event linking (input)             | _                              | Switching of the clock source to the low-<br>speed on-chip oscillator                                        |

Table 2.10 Comparison of Clock Generation Circuit Registers

| Register | Bit       | RX62T                                         | RX66T                                              |

|----------|-----------|-----------------------------------------------|----------------------------------------------------|

| SCKCR    | _         | System control register                       | System control register                            |

|          |           | Initial values after a reset are differen     | nt.                                                |

|          | PCKD[3:0] | _                                             | Peripheral module clock D (PCLKD) select bits      |

|          | PCKC[3:0] | _                                             | Peripheral module clock C (PCLKC) select bits      |

|          | PCK[3:0]  | Peripheral Module Clock Select bits           | _                                                  |

|          | PCKB[3:0] | _                                             | Peripheral module clock B (PCLKB) select bits      |

|          | PCKA[3:0] | _                                             | Peripheral module clock A (PCLKA) select bits      |

|          | BCK[3:0]  | _                                             | External bus clock (BCLK) select bits              |

|          | PSTOP1    |                                               | BCLK pin output control bit                        |

|          | ICK[3:0]  | System clock select bits                      | System clock (ICLK) select bits                    |

|          |           | b27 b24                                       | b27 b24                                            |

|          |           | 0 0 0 0: ×8                                   | 0 0 0 0: ×1/1                                      |

|          |           | 0 0 0 1: ×4                                   | 0 0 0 1: ×1/2                                      |

|          |           | 0 0 1 0: ×2                                   | 0 0 1 0: ×1/4                                      |

|          |           | 0 0 1 1: ×1                                   | 0 0 1 1: ×1/8                                      |

|          |           |                                               | 0 1 0 0: ×1/16                                     |

|          |           |                                               | 0 1 0 1: ×1/32                                     |

|          |           |                                               | 0 1 1 0: ×1/64                                     |

|          |           | Settings other than the above are prohibited. | Settings other than the above are prohibited.      |

|          | FCK[3:0]  | _                                             | Flash-IF clock (FCLK) select bit                   |

| MEMWAIT  | _         | _                                             | Memory wait cycle setting                          |

| SCKCR2   | _         | _                                             | System clock control register 2                    |

| SCKCR3   | _         | _                                             | System clock control register 3                    |

| PLLCR    | _         |                                               | PLL control register                               |

| PLLCR2   | _         |                                               | PLL control register 2                             |

| BCKCR    | _         |                                               | External bus clock control register                |

| MOSCCR   | _         | _                                             | Main clock oscillator control register             |

| LOCOCR   |           | _                                             | Low-speed on-chip oscillator control register      |

| ILOCOCR  | _         | _                                             | IWDT-dedicated on-chip oscillator control register |

| Register | Bit      | RX62T                           | RX66T                                                       |

|----------|----------|---------------------------------|-------------------------------------------------------------|

| HOCOCR   |          | _                               | High-speed on-chip oscillator control register              |

| HOCOCR2  |          |                                 | High-speed on-chip oscillator control register 2            |

| OSCOVFSR |          | _                               | Oscillation stabilization flag register                     |

| OSTDCR   | OSTDIE   | _                               | Oscillation stop detection interrupt enable bit             |

|          | OSTDF    | Oscillation stop detection flag | _                                                           |

|          | KEY[7:0] | OSTDCR key code                 | _                                                           |

| OSTDSR   |          |                                 | Oscillation stop detection status register                  |

| MOSCWTCR |          | _                               | Main clock oscillator wait control register                 |

| MOFCR    | _        | _                               | Main clock oscillator function control register             |

| HOCOPCR  |          | _                               | High-speed on-chip oscillator power supply control register |

## 2.7 Low Power Consumption

Table 2.11 is a comparative overview of low power consumption, Table 2.12 is a comparison of procedures for entering and exiting low power consumption modes and operating states in each mode, and Table 2.13 is a comparison of low power consumption registers.

**Table 2.11 Comparative Overview of Low Power Consumption**

| Item                                                  | RX62T                                                                                                                                 | RX66T                                                                                                                                                                                                  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reducing power consumption by switching clock signals | The frequency division ratio is settable independently for the system clock (ICLK) and peripheral module clock (PCLK)                 | The frequency division ratio is settable independently for the system clock (ICLK), peripheral module clock (PCLKA, PCLKB, PCLKC, PCLKD), external bus clock (BCLK), and flash interface clock (FCLK). |

| BCLK output control function                          | _                                                                                                                                     | BCLK output or high-level output can be selected.                                                                                                                                                      |

| Module-stop function                                  | Functions can be stopped independently for each peripheral module.                                                                    | Functions can be stopped independently for each peripheral module.                                                                                                                                     |

| Function for transition to low power consumption mode | Transition to low power consumption mode is enabled to stop the CPU, peripheral modules, and oscillator.                              | Transition to a low power consumption mode in which the CPU, peripheral modules, or oscillators are stopped is enabled.                                                                                |

| Low power consumption function                        | <ul> <li>Sleep mode</li> <li>All-module clock stop mode</li> <li>Software standby mode</li> <li>Deep software standby mode</li> </ul> | <ul> <li>Sleep mode</li> <li>All-module clock stop mode</li> <li>Software standby mode</li> <li>Deep software standby mode</li> </ul>                                                                  |

Table 2.12 Comparison of Procedures for Entering and Exiting Low Power Consumption Modes and Operating States in Each Mode

|                  | Entering and Exiting Low Power                             |                                       |                                       |

|------------------|------------------------------------------------------------|---------------------------------------|---------------------------------------|

| Mada             | Consumption Modes and Operating                            | DVCCT                                 | DVCCT                                 |

| Mode             | States Transition method                                   | RX62T                                 | RX66T                                 |

| Sleep mode       | Transition method                                          | Control register + instruction        | Control register + instruction        |

|                  | Method of cancellation other than reset                    | Interrupt                             | Interrupt                             |

|                  | State after cancellation                                   | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |

|                  | State after cancellation                                   | Program execution state               | Program execution state               |

|                  |                                                            | (interrupt processing)                | (interrupt processing)                |

|                  | Main clock oscillator                                      | Operating                             | Operating possible                    |

|                  | High-speed on-chip oscillator                              | _                                     | Operating possible                    |

|                  | Low-speed on-chip oscillator                               | _                                     | Operating possible                    |

|                  | IWDT-dedicated on-chip oscillator                          | Operating                             | Operating possible                    |

|                  | PLL                                                        | Operating                             | Operating possible                    |

|                  | CPU                                                        | Stopped (retained)                    | Stopped (retained)                    |

|                  | On-chip RAM                                                | Operating (retained)                  | Operating possible                    |

|                  | (0000 0000h to 0000 3FFFh): RX62T<br>RAM and ECCRAM: RX66T |                                       | (retained)                            |

|                  | Flash memory                                               | Operating                             | Operating                             |

|                  | USB 2.0 Host/Function module (USBb)                        | _                                     | Operating possible                    |

|                  | Watchdog timer                                             | Operating                             | Stopped (retained)                    |

|                  | (WDT: RX62T, WDTA: RX66T)                                  |                                       |                                       |

|                  | Independent watchdog timer                                 | Operating                             | Operating possible                    |

|                  | (IWDT: RX62T, IWDTa: RX66T)                                |                                       |                                       |

|                  | Port output enable                                         | Operating possible                    | Operating possible                    |

|                  | (POE3: RX62T, POE3B: RX66T)                                |                                       |                                       |

|                  | 8-bit timer (unit 0, unit 1) (TMR)                         | _                                     | Operating possible                    |

|                  | Voltage detection circuit (LVDA)                           | Operating                             | Operating possible                    |

|                  | Power-on reset circuit                                     | Operating                             | Operating                             |

|                  | Peripheral modules                                         | Operating                             | Operating possible                    |

|                  | I/O ports                                                  | Operating                             | Operating                             |

| All-module clock | Transition method                                          | Control register                      | Control register                      |

| stop mode        |                                                            | + instruction                         | + instruction                         |

|                  | Method of cancellation other than reset                    | Interrupt                             | Interrupt                             |

|                  | State after cancellation                                   | Program execution state               | Program execution state               |

|                  |                                                            | (interrupt processing)                | (interrupt processing)                |

|                  | Main clock oscillator                                      | Operating                             | Operating possible                    |

|                  | High-speed on-chip oscillator                              |                                       | Operating possible                    |

|                  | Low-speed on-chip oscillator                               | _                                     | Operating possible                    |

|                  | IWDT-dedicated on-chip oscillator                          | Operating                             | Operating possible                    |

|                  | PLL                                                        | Operating                             | Operating possible                    |

|                  | CPU                                                        | Stopped (retained)                    | Stopped (retained)                    |

|                  | On-chip RAM                                                | Stopped (retained)                    | Stopped (retained)                    |

|                  | (0000 0000h to 0000 3FFFh): RX62T                          | -1000                                 |                                       |

|                  | RAM and ECCRAM: RX66T                                      | 0(1) 1 (1) 1                          | 0(1) (1) (1)                          |

|                  | Flash memory                                               | Stopped (retained)                    | Stopped (retained)                    |

|                  | USB 2.0 Host/Function module (USBb)                        | <del></del>                           | Stopped                               |

|                  | Entering and Exiting Low Power          |                        |                        |

|------------------|-----------------------------------------|------------------------|------------------------|

|                  | Consumption Modes and Operating         |                        |                        |

| Mode             | States                                  | RX62T                  | RX66T                  |

| All-module clock | Watchdog timer                          | Operating              | Stopped (retained)     |

| stop mode        | (WDT: RX62T, WDTA: RX66T)               |                        |                        |

|                  | Independent watchdog timer              | Operating              | Operating possible     |

|                  | (IWDT: RX62T, IWDTa: RX66T)             |                        |                        |

|                  | Port output enable                      | Operating possible     | Operating possible*1   |

|                  | (POE3: RX62T, POE3B: RX66T)             |                        |                        |

|                  | 8-bit timer (unit 0, unit 1) (TMR)      |                        | Operating possible     |

|                  | Voltage detection circuit (LVDA)        | Operating              | Operating possible     |

|                  | Power-on reset circuit                  | Operating              | Operating              |

|                  | Peripheral modules                      | Stopped (retained)     | Stopped (retained)     |

|                  | I/O ports                               | Retained               | Retained               |

| Software         | Transition method                       | Control register       | Control register       |

| standby mode     |                                         | + instruction          | + instruction          |

|                  | Method of cancellation other than reset | Interrupt              | Interrupt              |

|                  | State after cancellation                | Program execution      | Program execution      |

|                  |                                         | state                  | state                  |

|                  |                                         | (interrupt processing) | (interrupt processing) |

|                  | Main clock oscillator                   | Stopped                | Stopped                |

|                  | High-speed on-chip oscillator           |                        | Stopped                |

|                  | Low-speed on-chip oscillator            |                        | Stopped                |

|                  | IWDT-dedicated on-chip oscillator       | Stopped                | Operating possible     |

|                  | PLL                                     | Stopped                | Stopped                |

|                  | CPU                                     | Stopped (retained)     | Stopped (retained)     |

|                  | On-chip RAM                             | Stopped (retained)     | Stopped (retained)     |

|                  | (0000 0000h to 0000 3FFFh): RX62T       |                        |                        |

|                  | RAM and ECCRAM: RX66T                   |                        |                        |

|                  | Flash memory                            | Stopped (retained)     | Stopped (retained)     |

|                  | USB 2.0 Host/Function module (USBb)     | _                      | Stopped                |

|                  | Watchdog timer                          | Stopped (retained)     | Stopped (retained)     |

|                  | (WDT: RX62T, WDTA: RX66T)               |                        |                        |

|                  | Independent watchdog timer              | Stopped (retained)     | Operating possible     |

|                  | (IWDT: RX62T, IWDTa: RX66T)             |                        |                        |

|                  | Port output enable                      | Stopped (retained)     | Stopped (retained)     |

|                  | (POE3: RX62T, POE3B: RX66T)             |                        |                        |

|                  | 8-bit timer (unit 0, unit 1) (TMR)      | _                      | Stopped (retained)     |

|                  | Voltage detection circuit (LVDA)        | Operating              | Operating possible     |

|                  | Power-on reset circuit                  | Operating              | Operating              |

|                  | Peripheral modules                      | Stopped (retained)     | Stopped (retained)     |