# APPLICATION NOTE

Implementing Polyphase Filtering with the HSP50110 (DQT), HSP50210 (DCL) and the HSP43168 (DFF)

AN9661 Rev.1.00 Jan 1998

# Introduction

intersil

Polyphase resampling filters are often used for timing adjustments in bit synchronizer loops. They are most commonly used at high baud rates where the sample rate to baud rate ratio ( $f_S/R_{Baud}$ ) is low. The HSP50110 Digital Quadrature Tuner (DQT) and HSP50210 Digital Costas Loop (DCL) chips support NCO driven polyphase resampling filtering when the HSP43168 Dual FIR Filter (DFF) is inserted between them. This Application Note will address use of the DQT, DFF and DCL in the polyphase filtering configuration.

# Polyphase Filtering Overview

In polyphase resamplers, the process ce, followed by a decimation to the desired lower rate. In practice, the process is done in a single step by changing the filter coefficients.

For example, in a 3/5 resampler, the input is interpolated by three using three sets of coefficient phases 0, 1, and 2. The interpolated signal is then decimated by 5, discarding 4/5 of the phases. The two steps are combined by computing three outputs for every five inputs. The resulting phases are:

$IOUT_0 = 0_A;$  $IOUT_1 = 2_B;$

$IOUT_1 = 1_D;$

$IOUT_2 = 0_F;$

$IOUT_3 = 0_F;$

as shown in Table 1. One can see by inspection, that the same result can be accomplished by providing unique sets of coefficients and applying the appropriate filter coefficient set to the input data at the desired output rate. A unique coefficient set is required for every interpolated phase of the data, in this example - 3.

# DQT/DCL Resampling Capabilities

The DQT/DCL have four design elements which enable polyphase filtering to be accomplished:

- 1. A resampling NCO with carry output.

- 2. A latched resampling NCO phase word: SPH(4:0).

- 3. A programmable clock counter with carry output.

- 4. A strobe, SSTRB, latched synchronous to both the Resampler NCO carry and the programmable clock counter carry.

In the DQT/CDL implementation, the resampling ratio is controlled by the resampling NCO. The ratio can be both irrational and variable. The DQT is fixed (controlled by a counter) at an output sample rate faster than the desired rate. The resampling NCO and the DFF are used to choose when to compute the next output and which interpolation phase to use. The DFF can store up to 32 filter phases (coefficient sets). This gives a timing resolution of  $\sim$ 3% of a symbol time.

TABLE 1. INTERPOLATE BY 3 DECIMATE BY 5

| INPUT<br>DATA  | INTERPOLATE BY 3<br>DATA | DECIMATE BY 5<br>DATA |

|----------------|--------------------------|-----------------------|

| ١ <sub>A</sub> | 0 <sub>A</sub>           | IOUT <sub>0</sub>     |

|                | 1 <sub>A</sub>           |                       |

|                | 2 <sub>A</sub>           |                       |

| Ι <sub>Β</sub> | 0 <sub>B</sub>           |                       |

|                | 1 <sub>B</sub>           |                       |

|                | 2 <sub>B</sub>           | IOUT <sub>1</sub>     |

| ΙC             | 0 <sub>C</sub>           |                       |

|                | 1 <sub>C</sub>           |                       |

|                | 2 <sub>C</sub>           |                       |

| ۱ <sub>D</sub> | 0 <sub>D</sub>           |                       |

|                | 1 <sub>D</sub>           | IOUT <sub>2</sub>     |

|                | 2 <sub>D</sub>           |                       |

| ١ <sub>E</sub> | 0 <sub>E</sub>           |                       |

|                | 1 <sub>E</sub>           |                       |

|                | 2 <sub>E</sub>           |                       |

| ١ <sub>F</sub> | 0 <sub>F</sub>           | IOUT <sub>3</sub>     |

The DQT resampling NCO is programmed for the desired output sample rate. When the NCO rolls over, it sets a flag internally so that the NCO's phase, SPH(4:0), is sampled and the SSTRB signal is asserted aligned with the next output sample. The SSTRB signal indicates that a FIR computation is required. The SPH(4:0) signals hold the NCO phase at the output sample time, indicating which filter interpolation coefficient set to use.

# Polyphase Filter Design

The coefficients for the interpolation phases are generated by designing the filter at the interpolated rate (32x the input sample rate since there are five bits of phase represented in SPH(4:0)) with desired passband at <1X in input sample rate. With the DFF (without alternating the FWD and RVRS data), the prototype filter would have (32 phases x 8 taps) 256 taps. These taps are divided into the 32 filter phases by taking every 32nd sample and storing the result as coefficient sets 0 through 31. The first coefficient set would be C0, C32, C64, C96, C128, C160, C193, and C224. The last coefficient set would be C31, C63, C95, C127, C159, C192, C223, and C255. Note: Preadders in the DFF cannot be used since interpolation phase coefficients are asymmetric.

Decimation can be used if fewer interpolation phases are used for example 16 coefficient phases can be realized by decimating by two. Because the resampling filter has only an 8 sample span (4 symbol), the short span yields relatively gradual transition band roll off, making it a poor shaping filter.

# *Implementing a Resampling Filter Using the DQT, DCL and the DFF*

There are several configurations for implementing polyphase filtering using the HSP50110 (DQT) and HSP50210 (DCL) with external FIR Filters. Three distinct operational cases which are related to the selected input mode of the input controller of the DQT are: Normal, Gated, and Interpolated. This Application Note addresses only the Normal Input Mode, which has the ENI input to the DQT tied low. Bit position 1 of Control Address = 4 should be set high (1), selecting the gated mode. Hardwiring ENI will continuously gate the input.

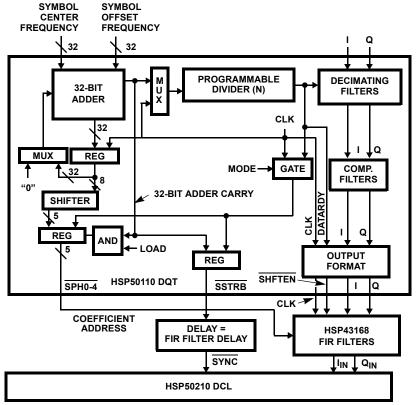

Consider the implementation shown in Figure 1. The SSTRB and the SPH0-4 are used to gate the output of the filter address, the filter and the coefficients respectively. Note that the SSTRB must be delayed an amount equivalent to the filter, to properly gate the filter output into the HSP50210 via the SYNC input signal. Using the fine phase address bits in SPH0-4, 32 filter phases (coefficient sets) can be realized.

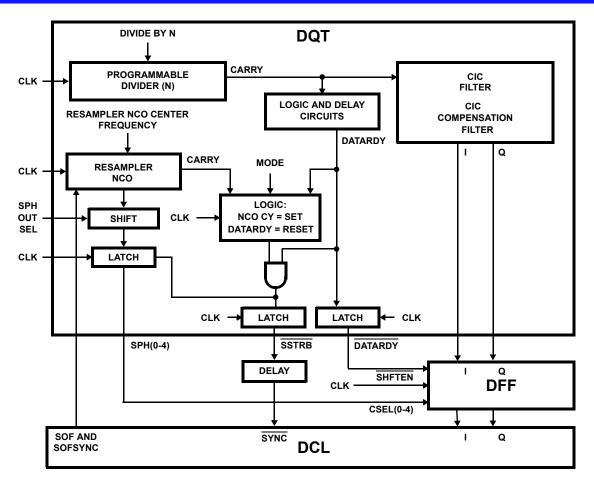

The clocking and control of the FIR using CLK, SSTRB, SYNC, DATARDY and SPH0-4 becomes critical. Figure 2 outlines the configuration required. It is very important to understand the

relationship between the various DQT clock and control outputs.

# CLK, the Programmable Divider, and the Re-Sampler NCO

The Programmable Divider must be configured to have CLK (the DQT input sample clock) as the clock source, rather than the Re-Sampler NCO carry out. To select CLK as the source, BIT-18 of DESTINATION ADDRESS 5 must be set to "1". The Programmable Divider (Destination Address 5 Bit 6 to 17) is set to a value of  $2^{n}$ , where n = 0, 1, 2, or 3. This generates a CIC Filter Clock that is CLK, CLK/2, CLK/4 or CLK/8, respectively. This clock will be gated to become the DATARDY signal, and will be used to gate the data into the external FIR Filter. This selection of the Programmable Divider determines the SPH\_OUT\_SEL settings for the shifter or the Re-Sampler Phase output bits. Table 2 details the required settings.

#### TABLE 2. DIVIDER AND PHASE SHIFT SETTINGS

| PROGRAMMABLE DIVIDER | SHIFTER SETTINGS |  |

|----------------------|------------------|--|

| 0H                   | 11               |  |

| 1H                   | 10               |  |

| 3H                   | 01               |  |

| 7H                   | 00               |  |

Note that when the CIC Filter is clocked at CLK rate, no shifting occurs. Similarly, when the CIC Filter is clocked at CLK/8 rate, the shifter selects the phase bits fourth from the top as the MSB.

FIGURE 1. SIGNAL GENERATION FOR POLYPHASE FILTERING WITH HSP50110/HSP50210

FIGURE 2. CLOCK AND CONTROL CONNECTIONS FOR POLYPHASE FILTERING

We desire finer phase resolution of a single decimated sample time. The Programmable Divider output, which is DQT CIC and DQT CIC compensation filter clock, is one positive (programmable positive or pegative) pulse the width of one

(programmable positive or negative) pulse the width of one input sample clock period.

Note that the input sample clock (CLK) is the clock that should be used to clock the FIR Filter input. The DATARDY signal will be used to enable the FIR Filter input data sampling at the decimated rate.

### The SSTRB Signal and the Re-Sampler Phase Output

The Re-Sampler NCO is programmed to the desired sample frequency of the DCL input. It is not connected to any clock hardware in the DQT. This NCO provides a carry output, which identifies the zero phase location. Additionally, 5 bits of phase resolution are provided. The SSTRB signal is the gated version of the carry out of the Re-Sampler NCO.

There are two selectable modes of operation for the SSTRB signal. The first mode is an asynchronous continuous mode, where the carry out is passed directly out of the chip without concern for the timing of the programmable counter. The carry

out is updated with every CLK rising edge. Do not use the asynchronous continuous mode for this application.

The second mode synchronizes the carry output pulse with the rising clock edge out of the programmable counter. Program BIT POSITION 13 of DESTINATION ADDRESS = 6 to be "0". This gating will "synchronize" the SSTRB and the 5 bits of sampler phase to the DATARDY signal. The synchronization occurs during gating and the gate will occasionally prevent the SSTRB and phase signals from their expected location, because they did not occur aligned with the DATARDY signal (during that output sample period).

The frequency of the Re-Sampler NCO carry out is equal to the programmed Re-Sampler NCO Center Frequency value multiplied by the frequency of CLK, scaled to 32 bits of resolution. If there is a Symbol Offset Frequency offset term, the sum of the offset and the center frequencies is multiplied by the frequency of CLK, and scaled to 32-bit resolution. This is detailed in Equation 1.

| FCO = $f_S \propto (SCF + SOF)/2^{32}$ | (EQ. 1) |

|----------------------------------------|---------|

|----------------------------------------|---------|

where FCO = the frequency of the Re-Sampler NCO carry out;  $f_S$  = the DQT input sampling frequency (CLK); SCF = the Sampler Center Frequency; SOF = Sampler Offset Frequency.

#### NOTES:

- 1. Because the SCF and SOF are both 32-bit words, the maximum value for the parenthetical expression is (FFFFFFF + FFFFFF)/ $2^{32} = 2$ , which yields an erroneous value of greater than one for the multiplier of the sampling frequency  $f_S$ . This will cause the NCO to "rollover". If the sum of these two values (SCF + SOF) are kept less than  $2^{32}$ , rollover will not be an issue.

- If the value of SCF is a multiple of 2, then there will be no jitter on the carry out of the NCO (and thus, no jitter on the decimation filter clock or the DATARDY signal) so long as the SOF is zero. But as SOF adjusts the phase of the NCO, jitter on the order of one NCO clock will be introduced due to the non-integer value of the sampling frequency multiplier (SCF + SOF)/ 2<sup>32</sup>.

- 3. If the value of SCF is not a multiple of 2, then there will be jitter on carry out of the NCO on the order of one NCO clock due to the non-integer value of the sampling frequency multiplier (SCF)/2<sup>32</sup>. As the SOF signal adjusts the phase of the NCO, the jitter will remain, except on those rare moments when the sum of SOF and SCF is a multiple of 2.

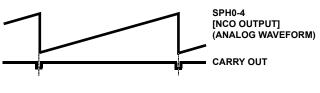

Figure 3 shows the relationship to the NCO output values and the frequency of the NCO carry out signal. SPH (0-5) are 5 MSB's selected from the top 8 bits of the NCO output word. It is these bits that will be used to provide finer sampler phase resolution to address the coefficient sets in the FIR Filter. A programmable shifter selects which 5 of the 8 MSB's are used as the sampler phase output. Up to thirty two symbol phase values can be achieved with these 5 bits. The shifter scaling retains the 32 state resolution for most NCO frequencies. These 5 bits should be connected to the FIR Filter coefficient address lines.

FIGURE 3. THE CARRY OUT SIGNAL RELATIONSHIP TO RESAMPLER PHASE BITS

# The External FIR Filter

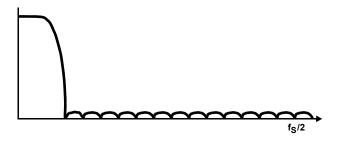

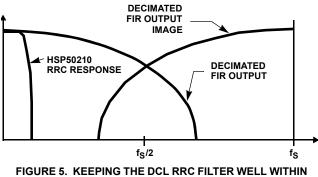

A FIR Filter is used to provide for the resampling of the DQT output with timing associated with the Re-Sampler NCO frequency. Figure 4 shows a typical filter response for this FIR Filter. The filter is designed as an Interpolate by 32/Decimate by n filter. The Interpolate by 32 is a "virtual" interpolation, since the part is being clocked at CLK rate, but enabled at the DATARDY rate. The FIR decimation rate is with respect to the DATARDY enable rate, which is the rate at which the FIR shifter is enabled. As shown in Figure 5, the filter must be designed to ensure that the RRC filter in the DCL chip is well within the flat passband of the FIR Filter and not corrupted by aliasing. The DFF will aid in, but not be, the primary shaping filter in the receive path.

FIGURE 4. A TYPICAL DATA FILTER FOR THE FIR FILTER STRUCTURE

FIGURE 5. KEEPING THE DCL RRC FILTER WELL WITHIN THE FLAT PASSBAND

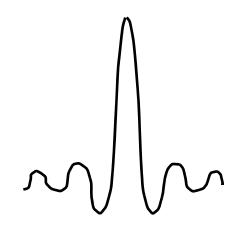

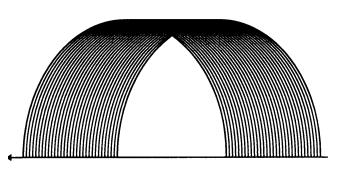

The HSP43168 dual FIR Filter provides the capability to provide both the I and Q filters in a single chip if a 8 tap symmetric filter meets the customer requirements. Each of the 8 taps is used with 32 coefficient sets to yield a total filter of up to  $8 \times 32 = 256$  taps. Another way to look at this is that this provides 8 filter taps per phase. Each of the 32 filter coefficient sets should be programmed with coefficients for different phases of the response. A typical single phase filter response is shown in Figure 6. This response becomes just one of 32 phase responses that as a composite will represent the filter. The main lobe response of composite filter, with 32 phases, is shown in Figure 7.

FIGURE 6. A TYPICAL SINGLE PHASE FILTER RESPONSE

FIGURE 7. THE "MAIN LOBE" COEFFICIENT FILTER RESPONSE FOR A 32 PHASE FILTER

# A Typical Single Phase Filter Response

The DCL will accept the output of the FIR Filter at the FIR decimated rate. These inputs will be enabled by the SYNC input, which is the SSTRB signal delayed by exact processing delay of the FIR Filter. Note that the SSTRB represents the "zero or start" phase sample of the 32 phases of the resampled rate clock. The designer must provide the input processing clock. This processing clock can be the CLK signal from the DQT, since the DCL inputs are enabled by SYNC. Thus the effective sampling rate of the DCL is determined by the SSTRB (SYNC) signal. The symbol loop filter output of the DCL, SOF and SOFSYNC, should be routed to the DCL Resampler inputs of the same name.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338