AN-1074 6-Channel Power Lines Sequencer

> Author: Yurii Shchebel Date: June 11, 2015

#### Introduction

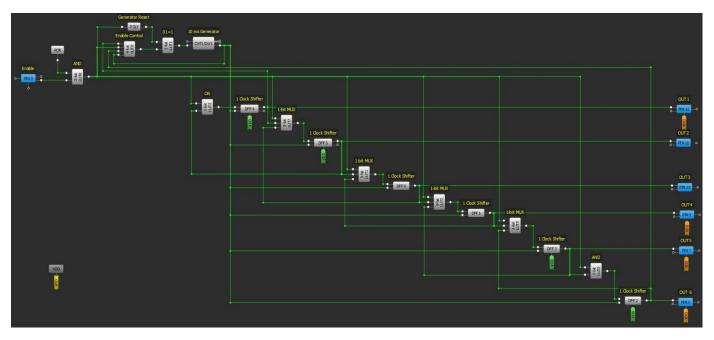

This application note describes the design of a 6 channel power lines sequencer. It can be used for switching supply rails on/off in a predetermined order with constant or variable delays.

### Power Lines Sequencer circuit design

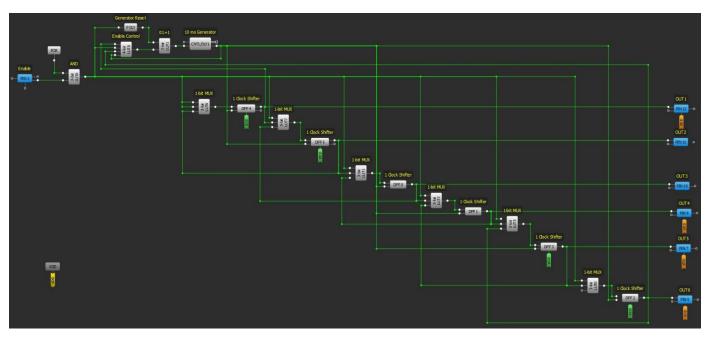

To design this sequencer it is necessary to construct a generator which sets the delay time, and DFFs and LUTs are used to shift the signal edges. Using blocks combinations "3-bit LUT + DFF" (cells) it is possible to sequence as many lines as the number of cells you have available. Cell configuration is shown in Figure 2, where N-1 = previous cell, N+1 = next cell.

The Generator block is made using 4-bit LUT0, CNT1/DLY1, 2-bit LUT1 and P DLY.

Blocks configurations are presented in figures 1-9.

| DFF | nable<br><sup>=</sup> Q <sub>N</sub><br>= Q <sub>N</sub> |       | 1-bt M | - <u>-</u> | Clock   | 1 Clock Shifter        | OUTN             |    |

|-----|----------------------------------------------------------|-------|--------|------------|---------|------------------------|------------------|----|

|     |                                                          | 3-bit | LUT1   |            |         | 2-bit LU               | T4/DFF/LATCH0    |    |

| IN3 | IN2                                                      | IN1   | IN0    | 0          | UT      | Type:                  | DFF / LATCH      | ¢  |

| 0   | 0                                                        | 0     | 0      | 0          | \$      | 1700.                  |                  |    |

| 0   | 0                                                        | 0     | 1      | 1          | \$      | Mode:                  | DFF              | \$ |

| 0   | 0                                                        | 1     | 0      | 0          | <b></b> |                        | UFF              |    |

| 0   | 0                                                        | 1     | 1      | 1          | \$      | nSET/nRESET<br>option: | None             | \$ |

| 0   | 1                                                        | 0     | 0      | 0          | \$      | Initial                | 1                | \$ |

| 0   | 1                                                        | 0     | 1      | 0          | <b></b> | polarity:              | Low              | •  |

| 0   | 1                                                        | 1     | 0      | 1          | •       | Q output<br>polarity:  | Non-inverted (Q) | \$ |

|     | 1                                                        | 1     | 1      | 1          | \$      | portant.               |                  |    |

## Figure 2. 3-bit LUT + DFF "cell" connections and configuration

|              | P DLY              |    |

|--------------|--------------------|----|

| Mode:        | Both edge detector | \$ |

| Delay:       | 4 Cells            | \$ |

| Output mode: | Non-delayed        | \$ |

Figure 3. P DLY configuration

Figure 1. Power Lines Sequencer schematic

### **6-Channel Power Lines Sequencer**

2-bit LUT0

|                                       | PIN 3                   |

|---------------------------------------|-------------------------|

| I/O selection:                        | Digital input           |

| Input mode:<br>OE = 0<br>Output mode: | Digital in without Sc 🗢 |

| Output mode:<br>OE = 1                | None                    |

| Resistor:                             | Floating \$             |

| Resistor value:                       | Floating                |

|                                       | PIN 5                   |

| I/O selection:                        | Digital output          |

| Input mode:<br>OE = 0                 | None 🗘                  |

| Output mode:<br>OE = 1                | 1x push pull            |

| Resistor:                             | Floating                |

| Resistor value:                       | Floating                |

|                                       | PIN 7                   |

| I/O selection:                        | Digital output          |

| Input mode:<br>OE = 0                 | None 🗘                  |

| Output mode:<br>OE = 1                | 1x push pull            |

| Resistor:                             | Floating \$             |

| Resistor value:                       | Floating \$             |

|                                       | PIN 9                   |

| I/O selection:                        | Digital output          |

| Input mode:<br>OE = 0                 | None 🗘                  |

| Output mode:<br>OE = 1                | 1x push pull            |

| Resistor:                             | [Floating 4]            |

| Resistor value:                       | Floating 🔷              |

|                                       | PIN 10                  |

| I/0 selection:                        | Digital output          |

| Input mode:<br>OE = 0                 | None 🗘                  |

| Output mode:<br>OE = 1                | 1x push pull            |

| Resistor:                             | Floating \$             |

| Resistor value:                       | Floating \$             |

|                                       | PIN 11                  |

| I/0 selection:                        | Digital output          |

| Input mode:<br>OE = 0                 | None 😫                  |

| Output mode:<br>OE = 1                | 1x push pull            |

|                                       | PIN 12                  |

| I/O selection:                        | Digital output          |

| Input mode:                           | None 😫                  |

| OE = 0<br>Output mode:<br>OE = 1      | 1x push pull            |

| Resistor:                             | Floating                |

| Resistor value:                       | Floating \$             |

| Resistor value:                       | ribbung V               |

| IN3  | IN2    | IN1     | INO   |      | OUT     |    |

|------|--------|---------|-------|------|---------|----|

| 0    | 0      | 0       | 0     | 0    |         | \$ |

| 0    | 0      | 0       | 1     | 0    |         | \$ |

| 0    | 0      | 1       | 0     | 0    |         | ¢  |

| 0    | 0      | 1       | 1     | 1    |         | \$ |

|      | 4      | -bit LU | T0/PG | EN   |         |    |

| ype: |        | l       | .UT   | _    |         | ¢  |

| IN3  | IN2    | IN1     | IN0   |      | OUT     |    |

| 0    | 0      | 0       | 0     | 0    |         | ¢  |

| 0    | 0      | 0       | 1     | 0    |         | \$ |

| 0    | 0      | 1       | 0     | 0    |         | ¢  |

| 0    | 0      | 1       | 1     | 0    |         | \$ |

| 0    | 1      | 0       | 0     | 1    |         | ¢  |

| 0    | 1      | 0       | 1     | 0    | T.      | \$ |

| 0    | 1      | 1       | 0     | 0    |         | ¢  |

| 0    | 1      | 1       | 1     | 0    |         | \$ |

| 1    | 0      | 0       | 0     | 1    |         | ¢  |

| 1    | 0      | 0       | 1     | 0    |         | \$ |

| 1    | 0      | 1       | 0     | 1    |         | ¢  |

| 1    | 0      | 1       | 1     | 0    | 13      | ¢  |

| 1    | 1      | 0       | 0     | 1    |         | ¢  |

| 1    | 1      | 0       | 1     | 0    | 13      | ¢  |

| 1    | 1      | 1       | 0     | 0    |         | ¢  |

| 1    | 1      | 1       | 1     | 0    |         | ¢  |

|      |        | 2-bit   | LUT1  |      |         |    |

| IN3  | IN2    | IN1     | IN0   | L    | OUT     |    |

| 0    | 0      | 0       | 0     | 0    |         | ¢  |

| 0    | 0      | 0       | 1     | 1    |         | ¢  |

| 0    | 0      | 1       | 0     | 0    |         | ¢  |

| 0    | 0      | 1       | 1     | 0    | 1       | ¢  |

|      | 3-bi   | t LUT6  | /Pipe | Dela | y       |    |

| ype: |        | (I      | .UT   |      |         | ¢  |

| IN3  | IN2    | IN1     | IN0   | 1    | OUT     |    |

| 0    | 0      | 0       | 0     | 0    |         | ¢  |

| 0    | 0      | 0       | 1     | 1    |         | ¢  |

| 0    | 0      | 1       | 0     | 0    |         | ¢  |

| 0    | 0      | 1       | 1     | 1    |         | ¢  |

| 0    | 1      | 0       | 0     | 0    |         | ¢  |

| 0    | 1      | 0       | 1     | 0    |         | ¢  |

| 0    | 1      | 1       | 0     | 1    |         | ¢  |

| 0    | 1      | 1       | 1     | 1    |         | ¢  |

| 3-b  | it LUT | 7/8-bit | CNT3/ | DLY  | 3/F SM1 |    |

| ype: |        | l       | .UT   | _    |         | ¢  |

| IN3  | IN2    | IN1     | INO   |      | OUT     |    |

| 0    | 0      | 0       | 0     | 0    |         | ¢  |

| 0    | 0      | 0       | 1     | 1    |         | \$ |

| 0    | 0      | 1       | 0     | 0    |         | \$ |

| 0    | 0      | 1       | 1     | 1    |         | \$ |

| 0    | 1      | 0       | 0     | 0    |         | \$ |

| 0    | 1      | 0       | 1     | 0    |         | \$ |

| V    |        |         |       |      |         |    |

| 0    | 1      | 1       | 0     | 1    |         | ¢  |

Figure 4. PINs configuration

Figure 5. LUTs configuration

### **6-Channel Power Lines Sequencer**

|     |     | 5-01  | LUT1 |        |     |

|-----|-----|-------|------|--------|-----|

| IN3 | IN2 | IN1   | INO  |        | OUT |

| 0   | 0   | 0     | 0    | 0      |     |

| 0   | 0   | 0     | 1    | 1      |     |

| 0   | 0   | 1     | 0    | 0      |     |

| 0   | 0   | 1     | 1    | 1      | :   |

| 0   | 1   | 0     | 0    | 0      |     |

| 0   | 1   | 0     | 1    | 0      | :   |

| 0   | 1   | 1     | 0    | 1      |     |

| 0   | 1   | 1     | 1    | 1      |     |

|     |     | 3-bit | LUT2 | i<br>N |     |

| IN3 | IN2 | IN1   | INO  |        | OUT |

| 0   | 0   | 0     | 0    | 0      |     |

| 0   | 0   | 0     | 1    | 1      | 1   |

| 0   | 0   | 1     | 0    | 0      |     |

| 0   | 0   | 1     | 1    | 1      | 1   |

| 0   | 1   | 0     | 0    | 0      |     |

| 0   | 1   | 0     | 1    | 0      | 1   |

| 0   | 1   | 1     | 0    | 1      |     |

| 0   | 1   | 1     | 1    | 1      | 1   |

|     |     | 3-bit | LUT3 |        |     |

| IN3 | IN2 | IN1   | IN0  |        | OUT |

| 0   | 0   | 0     | 0    | 0      |     |

| 0   | 0   | 0     | 1    | 1      |     |

| 0   | 0   | 1     | 0    | 0      |     |

| 0   | 0   | 1     | 1    | 1      |     |

| 0   | 1   | 0     | 0    | 0      |     |

| 0   | 1   | 0     | 1    | 0      |     |

| 0   | 1   | 1     | 0    | 1      |     |

| 0   | 1   | 1     | 1    | 1      |     |

|     |     | 3-bit | LUTO |        |     |

| IN3 | IN2 | IN1   | IN0  |        | OUT |

| 0   | 0   | 0     | 0    | 0      |     |

| 0   | 0   | 0     | 1    | 1      |     |

| 0   | 0   | 1     | 0    | 0      |     |

| 0   | 0   | 1     | 1    | 1      |     |

| 0   | 1   | 0     | 0    | 0      |     |

| 0   | 1   | 0     | 1    | 0      |     |

| 0   | 1   | 1     | 0    | 1      |     |

|     | 1   | 1     | 1    | 1      | :   |

Figure 6. LUTs configuration

| Di                     | F/LATCH4         |    |

|------------------------|------------------|----|

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | nRESET           | \$ |

| Initial<br>polarity:   | Low              | \$ |

| Q output<br>polarity:  | Non-inverted (Q) | \$ |

| Di                     | F/LATCH5         |    |

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | nRESET           | \$ |

| Initial<br>polarity:   | Low              | \$ |

| Q output<br>polarity:  | Non-inverted (Q) | \$ |

| 2-bit LU               | T4/DFF/LATCH0    |    |

| Туре:                  | DFF / LATCH      | \$ |

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | None             | \$ |

| Initial<br>polarity:   | Low              | \$ |

| Q output<br>polarity:  | Non-inverted (Q) | \$ |

| 2-bit LU               | T5/DFF/LATCH1    |    |

| Туре:                  | DFF / LATCH      | \$ |

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | None             | \$ |

| Initial<br>polarity:   | Low              | \$ |

| Q output<br>polarity:  | Non-inverted (Q) | \$ |

| 3-bit LU               | T5/DFF/LATCH3    |    |

| Түре:                  | DFF / LATCH      | \$ |

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | nRESET           | \$ |

| Initial<br>polarity:   | Low              | \$ |

| Q output<br>polarity:  | Non-inverted (Q) | \$ |

| 3-bit LU               | T4/DFF/LATCH2    |    |

| Туре:                  | DFF / LATCH      | \$ |

| Mode:                  | DFF              | \$ |

| nSET/nRESET<br>option: | nRESET           | \$ |

|                        |                  | 1  |

| Initial polarity:      | Low              | \$ |

Figure 7. DFFs configuration

|                                   | OSC        |      |

|-----------------------------------|------------|------|

| LF OSC RC OS                      | C RING C   | SC   |

| RC OSC power<br>mode:             | Auto power | on 🗘 |

| RC 05C<br>frequency:              | 25.00 kHz  | \$   |

| Current source<br>always turn on: | Disable    | ¢    |

| RC matrix<br>power down:          | Disable    | ¢    |

| RC clock<br>predivider by:        | 1          | \$   |

| RC clock to<br>matrix input:      | Enable     | \$   |

| 'OUTO' second<br>divider by:      | 1          | \$   |

| Clock selector:                   | RC OSC     | \$   |

#### Figure 8. ADC properties

| 8-bi                  | t CNT1/DLY1                   |                     |

|-----------------------|-------------------------------|---------------------|

| Mode:                 | Delay                         | \$                  |

| Counter data:         | 248                           | \$                  |

| Delay time:           | (Range: 1 - 255<br>10.0200 ms | )<br><u>Formula</u> |

| Edge select:          | Rising                        | \$                  |

| Q mode:               | Reset                         | \$                  |

| DFF bypass<br>enable: | None                          | \$                  |

| Co                    | onnections                    |                     |

| FSM data:             | None                          | \$                  |

| Clock:                | CLK                           | \$                  |

| Clock source:         | OSC Freq.                     |                     |

Figure 9. DLY1 configuration

# Power Lines Sequencer circuit analysis

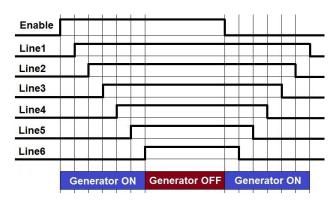

As we know, a DFF can shift an input signal (D input) by 1 clock. The point is to form this input signal using existing signals (Enable, Previous line, Next line), which are applied to 3-bit LUT.

This 3-bit LUT operates as a MUX and outputs N-1 signal when Enable is HIGH, and N+1 signal when Enable is LOW (see figure 10).

4-bit LUT0 is used to turn on/off the generator when it is necessary to decrease current consumption. Its output will invert the IN0 input signal until the lines are all HIGH or all LOW (see figure 10). 2-bit LUT1 repeats the 4-bit LUT0 value when P DLY output is LOW. When the pulse comes from PDLY block, 2bit LUT1 output goes LOW. This will reset the generator on the rising or falling edge of Enable signal, and that provides proper delay for the last (6<sup>th</sup>) line's falling edge (figure 11).

Figure 10. Power Lines Sequencer theoretical timing diagram

### 6-Channel Power Lines Sequencer

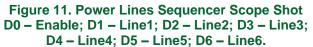

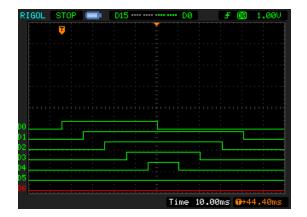

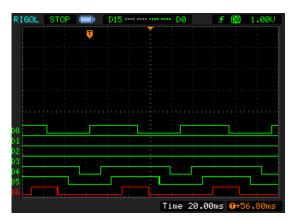

Figure 12. Power Lines Sequencer Scope Shot D0 – Enable; D1 – Line1; D2 – Line2; D3 – Line3; D4 – Line4; D5 – Line5; D6 – Line6.

In the case when Enable goes low before some lines are driven high, these lines will stay LOW (see figure 12).

In the case Enable signal comes before some lines are driven LOW, these lines will stay HIGH (see figure 13).

No additional blocks are required to provide these functions. It is realized only with 3-bit LUTs and DFFs, described earlier.

Figure 13. Power Lines Sequencer theoretical timing diagram D0 – Enable; D1 – Line1; D2 – Line2; D3 – Line3; D4 – Line4; D5 – Line5; D6 – Line6.

Also it is possible to make a circuit simplification (Figure 14). That can be done for the first and last 3bit LUT + DFF cells. In the first case, Enable signal and "Previous line" have the same timing. So 3-bit LUT can be replaced with a 2-bit LUT, configured as an OR gate (see figure 15).

Figure 14. Simplified Power Lines Sequencer circuit design

### **6-Channel Power Lines Sequencer**

As for the last line, there is no Next line and one of the 3-bit LUT's inputs stays LOW all the time. This LUT can be replaced with a 2-bit LUT (AND gate) as well (figure 15).

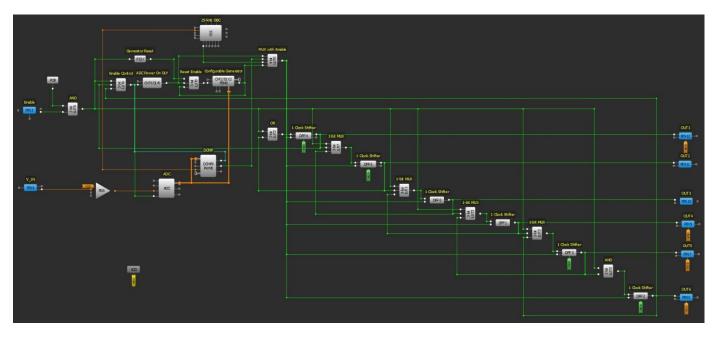

# Power Lines Sequencer with variable delay time

Using a state machine instead of a simple Delay block makes it possible to change a delay time by loading counter data from the ADC. The Power lines sequencer with variable delay time circuit is presented in figure 17.

Configuration of the LUT + DFF cells remains the same, but there are some changes in the generator operation process and some blocks are added (see figure 17). The corresponding Blocks configuration is shown in figures 18-22.

|     |     | 2-bit | LUT2 |   |    |

|-----|-----|-------|------|---|----|

| IN3 | IN2 | IN1   | INO  | 0 | UT |

| 0   | 0   | 0     | 0    | 0 | \$ |

| 0   | 0   | 0     | 1    | 1 | \$ |

| 0   | 0   | 1     | 0    | 1 | \$ |

| 0   | 0   | 1     | 1    | 1 | \$ |

|     |     | 2-bit | LUT3 |   |    |

| IN3 | IN2 | IN1   | INO  | 0 | UT |

| 0   | 0   | 0     | 0    | 0 | \$ |

| 0   | 0   | 0     | 1    | 0 | \$ |

| 0   | 0   | 1     | 0    | 0 | +  |

| 0   | 0   | 1     | 1    | 1 | \$ |

#### Figure 15. 2-bit LUTs configuration

|                        | PIN 6               |    |

|------------------------|---------------------|----|

| I/O selection:         | Analog input/output | \$ |

| Input mode:<br>OE = 0  | Analog input        | \$ |

| Output mode:<br>OE = 1 | Analog output       | \$ |

| Resistor:              | Floating            | \$ |

| Resistor value:        | Floating            | \$ |

#### Figure 16. PIN6 properties

Figure 17. Schematic of Power Lines Sequencer with variable delay time

### **6-Channel Power Lines Sequencer**

|                                  | ADC                |        |

|----------------------------------|--------------------|--------|

| Mode:                            | Single-end         | \$     |

| Vref:                            | Bandgap (1 V)      | \$     |

| Force analog<br>part:            | Disable            | \$     |

| Analog part<br>speed selection   | 5 kHz              | •      |

| Clock for ADC<br>divide by:      | 1                  | \$     |

| ADC data sync<br>with SPI clock: | Disable            | \$     |

| PWM & ADC<br>clock source :      | RC OSC             | •      |

| Sample speed:                    | 97.6562 Hz         | ormula |

| Co                               | nnections          |        |

| Serial data:                     | Disable (Matrix <- | > \$   |

#### Figure 19. ADC properties

|                      | PGA        |    |

|----------------------|------------|----|

| Power on<br>signal:  | Power down | ¢  |

| Gain:                | x1         | \$ |

| ADC mode:            | Single-end | \$ |

| Con                  | nections   |    |

| Channel<br>selector: | VDD        | \$ |

| IN+ Channel 1:       | PIN 6      | \$ |

| IN+ Channel 2:       | None       | \$ |

| IN- Channel:         | None       | \$ |

| External output:     | Disable    | \$ |

Figure 18. PGA properties

| DCMP0/PWM0                       |            |    |  |  |  |  |

|----------------------------------|------------|----|--|--|--|--|

| DCMP/PWM<br>power register:      | Power on   |    |  |  |  |  |

| Function<br>selection:           |            |    |  |  |  |  |

| PD sync to<br>clock:             | Off        | •  |  |  |  |  |

| Clock source:                    | ADC CLK    | •  |  |  |  |  |

| Clock invert:                    | Disable    | •  |  |  |  |  |

| PWM & ADC<br>clock source :      | RC OSC     | •  |  |  |  |  |

| PWM data sync<br>with SPI clock: | Disable    | •  |  |  |  |  |

| Duty cycle:                      | 0% - 99.6% | \$ |  |  |  |  |

| PWM<br>deadband time:            | 10 ns      | •  |  |  |  |  |

| Register 0:<br>MTRX SEL: (0:0)   | 0          | *  |  |  |  |  |

| Register 1:<br>MTRX SEL: (0:1)   | 0          | *  |  |  |  |  |

| Register 2:<br>MTRX SEL: (1:0)   | 0          | *  |  |  |  |  |

| Register 3:<br>MTRX SEL: (1:1)   | 0          | *  |  |  |  |  |

| Con                              | nections   |    |  |  |  |  |

| IN+ selector:                    | ADC [7:0]  |    |  |  |  |  |

| IN- selector:                    | Register 0 | •  |  |  |  |  |

Figure 20. DCMP properties

### 6-Channel Power Lines Sequencer

| WS Ctrl/14-bit CNT0/DLY0                                                                                      |                                                                                                                 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Туре:                                                                                                         | CNT/DLY \$                                                                                                      |  |  |  |  |  |

| Mode:                                                                                                         | Delay 🔷                                                                                                         |  |  |  |  |  |

| Counter data:                                                                                                 | 30                                                                                                              |  |  |  |  |  |

| Delay time:                                                                                                   | (Range: 1 - 16383)<br>1.3000 ms <u>Formula</u>                                                                  |  |  |  |  |  |

| Edge select:                                                                                                  | Falling 🔷                                                                                                       |  |  |  |  |  |

| Q mode:                                                                                                       | Reset                                                                                                           |  |  |  |  |  |

| DFF bypass<br>enable:                                                                                         | None 🔷                                                                                                          |  |  |  |  |  |

| Connections                                                                                                   |                                                                                                                 |  |  |  |  |  |

| FSM data:                                                                                                     | None 🗘                                                                                                          |  |  |  |  |  |

| Clock:                                                                                                        | CLK 🔷                                                                                                           |  |  |  |  |  |

| Clock source:                                                                                                 | OSC Freq.                                                                                                       |  |  |  |  |  |

|                                                                                                               |                                                                                                                 |  |  |  |  |  |

| 4-bit LUT1/14                                                                                                 | -bit CNT2/DLY2/FSM0                                                                                             |  |  |  |  |  |

| 4-bit LUT1/14<br>Type:                                                                                        | -bit CNT2/DLY2/FSM0                                                                                             |  |  |  |  |  |

| 10.275                                                                                                        |                                                                                                                 |  |  |  |  |  |

| Түре:                                                                                                         | CNT/DLY<br>Delay<br>1                                                                                           |  |  |  |  |  |

| Type:<br>Mode:                                                                                                | CNT/DLY 🗘                                                                                                       |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:                                                                               | CNT/DLY       Delay       1       (Range: 1-16383)                                                              |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:<br>Delay time:                                                                | CNT/DLY       Delay       1       (Range: 1 - 16383)       0.1400 ms                                            |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:<br>Delay time:<br>Edge select:                                                | CNT/DLY<br>Delay<br>(Range: 1 - 16383)<br>0.1400 ms Formula<br>Rising<br>(Range )                               |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:<br>Delay time:<br>Edge select:<br>Q Mode:<br>FSM data sync<br>with SPI clock: | CNT/DLY<br>Delay<br>1<br>(Range: 1 - 16383)<br>0.1400 ms Formula<br>Rising<br>Reset<br>CNT/DLY                  |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:<br>Delay time:<br>Edge select:<br>Q Mode:<br>FSM data sync<br>with SPI clock: | CNT/DLY   Delay   1   (Range: 1 - 16383)   0.1400 ms   Formula   Rising   Reset   Disable                       |  |  |  |  |  |

| Type:<br>Mode:<br>Counter data:<br>Delay time:<br>Edge select:<br>Q Mode:<br>FSM data sync<br>with SPI clock: | CNT/DLY<br>Delay<br>Delay<br>(Range: 1 - 16383)<br>0.1400 ms Formula<br>Rising<br>Reset<br>Disable<br>mnections |  |  |  |  |  |

Figure 21. DLYs properties

| Гуре:    |          | l        | .UT      |      |     | \$    |

|----------|----------|----------|----------|------|-----|-------|

| IN3      | IN2      | IN1      | INO      |      | OUT | _     |

| 0        | 0        | 0        | 0        | 0    |     | \$    |

| 0        | 0        | 0        | 1        | 1    |     | \$    |

| 0        | 0        | 1        | 0        | 0    |     | \$    |

| 0        | 0        | 1        | 1        | 1    |     | \$    |

| 0        | 1        | 0        | 0        | 0    | 1   | \$    |

| 0        | 1        | 0        | 1        | 0    |     | ¢     |

| 0        | 1        | 1        | 0        | 1    |     | \$    |

| 0        | 1        | 1        | 1        | 1    |     | 4     |

| 1        | 0        | 0        | 0        | 0    |     | \$    |

| 1        | 0        | 0        | 1        | 0    |     | \$    |

| 1        | 0        | 1        | 0        | 0    | 1   | \$    |

| 1        | 0        | 1        | 1        | 0    |     | ¢     |

| 1        | 1        | 0        | 0        | 0    |     | \$    |

| 1        | 1        | 0        | 1        | 0    |     | \$    |

| 1        | 1        | 1        | 0        | 0    | 1   | \$    |

| 1        | 1        | 1        | 1        | 0    |     | \$    |

|          |          | 3-bit    | LUTO     |      |     |       |

| IN3      | IN2      | IN1      | INO      |      | OUT | _     |

| 0        | 0        | 0        | 0        | 1    |     | \$    |

| 0        | 0        | 0        | 1        | 0    |     | \$    |

| 0        | 0        | 1        | 0        | 0    |     | \$    |

| 0        | 0        | 1        | 1        | 0    |     | \$    |

| 0        | 1        | 0        | 0        | 0    |     | \$    |

| 0        | 1        | 0        | 1        | 0    |     | \$    |

| 0        | 1        | 1        | 0        | 0    |     | \$    |

| 0        | 1        | 1        | 1        | 0    |     | \$    |

| 1        | 0        | 0        | 0        | 0    |     | 4     |

|          | 3-bi     | t LUT6   | /Pipe    | Dela | iy  |       |

| ype:     |          | LUT      |          |      |     |       |

| 1512     | 0.02     | 1614     | 1810     |      | OUT |       |

| IN3<br>0 | 1N2<br>0 | IN1<br>0 | 1N0<br>0 | 1    | 001 |       |

| 0        | 0        |          | 1        | 1    |     | 41 41 |

| 0        |          | 0        | 0        | 0    |     |       |

|          | 0        |          |          | 0    |     | +     |

| 0        | 0        | 1        | 1        | 0    |     | 4     |

|          | 1        |          | 0        | 0    |     | +     |

| 0        | 1        | 0        | 1        | 0    |     | +     |

| 0        | 1        | 1        | 0        | 0    |     | +     |

| 0        | 1        | 1        | 1        | 1    |     | \$    |

An analog voltage comes from PIN6, configured as analog input, to the PGA and then - to ADC block, which converts it into 8-bit code. Then this code can be loaded into CNT2/DLY2/FSM0 block as counter data. So by the changing Pin6 analog input voltage, it is possible to change delay time between power lines switching. As in previous circuits, the generator operation time range is determined by LUT "Enable Control", but for generator reset (by P DLY in both edge detector mode) 3-bit LUT0 is used. CNT0/DLY0 block is needed to switch generator on after the ADC outputs its first proper parallel data. When the ADC input voltage is less that ADC offset (about 50mV), the ADC will output 8-bit logic 0, which will make the generator not operational. To remedy this situation, DCMP checks if ADC data is equal to 0. If it is, a 1-bit MUX with Enable (4-bit LUT0) will output its signal (after CNT0/DLY0 delay) from the OSC (minimum delay time). If it is not equal to 0 \_ then signaling is from CNT2/DLY2/FSM0 + 3-bit LUT0 generator.

Figure 23. Timing diagram of Power Lines Sequencer with variable delay CH1 – V-IN; D0 – Enable; D1 – Line1; D2 – Line2; D3 – Line3; D4 – Line4; D5 – Line5; D6 – Line6.

#### Conclusion

Using only one SLG46140 chip it is possible to create a power lines sequencer for six (or even more) lines with constant or variable delay between lines switching. Current consumption is also optimized (at 3.3V VDD): 150uA during lines switching on/off (dynamic), and 0uA when lines are are settled (static).

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.