## **Contents**

| Ι. | interi | nai wemory                        | 4  |

|----|--------|-----------------------------------|----|

|    | 1.1    | Block Diagram                     | 4  |

|    | 1.2    | Offset                            | 6  |

|    | 1.3    | Slope                             | 7  |

|    |        | 1.3.1. Slope of Transfer Function | 7  |

|    |        | 1.3.2. Slope example              | 7  |

|    | 1.4    | Clamping                          | 8  |

|    |        | 1.4.1. Clamping Example           | 9  |

|    | 1.5    | LinInt0                           | 10 |

|    |        | 1.5.1. Linear Error Correction    | 11 |

|    | 1.6    | LinInt1                           | 11 |

|    | 1.7    | LinInt2                           | 12 |

|    | 1.8    | LinInt3                           | 13 |

|    | 1.9    | LinInt4                           | 14 |

|    | 1.10   | Coil Offset                       | 15 |

|    | 1.11   | CalMode                           | 16 |

|    |        | 1.11.1. Output Mode               | 16 |

|    |        | 1.11.2. Correction Mode           | 18 |

|    | 1.12   | Output                            | 19 |

|    | 1.13   | Trimming                          | 21 |

|    | 1.14   | AGC0                              | 22 |

|    | 1.15   | AGC1                              | 23 |

|    | 1.16   | Mask                              | 24 |

|    | 1.17   | Traceability0                     | 25 |

|    | 1.18   | Traceability1                     | 26 |

|    | 1.19   | Misc                              | 26 |

|    | 1.20   | Afe_Agc                           | 26 |

|    | 1.21   | Xsine                             | 27 |

|    | 1.22   | Ycosine                           | 27 |

|    | 1.23   | Angle                             | 27 |

|    | 1.24   | Cordic Magnitude                  | 28 |

|    | 1.25   | SPA                               | 28 |

|    | 1.26   | Pos0                              | 29 |

|    | 1.27   | Pos1                              | 29 |

| 2. | Glos   | sary                              | 30 |

| 3. |        | sion History                      | 30 |

|    |        |                                   |    |

# **List of Figures**

| Figure 1. Internal Memory of the ZMID4200                         | 4  |

|-------------------------------------------------------------------|----|

| Figure 2. Internal Memory of the ZMID4200                         |    |

| Figure 3. Clamping Example                                        | 10 |

| Figure 4. Linear Error Correction Example                         | 11 |

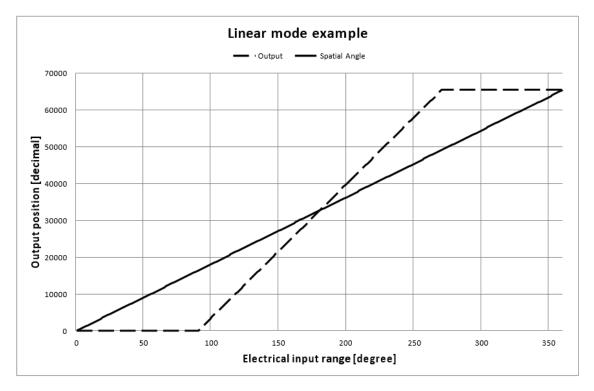

| Figure 5. Linear Output Mode Example with Slope = 2, Offset = 90° | 17 |

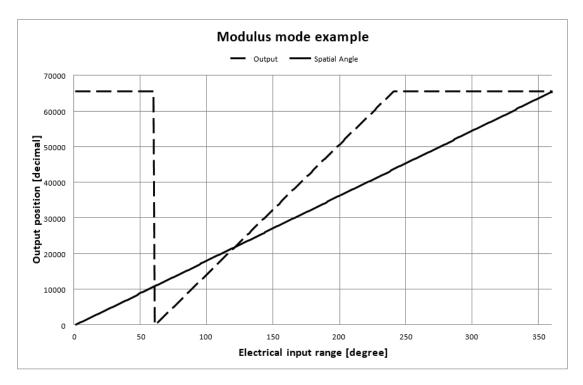

| Figure 6. Modulus Output Example with Slope = 2, Offset = 60°     | 17 |

| Figure 7. Pre-Calibration Process                                 | 18 |

| Figure 8. Post-Calibration Process                                | 18 |

| Figure 9. Output PWM Diagnostic Level                             | 20 |

| Figure 10. Output Analog Diagnostic Level                         | 21 |

| Figure 11. Gain Control                                           | 22 |

| List of Tables                                                    |    |

| Table 1. Internal Memory                                          |    |

| Table 2. Offset Register Description                              |    |

| Table 3. Offset Register Description Modulo 360                   |    |

| Table 4. Slope Register Description                               |    |

| Table 5. CLAMP Register Description                               |    |

| Table 6. LinInt0 Register Description                             |    |

| Table 7. LinInt1 Register Description                             |    |

| Table 8. LinInt2 Register Description                             |    |

| Table 9. LinInt3 Register Description                             |    |

| Table 10. LinInt4 Register Description                            |    |

| Table 11. Amplitude Offset Register Description                   |    |

| Table 12. CalMode Register Description                            |    |

| Table 13. Output Register Description                             |    |

| Table 14. Trim0 Register Description                              |    |

| Table 15. AGC0 Register Description                               |    |

| Table 16. AGC0 Register Description                               |    |

| Table 17. Mask Register Description                               |    |

| Table 18. Traceability0 Register Description                      |    |

| Table 19. Traceability1 Register Description                      |    |

| Table 20. Misc Register Description                               |    |

| Table 21. Afe_Agc Register Description                            |    |

| Table 22. Xsine Register Description                              |    |

| Table 23. Ycosine Register Description                            |    |

| Table 24. Angle Register Description                              |    |

| Table 25. Mag Register Description                                |    |

| Table 26. Spa Register Description                                |    |

| Table 27. Pos0 Register Description | 29 |

|-------------------------------------|----|

| Table 28. Pos1 Register Description | 29 |

## 1. Internal Memory

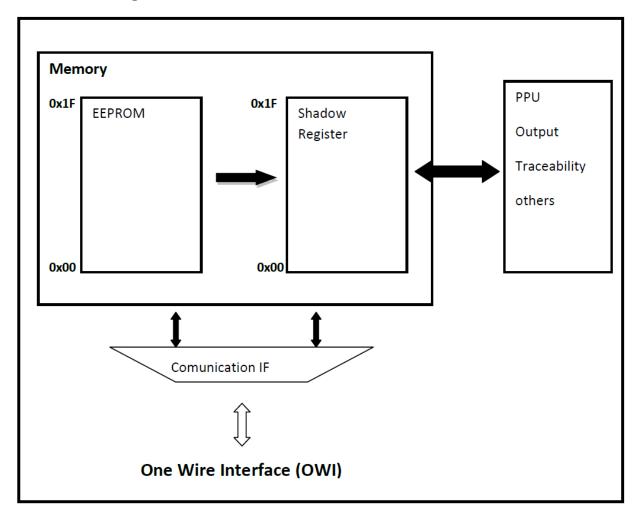

## 1.1 Block Diagram

Figure 1. Internal Memory of the ZMID4200

Figure 1 shows the internal memory topology of the ZMID4200 products which is split up into a non-volatile EEPROM (E2P) and a volatile shadow ram (SWR) section. After chip start up the E2P content is copied into the SWR. During IC operation in OWI mode, changes in the SWR will take immediate effect whereas changes in the E2P require an IC power cycle. (Power off/Power on).

### Definitions:

0b Binary number prefix.

0x Hexadecimal number prefix.

**Table 1. Internal Memory**

| Address | Name   | Туре | Location | Function                                        |  |

|---------|--------|------|----------|-------------------------------------------------|--|

| 0x00    | Offset | R/W  | E2P/SWR  | 14-bit zero- Zero Angle offset of output signal |  |

| 0x01    | Slope  | R/W  | E2P/ SWR | 13-bit slope value of output signal             |  |

| Address | Name                | Туре | Location | Function                                                                                                                                                                                                                                       |  |

|---------|---------------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x02    | Clamping            | R/W  | E2P/SWR  | Clamp values of output signal                                                                                                                                                                                                                  |  |

| 0x03    | LinInt0             | R/W  | E2P/SWR  | Linear interpolation of output signal corr1@12.5% (45°) - bit158 corr0@0%(0°) - bit70                                                                                                                                                          |  |

| 0x04    | LinInt1             | R/W  | E2P/SWR  | Linear interpolation of output signal corr3@37.5% (135°) - bit158 corr2@25%(90°) - bit70                                                                                                                                                       |  |

| 0x05    | LinInt2             | R/W  | E2P/SWR  | Linear interpolation of output signal corr5@62.5% (225°) - bit158 corr4@50%(180°) - bit70                                                                                                                                                      |  |

| 0x06    | LinInt3             | R/W  | E2P/SWR  | Linear interpolation of output signal corr7@87.5% (315°) - bit158 corr6@75%(270°) - bit70                                                                                                                                                      |  |

| 0x07    | LinInt4             | R/W  | E2P/SWR  | Linear interpolation of output signal not used - bit158 corr8@100%(360°) - bit70                                                                                                                                                               |  |

| 0x08    | Coil offset         | R/W  | E2P/SWR  | Signal Offset correction of the demodulated input signals - sin and cos (r1,r2 - Ycos,Xsin); Only apply if constant input gain setting is activated.                                                                                           |  |

| 0x09    | CalMode             | R/W  | E2P/SWR  | Calibration mode register contains control bits for output Mode like linear or modulo360 mode sensor; linear correction mode like pre-&post-calibration Angle offset for linearity correction like 0° or - 22.5°; Swap receiver coils polarity |  |

| 0x0A    | Output              | R/W  | E2P/SWR  | Output register is used for configuration of the output SENT CRC, SENT Pause, PWM slope current, PWM freq, Analog diagnostic level.                                                                                                            |  |

| 0x0B    | Trimming            | R/W  | E2P/SWR  | This register contains control parameters for: PWM slope time, OSR, LC oscillator current, VDDT voltage calibration                                                                                                                            |  |

| 0x0C    | AGC0                | R/W  | E2P/SWR  | Basic configurations of the analog front-end in terms of timing and gain e.g. Automated gain scheduling in number of samples; Integrator gain stage;                                                                                           |  |

| 0x0D    | AGC1                | R/W  | E2P/SWR  | Configurations of excitation coil frequency limits (alarm setting); CORDIC magnitude limits; Interlink mode (integration time adaption and gain adaption)                                                                                      |  |

| 0x0E    | Mask                | R/W  | E2P/SWR  | Diagnostic mask register is controlling which alarms are generating an output diagnostic flag e.g: Receiver coil1 open/short; Excitation coil break;                                                                                           |  |

| 0x0F    | Trace0              | R/W  | E2P      | factory traceability code 0                                                                                                                                                                                                                    |  |

| 0x10    | Trace1              | R/W  | E2P      | factory traceability code 1                                                                                                                                                                                                                    |  |

| 0x11    | Misc                | R/W  | E2P/SWR  | Configuration of voltage regulators and oscillators; e.g. switch off VDDT regulator in case of excitation coil alarm                                                                                                                           |  |

| 0x13    | Afe_agc             | R    | SWR      | Analog front-end/ Automatic gain regulation. Polarity of R1 & R2 ADC gain. AGC nr. of integration cycles                                                                                                                                       |  |

| 0x14    | Xsine               | R    | SWR      | 13-bit Cordic raw input signal                                                                                                                                                                                                                 |  |

| 0x15    | Ycosine             | R    | SWR      | 13-bit Cordic raw input signal                                                                                                                                                                                                                 |  |

| 0x16    | Angle               | R    | SWR      | 15-bit Cordic output angle (0° to 90°)                                                                                                                                                                                                         |  |

| 0x17    | Cordic<br>Magnitude | R    | SWR      | 15-bit Cordic output magnitude                                                                                                                                                                                                                 |  |

| 0x18    | Spa                 | R    | SWR      | Spatial angle 16-bit output angle (0° to 360°) before output calibration and linear error correction.                                                                                                                                          |  |

| 0x19    | Pos0                | R    | SWR      | Position0 16-bit output angle (0° to 360°) after output calibration; If linearization done before output calibration this value = Position1; If linearization done after output calibration this value ≠ Position1                             |  |

| 0x1A    | Pos1                | R    | SWR      | Position1 16-bit output angle (0° to 360°) after output calibration and linearization; This value is always affected by                                                                                                                        |  |

#### 1.2 Offset

Address of register: 0x00.

Default value: 0x0000.

The offset parameter is used for the calibration of the position transfer function. The notation of the offset parameter depends on the output mode (see 1.12). Two output modes can be selected (modulo360 or linear).

Output mode: Modulo360 (set out\_mod = 0b1 (1.10), for selecting the output mode "360Modulo")

**Table 2. Offset Register Description**

| Bits            | Symbol   |                                     | Description     |

|-----------------|----------|-------------------------------------|-----------------|

| Off.15 - Off.14 | Reserved | Not used, read as 0 (SWR).          |                 |

| Off.13 - Off.0  | Offset   | Offset of output transfer function. |                 |

|                 |          | Offset Value                        | Value in Degree |

|                 |          | 0x0000                              | 0               |

|                 |          | 0x0800                              | 45              |

|                 |          | 0x1000                              | 90              |

|                 |          | 0x1800                              | 135             |

|                 |          | 0x2000                              | 180             |

|                 |          | 0x2800                              | 225             |

|                 |          | 0x3000                              | 270             |

|                 |          | 0x3800                              | 315             |

|                 |          | 0x3FFF                              | 360             |

Note: The reserved bits off.15 & off.14 can be written and read to/from the block E2P. The copy process copies only bits (off.13 down to off.0) to the SWR.

Output mode: Linear (set out\_mod = 0b0 (see section 1.11.1), for selecting Linear Output mode).

**Table 3. Offset Register Description Modulo 360**

| Bits            | Symbol   |                                     | Description     |  |  |

|-----------------|----------|-------------------------------------|-----------------|--|--|

| Off.15 - Off.14 | Reserved | Not used, read as 0 (SWR).          |                 |  |  |

| Off.13 - Off.0  | Offset   | Offset of output transfer function. |                 |  |  |

|                 |          | Offset Value                        | Value in Degree |  |  |

|                 |          | 0x0000                              | 180             |  |  |

|                 |          | 0x0400                              | 360             |  |  |

|                 |          | 0x0800                              | 540             |  |  |

|                 |          | 0x0C00                              | 720             |  |  |

|                 |          | 0x1000                              | 900             |  |  |

|                 |          | 0x1400                              | 1080            |  |  |

|                 |          | 0x1800                              | 1260            |  |  |

|                 |          | 0x1C00                              | 1440            |  |  |

|                 |          | 0x1FFF                              | 1620            |  |  |

|                 |          | 0x2000                              | 180             |  |  |

|                 |          | 0x2400                              | 0               |  |  |

|                 |          | 0x2800                              | -180            |  |  |

|                 |          | 0x2C00                              | -360            |  |  |

|                 |          | 0x3000                              | -540            |  |  |

|                 |          | 0x3400                              | -720            |  |  |

|                 |          | 0x3800                              | -900            |  |  |

|                 |          | 0x3C00                              | -1080           |  |  |

|                 |          | 0x3FFF                              | -1260           |  |  |

Note: The reserved bits off.15 & off.14 can be written and read to/from the block E2P. The copy process copies only bits (off.13 down to off.0) to the SWR.

## 1.3 Slope

Address of register: 0x01.

Default value: 0x0400.

#### 1.3.1. Slope of Transfer Function

The slope parameter is used for the calibration of the position transfer function. It is a multiplication factor for the spatial angle. The slope notation is independent from the out\_mode parameter (see section 1.12).

**Table 4. Slope Register Description**

| Bits            | Symbol   |                                   | Description     |

|-----------------|----------|-----------------------------------|-----------------|

| slp.15 - slp.13 | Reserved | Not used, read as 0 (SWR)         |                 |

| slp.12 - slp.0  | Slope    | Slope of output transfer function | on.             |

|                 |          | Offset Value                      | Value in Degree |

|                 |          | 0x0000                            | 0.0             |

|                 |          | 0x0100                            | 0.25            |

|                 |          | 0x0200                            | 0.5             |

|                 |          | 0x0300                            | 0.75            |

|                 |          | 0x0400                            | 1.0             |

|                 |          | 0x0800                            | 2.0             |

|                 |          | 0x0C00                            | 3.0             |

|                 |          | 0x0FFF                            | 3.999           |

|                 |          | 0x1000                            | -0.0            |

|                 |          | 0x1100                            | -0.25           |

|                 |          | 0x1200                            | 0.5             |

|                 |          | 0x1300                            | 0.75            |

|                 |          | 0x1400                            | -1.0            |

|                 |          | 0x1800                            | -2.0            |

|                 |          | 0x1C00                            | -3.0            |

|                 |          | 0x1FFF                            | -3.999          |

Note: The reserved bits slp.15, slp.14 and slp.13 can be written and read to/from the block E2P.

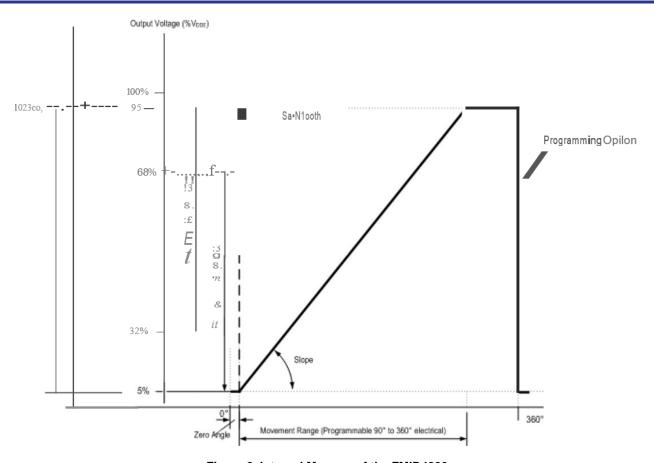

### 1.3.2. Slope example

Slope value coded on 13bits with a range between -4 to +4, 1 bit is the sign and defines the sign of (slope).

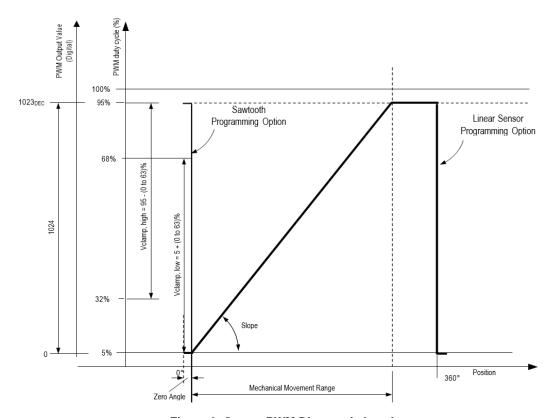

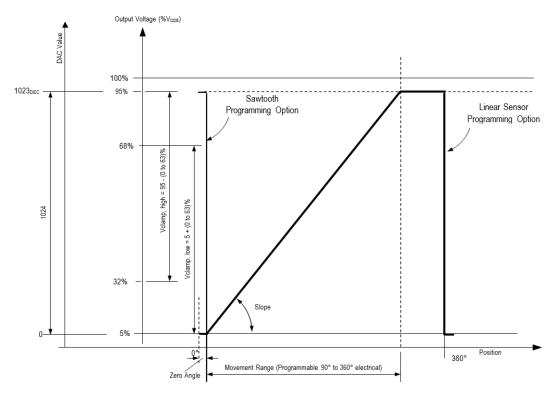

Figure 2. Internal Memory of the ZMID4200

Figure 2 shows the internal memory topology of the ZMID4200 products which is split up into a non-volatile EEPROM (E2P) and a volatile shadow ram (SWR) section. After chip start up the E2P content is copied into the SWR. During IC operation in OWI mode, changes in the SWR will take immediate effect whereas changes in the E2P require an IC power cycle. (Power off/Power on).

### 1.4 Clamping

Address of register: 0x02.

Default value: 0x0000.

The clamping parameters clamp\_low and clamp\_high are located in the clamp memory. These two parameters are used for position calibration if the output protocol mode is for ZMID4200. For the Analog output mode the complete 100% position range is mapped to a voltage range from 250mV to 4750mV. The stepping rate of the clamping parameters is 1%, so that the analog voltage stepping rate is 47.5 mV / 1 %. The diagnostic low level is less or equal 200mV, the high level is higher or equal 4800mV.

For the PWM output mode the position range is mapped to the Pulse Pause Ratio (PPR) of a periodic analog output signal. 100% position range is mapped to the PPR-range from 5% to 95%. So a clamping step of 1% is mapped to a PPR change of 0.9% (e.g. clamp\_low = 10% & pos <= clamp\_low --> PPR = 5% + 9%). The diagnostic low level is mapped to 2.5% PPR, the high level is mapped to 97.5% PPR.

**Table 5. CLAMP Register Description**

| Bits                 | Symbol     | Des                                                                       | cription                  |  |

|----------------------|------------|---------------------------------------------------------------------------|---------------------------|--|

| clamp. 15 -clamp. 14 | Reserved   | Not used, read as 0 (SWR)                                                 | Not used, read as 0 (SWR) |  |

| clamp. 13 - clamp. 8 | clamp_high | Position output clamp high descend from 4750 mV (Analog) resp. 95% (PWM). |                           |  |

|                      |            | clamp_high (CLAMP13 - CLAMP08)                                            | Rate (%)                  |  |

|                      |            | 0x00                                                                      | 0                         |  |

|                      |            | 0x01                                                                      | 1                         |  |

|                      |            | 0x02                                                                      | 2                         |  |

|                      |            |                                                                           |                           |  |

|                      |            | ••••                                                                      |                           |  |

|                      |            |                                                                           |                           |  |

|                      |            |                                                                           |                           |  |

|                      |            | 0x3F                                                                      | 63                        |  |

| clamp. 7 - clamp.6   | Reserved   | Not used, read as 0 (SWR)                                                 |                           |  |

| clamp. 5 - clamp. 0  | clamp_low  | Position output clamp low rising from 250mV (Analog) resp. 5% (PWM)       |                           |  |

|                      |            | clamp_low (CLAMP5 - CLAMP00)                                              | Rate (%)                  |  |

|                      |            | 0x00                                                                      | 0                         |  |

|                      |            | 0x01                                                                      | 1                         |  |

|                      |            | 0x02                                                                      | 2                         |  |

|                      |            |                                                                           |                           |  |

|                      |            |                                                                           |                           |  |

|                      |            |                                                                           |                           |  |

|                      |            |                                                                           |                           |  |

|                      | <u> </u>   | 0x3F                                                                      | 63                        |  |

Note: The reserved bits clamp.15, clamp.14, clamp.7 and clamp.6 can be written and read to/from the block E2P. The copy process copies only bits (clamp.13 down to clamp.8) and (clamp.5 down to clamp.0) to the SWR.

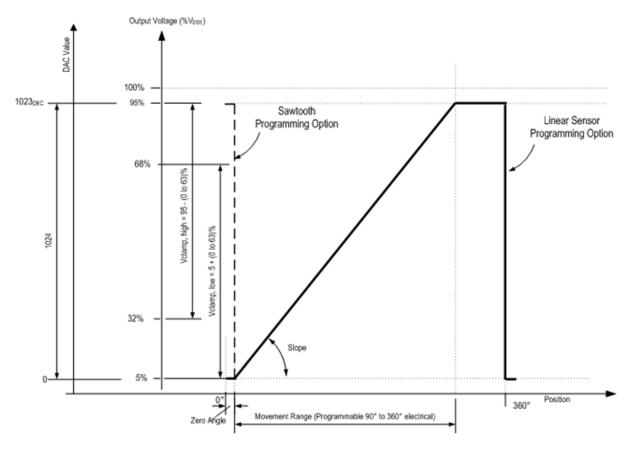

### 1.4.1. Clamping Example

Clamps (applicable for Analog and PWM Output, not for SENT).

Clamp\_low (6 bits): min value is 5%, steps of 1% from minimum value. Max Clamp\_low value is: 68%.

Clamp\_high (6 bits): max value is 95%, steps of -1% from max value. Min Clamp\_high value is: 32%.

In the below example the clamping levels are 5% and 95%.

Figure 3. Clamping Example

## 1.5 LinInt0

Address of register: 0x03.

Default value: 0x0000.

Table 6. LinInt0 Register Description

| Bits                   | Symbol |                                            | Description       |

|------------------------|--------|--------------------------------------------|-------------------|

| linint0.15 - linint0.8 | corr1  | Correction factor 1 for position 12.5% (45 | deg).             |

|                        |        | Corr0 (linint7 - linint0)                  | Correction Factor |

|                        |        | 0x00                                       | 0                 |

|                        |        | 0x01                                       | 1                 |

|                        |        |                                            |                   |

|                        |        |                                            |                   |

|                        |        |                                            |                   |

|                        |        | 0x7F                                       | 127               |

|                        |        | 0x10                                       | -0                |

|                        |        | 0x11                                       | -1                |

|                        |        |                                            |                   |

|                        |        |                                            |                   |

|                        |        |                                            |                   |

|                        |        | 0xFF                                       | -127              |

| Bits                 | Symbol |                                             | Description       |

|----------------------|--------|---------------------------------------------|-------------------|

| Linint0.7 -linint0.0 | corr0  | Correction factor 0 for position 0% ( 0 deg | )                 |

|                      |        | Corr0 (linint7 - linint0)                   | Correction Factor |

|                      |        | 0x00                                        | 0                 |

|                      |        | 0x01                                        | 1                 |

|                      |        |                                             |                   |

|                      |        |                                             |                   |

|                      |        |                                             |                   |

|                      |        | 0x7F                                        | 127               |

|                      |        | 0x10                                        | -0                |

|                      |        | 0x11                                        | -1                |

|                      |        |                                             |                   |

|                      |        |                                             |                   |

|                      |        |                                             |                   |

|                      |        | 0xFF                                        | -127              |

Note: The notation of the correction factor is sign & abs. with a range of +127...+-0....-127.

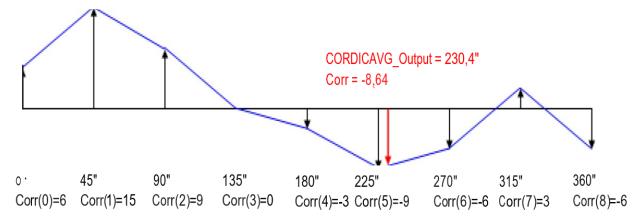

#### 1.5.1. Linear Error Correction

The linear error correction function has 9 equidistant fixed correction points (one dimensional). Between each pair of grid points a linear interpolation function evaluates the correction factor.

**Figure 4. Linear Error Correction Example**

#### 1.6 LinInt1

Address of register: 0x04.

Default value: 0x0000.

Table 7. LinInt1 Register Description

| Bits                   | Symbol | Description                                    |                   |

|------------------------|--------|------------------------------------------------|-------------------|

| Linint1.15 - linint1.8 | Corr3  | Correction factor 3 for position 37.5% (135 de | eg).              |

|                        |        | Corr3 (linint15 - linint8)                     | Correction Factor |

|                        |        | 0x00                                           | 0                 |

|                        |        | 0x01                                           | 1                 |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        | 0x7F                                           | 127               |

|                        |        | 0x10                                           | -0                |

|                        |        | 0x11                                           | -1                |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        | 0xFF                                           | -127              |

| Linint1.7 - linint1.0  | Corr2  | Correction factor 2 for position 25% (90 deg). |                   |

|                        |        | Corr2 (linint7 - linint0)                      | Correction Factor |

|                        |        | 0x00                                           | 0                 |

|                        |        | 0x01                                           | 1                 |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        | 0x7F                                           | 127               |

|                        |        | 0x10                                           | -0                |

|                        |        | 0x11                                           | -1                |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        |                                                |                   |

|                        |        | 0xFF                                           | -127              |

Note: The notation of the correction factor is sign & abs. with a range of +127...+- 0.....-127.

### 1.7 LinInt2

Address of register: 0x05.

Default value: 0x0000.

**Table 8. LinInt2 Register Description**

| Bits                   | Symbol | Description                                      |                   |  |  |  |

|------------------------|--------|--------------------------------------------------|-------------------|--|--|--|

| Linint2.15 - linint2.8 | Corr5  | Correction factor 5 for position 62.5% (225 deg) |                   |  |  |  |

|                        |        | Corr5 (linint15 - linint8)                       | Correction Factor |  |  |  |

|                        |        | 0x00                                             | 0                 |  |  |  |

|                        |        | 0x01                                             | 1                 |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0x7F                                             | 127               |  |  |  |

|                        |        | 0x10                                             | -0                |  |  |  |

|                        |        | 0x11                                             |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0xFF                                             | -127              |  |  |  |

| Linint2.7 - linint2.0  | Corr4  | Correction factor 4 for position 50% (180 deg).  |                   |  |  |  |

|                        |        | Corr4 (linint7 - linint0)                        | Correction Factor |  |  |  |

|                        |        | 0x00                                             | 0                 |  |  |  |

|                        |        | 0x01                                             | 1                 |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0x7F                                             | 127               |  |  |  |

|                        |        | 0x10                                             | -0                |  |  |  |

|                        |        | 0x11                                             |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0xFF                                             | -127              |  |  |  |

Note: The notation of the correction factor is sign & abs. with a range of +127 ... +- 0.....-127.

### 1.8 LinInt3

Address of register: 0x06.

Default value: 0x0000.

**Table 9. LinInt3 Register Description**

| Bits                   | Symbol | Description                                      |                   |  |  |  |

|------------------------|--------|--------------------------------------------------|-------------------|--|--|--|

| Linint3.15 - linint3.8 | Corr7  | Correction factor 7 for position 87.5% (315deg). |                   |  |  |  |

|                        |        | Corr7 (linint3.15 - linint3.8)                   | Correction Factor |  |  |  |

|                        |        | 0x00                                             | 0                 |  |  |  |

|                        |        | 0x01                                             | 1                 |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0x7F                                             | 127               |  |  |  |

|                        |        | 0x10                                             | -0                |  |  |  |

|                        |        | 0x11                                             | -1                |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0xFF                                             | -127              |  |  |  |

| Linint3.7 - linint3.0  | Corr6  | Correction factor 6 for position 75% (270deg).   |                   |  |  |  |

|                        |        | Corr6 (linint3.7 - linint3.0)                    | Correction Factor |  |  |  |

|                        |        | 0x00                                             | 0                 |  |  |  |

|                        |        | 0x01                                             | 1                 |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0x7F                                             | 127               |  |  |  |

|                        |        | 0x10                                             | -0                |  |  |  |

|                        |        | 0x11                                             | -1                |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        |                                                  |                   |  |  |  |

|                        |        | 0xFF                                             | -127              |  |  |  |

Note: The notation of the correction factor is sign & abs. with a range of +127 ... +- 0..... -127.

### 1.9 LinInt4

Address of register: 0x07.

Default value: 0x0000.

**Table 10. LinInt4 Register Description**

| Bits                   | Symbol   | Description               |  |

|------------------------|----------|---------------------------|--|

| Linint4.15 - linint4.8 | Reserved | Not used, read as 0 (SWR) |  |

| Bits                  | Symbol | Description                                    |                   |  |  |

|-----------------------|--------|------------------------------------------------|-------------------|--|--|

| Linint4.7 - linint4.0 | Corr8  | Correction factor 8 for position 100% (360deg) |                   |  |  |

|                       |        | Corr8 (linint4.15 - linint4.8)                 | Correction Factor |  |  |

|                       |        | 0x00                                           | 0                 |  |  |

|                       |        | 0x01                                           | 1                 |  |  |

|                       |        |                                                |                   |  |  |

|                       |        |                                                |                   |  |  |

|                       |        |                                                |                   |  |  |

|                       |        | 0x7F                                           | 127               |  |  |

|                       |        | 0x10                                           | -0                |  |  |

|                       |        | 0x11                                           | -1                |  |  |

|                       |        |                                                |                   |  |  |

|                       |        |                                                |                   |  |  |

|                       |        |                                                |                   |  |  |

|                       |        | 0xFF                                           | -127              |  |  |

Note: The notation of the correction factor is sign & abs. with a range of +127 ...+-0.....-127.

## 1.10 Coil Offset

Address of register: 0x08.

Default value: 0x0000.

The defined register offset values are added/ subtracted to/from the amplitude values (13-bit) of the receiver coil R2 and coil R1 values. When using the signal offset compensation the automated gain control (AGC1) must be switched off. (agc\_mode = 0b00 => Automatic gain OFF, integration time adaption OFF).

**Table 11. Amplitude Offset Register Description**

| Bits           | Symbol    | Description               |           |                            |                             |  |

|----------------|-----------|---------------------------|-----------|----------------------------|-----------------------------|--|

| amp.15         | mult_r1   | Multiplication factor for | r amplitu | ude offset_r1              |                             |  |

|                |           | mult_r1 (amp.1            | 15)       | 5) Multiplication Factor   |                             |  |

|                |           | 0b0                       |           | 2                          |                             |  |

|                |           | 0b1                       |           | 4                          |                             |  |

| amp.14 - amp.8 | offset_r1 | Offset value which is     | added/si  | ubtracted to/from receiver | coil R1 amplitude           |  |

|                |           | mult_r1                   |           | offset_r1                  | Correction Factor (Decimal) |  |

|                |           | 0b0                       | 0b0       | 111111                     | Ycosine + 126               |  |

|                |           |                           | 0b0       | 000000                     | Ycosine + 0                 |  |

|                |           |                           | 0b1       | 000000                     | Ycosine - 0                 |  |

|                |           |                           | 0b1       | 111111                     | Ycosine - 126               |  |

|                |           | 0b1                       | 0b0       | 111111                     | Ycosine + 252               |  |

|                |           |                           | 0b0       | 000000                     | Ycosine + 0                 |  |

|                |           |                           | 0b1       | 000000                     | Ycosine - 0                 |  |

|                |           |                           | 0b1       | 111111                     | Ycosine - 252               |  |

| amp.7          | mult_r2   | Multiplication factor fo  | r offset_ | r2                         |                             |  |

|                |           | mult_r2 (amp.7)           |           | Multiplication Factor      |                             |  |

|                |           | 0b0                       |           | 2                          |                             |  |

|                |           | 0b1                       |           | 4                          |                             |  |

| amp.6 - amp.0  | offset_r2 | Offset value which is     | added/si  | ubtracted to/from receiver | coil R2 amplitude.          |  |

|                |           | mult_r2                   |           | offset_r2                  | Correction Factor (Decimal) |  |

|                |           | 0b0                       | 0b0       | 111111                     | Xsine + 126                 |  |

|                |           |                           | 0b0       | 000000                     | Xsine + 0                   |  |

|                |           |                           | 0b1       | 000000                     | Xsine - 0                   |  |

|                |           |                           | 0b1       | 111111                     | Xsine - 126                 |  |

|                |           | 0b1                       | 0b0       | 111111                     | Xsine + 252                 |  |

|                |           |                           | 0b0       | 000000                     | Xsine + 0                   |  |

|                |           |                           | 0b1       | 000000                     | Xsine - 0                   |  |

|                |           |                           | 0b1       | 111111                     | Xsine - 252                 |  |

Note: abs (Xsine + offset r2) exceeds max.value of 0x1FFF → amplitude DSP overflow alarm is asserted.

### 1.11 CalMode

Address of register: 0x09.

Default value: 0x0000.

The calibration mode register contains some control bits which configure the calibration mode and evaluation of the correction curve.

**Table 12. CalMode Register Description**

| Bits                  | Symbol       | Description                   |                                                                                                         |  |

|-----------------------|--------------|-------------------------------|---------------------------------------------------------------------------------------------------------|--|

| calmod.15 - calmod.13 | Reserved     | Not used, read as 0 (SWR)     |                                                                                                         |  |

| calmod.12             | out_mod      | Output Mode                   |                                                                                                         |  |

|                       |              | Out_mod                       | Output Mode                                                                                             |  |

|                       |              | 0b0                           | Linear                                                                                                  |  |

|                       |              | 0b1                           | Modulo360                                                                                               |  |

| calmod.11 - calmod.9  | Reserved     | Not used, read as 0 (SWR)     |                                                                                                         |  |

| calmod.8              | corr_mod     | Correction Mode.              |                                                                                                         |  |

|                       |              | Defines how the correction cu | urve has to be applied to correct the linearity of the output transfer                                  |  |

|                       |              | function.                     | ,                                                                                                       |  |

|                       |              | Corr_mod                      | Correction Mode                                                                                         |  |

|                       |              | 0b0                           | Linear error correction pre-calibration                                                                 |  |

|                       |              | 0b1                           | Linear error correction post-calibration                                                                |  |

| calmod.7 - calmod.5   | Reserved     | Not used, read as 0 (SWR)     |                                                                                                         |  |

| calmod.4              | angle_offset | Linearization angle offset.   |                                                                                                         |  |

|                       |              |                               | offset is added to the CORDIC calculation only in the case of an e the Slope calibration (Corr_MOD) = 0 |  |

|                       |              | Angle_offset                  | Angle Offset in Degree                                                                                  |  |

|                       |              | 0b0                           | 0                                                                                                       |  |

|                       |              | 0b1                           | -22.5                                                                                                   |  |

| calmod.3              | swap_rc_pol  | Testing bits for Renesas      |                                                                                                         |  |

| calmod.2              | swap_rc_amp  | Testing bits for Renesas      |                                                                                                         |  |

| calmod.1              | invppr2      | Testing bits for Renesas      |                                                                                                         |  |

| calmod.0              | invppr1      | Testing bits for Renesas      |                                                                                                         |  |

### 1.11.1. Output Mode

Linear (Out\_Mod = 0): Linear Output Mode is a non-repeating output mode in which the sensor output signal is clamped at the mechanical end points with a range of  $-1260^{\circ}$  ... +  $1620^{\circ}$ .

Modulo 360 (Out\_Mod = 1): The Modulo 360 Output (Sawtooth Output) Mode is a repeating output mode in which the sensor output signal is not clamped at the mechanical end points, but is switched back to its origin with a range between 0° to 360°.

Figure 5. Linear Output Mode Example with Slope = 2, Offset = 90°

Figure 6. Modulus Output Example with Slope = 2, Offset = 60°

#### 1.11.2. Correction Mode

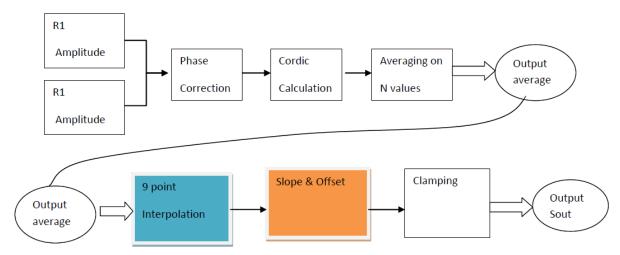

Pre Calibration: if (Corr\_MOD) = 0 then linearity correction is done before "Slope & Offset".

The pre-calibration should be used if the electric input covers a range of a 360°. Using pre-calibration is an advantaged when slope and offset needs to be changed after linearization.

Figure 7. Pre-Calibration Process

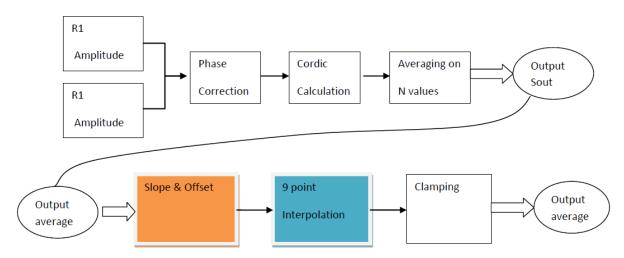

Post Calibration; if (Corr\_MOD) = 1 then linearity correction is done after "Slope & Offset ". The post-calibration should be the default standard type of calibration.

Figure 8. Post-Calibration Process

Note: The reserved bits can be written and read to/from the block E2P. The copy process copies only bits (calmod.12, calmod.8, calmod.4, calout1 and calmod.0) to the SWR.

Note: Individual swapping of receiver polarity & amplitude is only for testing purpose. For application mode both control bits have to be set 0b1 respectively 0b0.

## 1.12 Output

Address of register: 0x0A Default value: 0x0802

The output register configuration.

**Table 13. Output Register Description**

| Bits                 | Symbol         | Description                                                                   |                                                                                             |  |  |

|----------------------|----------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| out.15               | Reserved       | Not used, read as 0 (SWR)                                                     |                                                                                             |  |  |

| output.14            | sent_crc       | Only for SENT ou                                                              | atput                                                                                       |  |  |

|                      |                | SENT CRC                                                                      |                                                                                             |  |  |

|                      |                |                                                                               | bit switched between CRC calculation according Legacy implementation of SAE J               |  |  |

|                      |                | 2716.                                                                         |                                                                                             |  |  |

|                      |                | SENT CRC                                                                      | CRC Calculation                                                                             |  |  |

|                      |                | 0b0                                                                           | CRC calculation according rev. Feb 2008                                                     |  |  |

|                      |                | 0b1                                                                           | CRC calculation according SAE J 2716, Rev 3                                                 |  |  |

| output.13            | sent_pause     | Only for SENT ou                                                              | ıtput                                                                                       |  |  |

|                      |                | SENT Pause                                                                    |                                                                                             |  |  |

|                      |                | •                                                                             | it switches between a constant SENT frame length according SAE J 2716 rev3 by               |  |  |

|                      |                |                                                                               | pulse and a variable SENR frame length according rev2.                                      |  |  |

|                      |                | Sent_pause                                                                    | Frame Length                                                                                |  |  |

|                      |                | 0b0                                                                           | SENT frame according to SAE J 2716 Rev.2                                                    |  |  |

|                      |                | 0b1                                                                           | SENT frame length according SAE J 2716, Rev3.                                               |  |  |

| output.12            | sent_ssn       | Only for SENT ou                                                              | ·                                                                                           |  |  |

|                      |                |                                                                               | ad is transferred by the 3 data nibbles of signal1. The payload structure of signal2        |  |  |

|                      |                |                                                                               | ENT single secure nibble bit.                                                               |  |  |

|                      |                | SENT SSN                                                                      | Frame Length                                                                                |  |  |

|                      |                | 0b0                                                                           | nibble #4, #5, #6 set to zero                                                               |  |  |

|                      |                | 0b1                                                                           | nibble #4 & nibble #5 = value of 8-bit                                                      |  |  |

|                      |                |                                                                               | rolling counter with rollover back to zero.nibble #6 = inverted copy of nibble #1.          |  |  |

| output.11 - output.8 | pwm_slope_curr | Only for PWM ou                                                               |                                                                                             |  |  |

|                      |                | PWM slope curre                                                               |                                                                                             |  |  |

|                      |                |                                                                               | e PWM output signal is controlled by several current sources related to a master current    |  |  |

|                      |                |                                                                               | ent of the master source can be programmed.                                                 |  |  |

|                      |                | Pwm_slope_cu                                                                  | Irr PWM Slope Current Minimum                                                               |  |  |

|                      |                | 0x0<br>0xF                                                                    |                                                                                             |  |  |

|                      | ,              |                                                                               | Maximum                                                                                     |  |  |

| output.6 - output.4  | pwm_freq       | Only for PWM ou                                                               |                                                                                             |  |  |

|                      |                | Pwm_freq                                                                      | PWM Frequency (Hz)                                                                          |  |  |

|                      |                | 0b000                                                                         | 2023                                                                                        |  |  |

|                      |                | 0b001                                                                         | 1517                                                                                        |  |  |

|                      |                | 0b010                                                                         | 1214                                                                                        |  |  |

|                      |                | 0b011                                                                         | 1011                                                                                        |  |  |

|                      |                | 0b100                                                                         | 758                                                                                         |  |  |

|                      |                | 0b101                                                                         | 506                                                                                         |  |  |

|                      |                | 0b110                                                                         | 253                                                                                         |  |  |

|                      |                | 0b111                                                                         |                                                                                             |  |  |

| output.3             | pwm_diag       | Only for PWM ou                                                               | •                                                                                           |  |  |

|                      |                | PWM diagnostic I                                                              |                                                                                             |  |  |

|                      |                |                                                                               | col PWM allows two PPR for the diagnostic flag: diagnostic low & diagnostic high. Bit       |  |  |

| output 0             | one die -      | -                                                                             | select one of the two levels if diagnostic alarm is asserted.                               |  |  |

| output.2             | ana_diag       | Only for Analog o                                                             | ·                                                                                           |  |  |

|                      |                | ANALOG diagnos                                                                |                                                                                             |  |  |

|                      |                | The output protocol ANALOG allows two voltage ranges for the diagnostic flag: |                                                                                             |  |  |

|                      |                | J                                                                             | diagnostic high. bit output.6 allows to select one of the two levels if diagnostic alarm is |  |  |

|                      |                | asserted.                                                                     |                                                                                             |  |  |

| Bits               | Symbol  | Description                                                                                            |                                      |  |

|--------------------|---------|--------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| output.1- output.0 | out_pro | Output interface: These bits are used to configure the output interface. The default output is analog. |                                      |  |

|                    |         | out_pro                                                                                                | out_pro Outputs                      |  |

|                    |         | 0b00                                                                                                   | OWI                                  |  |

|                    |         | 0b01                                                                                                   | PWM                                  |  |

|                    |         | 0b10                                                                                                   | 0b10 Analog output voltage (default) |  |

|                    |         | 0b11                                                                                                   | SENT                                 |  |

Figure 9. Output PWM Diagnostic Level

Figure 10. Output Analog Diagnostic Level

Note: The reserved bits can be written and read to/from the block E2P. The copy process copies only defined bits to the SWR.

Note: PWM & SENT timing parameters are based on the ZMID4200 internal oscillator period. To fulfill the electrical specification the oscillator has to be calibrated to 16MHz (see 1.14).

## 1.13 Trimming

Address of register: 0x0B Default value: 0x8107

Trimming and OSR

The Trimming parameters controls the lc current and the vddt voltage regulator. The OSR parameter defines the decimation of ADC samples for calculating the position processing update rate.

Table 14. Trim0 Register Description

| Bits                | Symbol         |                                     | Description                                                                                                                                      |  |  |

|---------------------|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| trim0.15 - trim0.14 | pwm_slope_time | PWM slope time                      | PWM slope time                                                                                                                                   |  |  |

|                     |                | sources are switche                 | PWM output signal is controlled by current sources. The current ed on in 5 consecutive steps. The time between the steps isslope_time parameter. |  |  |

|                     |                | pwm_slope_time=                     | 0b00. 435ns / step pwm_slope_time= 0b01.580ns / step                                                                                             |  |  |

| trim0.13 - tirm0.12 | osr            | Oversampling Rate                   |                                                                                                                                                  |  |  |

|                     |                | The oversampling raccumulated and u | ate defines the number of samples per receive channel which are sed for the PPU.                                                                 |  |  |

|                     |                | OSR                                 | Samples/Channel                                                                                                                                  |  |  |

|                     |                | 0b00                                | 4                                                                                                                                                |  |  |

|                     |                | 0b01                                | 8                                                                                                                                                |  |  |

|                     |                | 0b10                                | 16                                                                                                                                               |  |  |

|                     |                | 0b11                                | 32                                                                                                                                               |  |  |

| trim0.11 - trim0.9  | Reserved       | Not used, read as 0                 | (SWR)                                                                                                                                            |  |  |

July 21, 2021

| Bits              | Symbol    |                       | Description                            |  |  |

|-------------------|-----------|-----------------------|----------------------------------------|--|--|

| trim0.8 - trim0.4 | lc_cal    | LC Oscillator Calibra | ation (excitation coil)                |  |  |

|                   |           | lc_cal                | Current (Excitation Coil)              |  |  |

|                   |           | 0b0.0000              | Min (0 mA)                             |  |  |

|                   |           | 0b1.1111              | Max (15 mA)                            |  |  |

| trim0.3           | Reserved  | Not used, read as 0   | (SWR)                                  |  |  |

| trim0.2 - trim0.0 | vddt_trim | Renesas internal par  | Renesas internal parameter for testing |  |  |

#### 1.14 AGC0

Address of register: 0x0C Default value: 0x0836

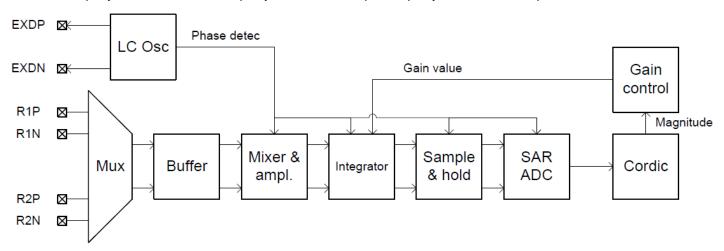

Basic configurations of the analog front end (R1/2 input receive path) gain regulation are controlled by the AGC register. The incoming time division multiplexed signals are amplified by the integrator and the S&H circuit (Figure 6). Both parameters 'ext' and 'gain' will modify the amplification factor of the sampled signals.

The parameter 'smpl\_cycle' is a 'timing-factor' in number of sample periods for the adaptive gain regulation to determine the point time for gain / integration time setting. A change of the smpl\_cycle parameter should only be done in dependency of the OSR parameter.

Parameter smp\_cycle zero indexed: smpl\_cycle = 0 .1st sample. smpl\_cycle = 1 .2nd sample.

Figure 11. Gain Control

Table 15. AGC0 Register Description

| Bits             | Symbol     |                      | Description                                                                                                                                  |             |                                      |  |

|------------------|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------|--|

| agc0.15          | Reserved   | Not used, re         | Not used, read as 0 (SWR)                                                                                                                    |             |                                      |  |

| agc0.14 - agc0.9 | smpl_cycle | ,                    | Only when OSR is changed to a non-default value (4) and the AGC control is turned on the sample cycle value needs to be adapted accordingly: |             |                                      |  |

|                  |            | OSR                  | Samples/Channel                                                                                                                              | 2 × Channel | Recommended<br>smpl_cycle<br>Setting |  |

|                  |            | 0b00 4 8 0b00.0100   |                                                                                                                                              |             | 0b00.0100                            |  |

|                  |            | 0b01                 | 8                                                                                                                                            | 16          | 0b00.1100                            |  |

|                  |            | 0b10                 | 16                                                                                                                                           | 32          | 0b01.1100                            |  |

|                  |            | 0b11 32 64 0b11.1100 |                                                                                                                                              |             | 0b11.1100                            |  |

| agc0.8 -agc0.4   | ext        | Renesas int          | ternal                                                                                                                                       |             | <u>.</u>                             |  |

| Bits            | Symbol     | Description                |        |                                                                                                                                                                                                                                                                 |

|-----------------|------------|----------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| agc0.3 - agc0.0 | gain_stage | Integrator gain stage      |        |                                                                                                                                                                                                                                                                 |

|                 |            | Gain_stage                 |        | Integrator Gain Stage                                                                                                                                                                                                                                           |

|                 |            | 0x0 Minim                  |        | num gain                                                                                                                                                                                                                                                        |

|                 |            |                            |        |                                                                                                                                                                                                                                                                 |

|                 |            |                            |        |                                                                                                                                                                                                                                                                 |

|                 |            | 0xC                        | Maxir  | num gain                                                                                                                                                                                                                                                        |