16

# R9A02G015

## User's Manual: Hardware

## ASSP (USB Power Delivery Controller)

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

Rev.1.00 Mar 2019

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power is supplied until the power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## How to Use This Manual

ReadersThis manual is intended for user engineers who wish to understand the functions of the<br/>R9A02G015 and design and develop application systems and programs for these devices.<br/>The target products are as follows.

• 32-pin: R9A02G0150/R9A02G0151

Purpose

This manual is intended to give users an understanding of the functions described in the

Organization below.

OrganizationThe R9A02G015 manual is separated into three parts: this manual, Data Sheet, and the<br/>software edition (common to the RL78 family).

#### R9A02G015 User's Manual: Hardware (This Manual)

Pin functions

Internal block functions

Interrupts

· Other on-chip peripheral functions

#### RL78 Family User's Manual: Software

- CPU functions

- Instruction set

- Explanation of each instruction

R9A02G015 Data Sheet

- Electrical specifications

- Package drawings

How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical engineering, logic circuits, and microcontrollers.

- To gain a general understanding of functions:

- $\rightarrow$  Read this manual in the order of the **CONTENTS**.

- How to interpret the register format:

- → For a bit number enclosed in angle brackets, the bit name is defined as a reserved word in the assembler, and is defined as an sfr variable using the #pragma sfr directive in the compiler.

- To know details of the R9A02G015 (built in RL78 CPU core) instructions:

- → Refer to the separate document RL78 Family User's Manual Software (R01US0015E).

| Conventions | Data significance:          | Higher digits on the left and lower digits on the right                        |

|-------------|-----------------------------|--------------------------------------------------------------------------------|

|             | Active low representations: | $\overline{\times \times \times}$ (overscore over pin and signal name) or xxxB |

|             | Note:                       | Footnote for item marked with Note in the text                                 |

|             | Caution:                    | Information requiring particular attention                                     |

|             | Remark:                     | Supplementary information                                                      |

|             | Numerical representations:  | Binary×××× or ××××B                                                            |

|             |                             | Decimal××××                                                                    |

|             |                             | Hexadecimal××××H                                                               |

|             |                             |                                                                                |

Related Documents

The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                       | Document No. |

|-------------------------------------|--------------|

| R9A02G015 User's Manual: Hardware   | This manual  |

| R9A02G015 Data Sheet                | R19DS0101E   |

| RL78 Family User's Manual: Software | R01US0015E   |

#### Documents Related to Flash Memory Programming (User's Manual)

| Document Name                                                            | Document No. |

|--------------------------------------------------------------------------|--------------|

| PG-FP6 Flash Memory Programmer User's Manual                             | R20UT4025E   |

| E1 Emulator R0E000010KCE00 E20 Emulator R0E000200KCT00 User's Manual     | R20UT0398E   |

| E2 Emulator RTE0T00020KCE00000R User's Manual                            | R20UT3538E   |

| E2 Emulator Lite RTE0T0002LKCE00000R User's Manual                       | R20UT3240E   |

| Renesas Flash Programmer Flash Memory Programming Software User's Manual | R20UT4066E   |

| Renesas Flash Development Toolkit User's Manual                          | R20UT0508E   |

## Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

#### **Other Documents**

| Document Name                        | Document No. |

|--------------------------------------|--------------|

| Renesas Microcontrollers RL78 Family | R01CP0003E   |

| Semiconductor Package Mount Manual   | R50ZZ0003E   |

| Semiconductor Reliability Handbook   | R51ZZ0001E   |

## Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

All trademarks and registered trademarks are the property of their respective owners.

EEPROM is a trademark of Renesas Electronics Corporation.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

## CONTENTS

| 1. OL  | ITLINE                                                                           | 17 |

|--------|----------------------------------------------------------------------------------|----|

| 1.1    | Features                                                                         | 17 |

| 1.2    | Ordering Information                                                             | 19 |

| 1.3    | Pin Configuration (Top View)                                                     | 20 |

| 1.3.1  | 32-pin product (with USB)                                                        | 20 |

| 1.3.2  | 32-pin product (without USB)                                                     | 21 |

| 1.4    | Pin Identification                                                               | 22 |

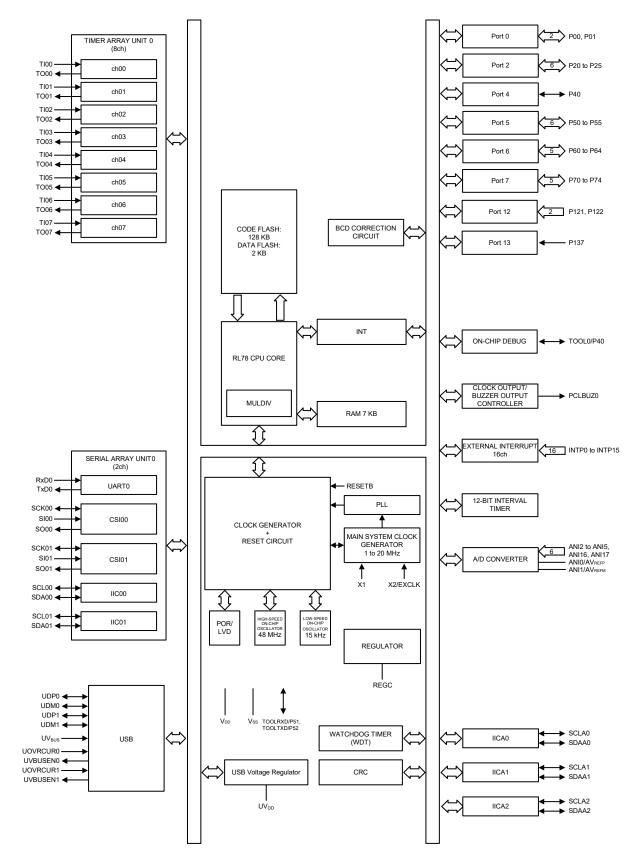

| 1.5    | Block Diagram                                                                    | 23 |

| 1.5.1  | 32-pin products                                                                  | 23 |

| 1.6    | Outline of Functions                                                             | 24 |

| 2. PIN | N FUNCTIONS                                                                      | 26 |

| 2.1    | Port Functions                                                                   | 26 |

| 2.1.1  | 32-pin Products                                                                  | 26 |

| 2.2    | Functions other than port pins                                                   | 28 |

| 2.3    | Connection of Unused Pins                                                        |    |

| 2.4    | Pin Block Diagrams                                                               |    |

|        |                                                                                  |    |

| 3. CP  | U ARCHITECTURE                                                                   | 42 |

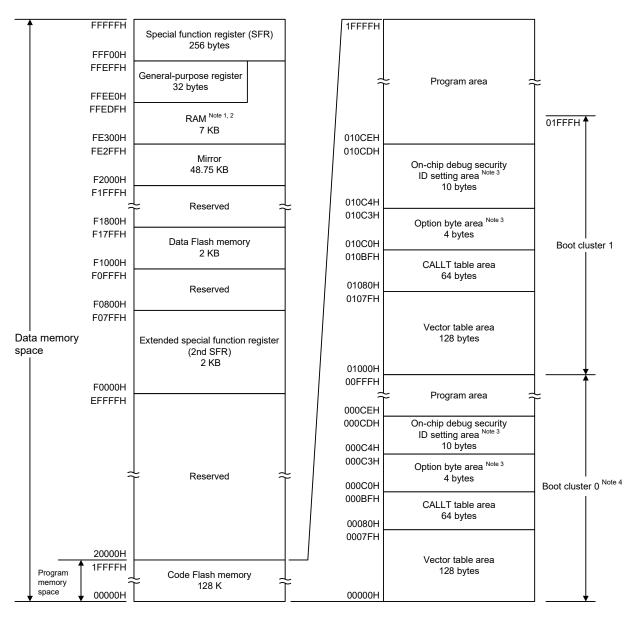

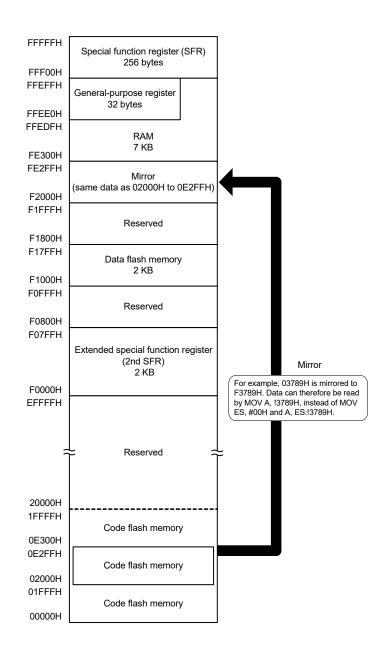

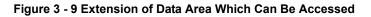

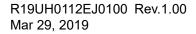

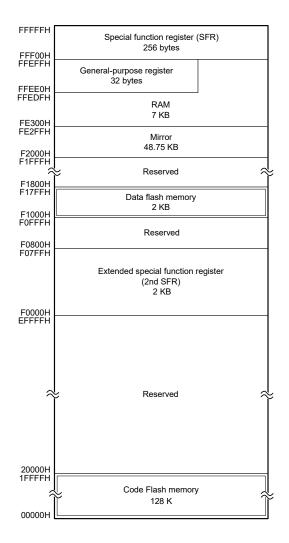

| 3.1    | Memory Space                                                                     | 43 |

| 3.1.1  | Internal program memory space                                                    | 45 |

| 3.1.2  | Mirror area                                                                      | 47 |

| 3.1.3  | Internal data memory space                                                       | 48 |

| 3.1.4  | Special function register (SFR) area                                             | 49 |

| 3.1.5  | Extended special function register (2nd SFR: 2nd Special Function Register) area | 49 |

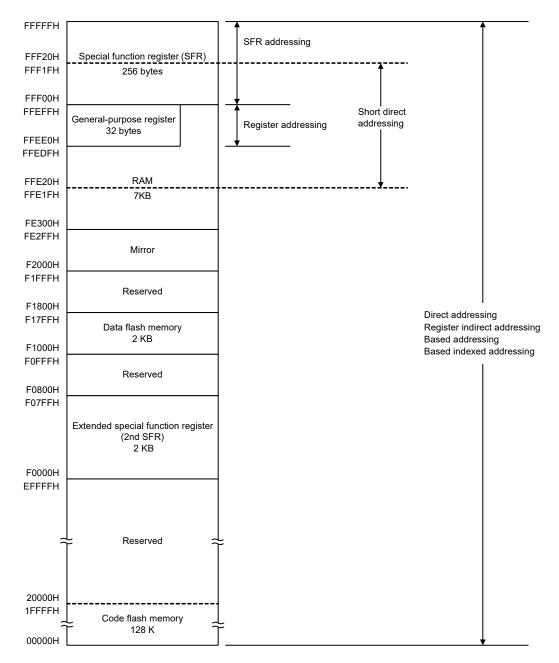

| 3.1.6  | Data memory addressing                                                           | 50 |

| 3.2    | Processor Registers                                                              | 51 |

| 3.2.1  | Control registers                                                                | 51 |

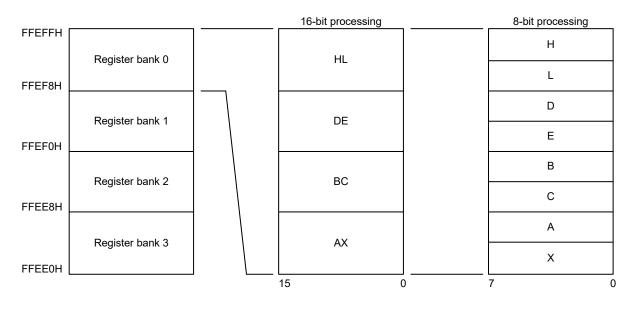

| 3.2.2  | General-purpose registers                                                        | 53 |

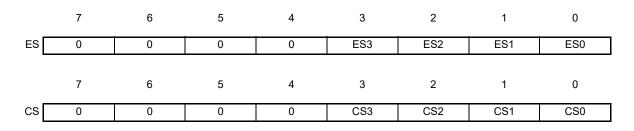

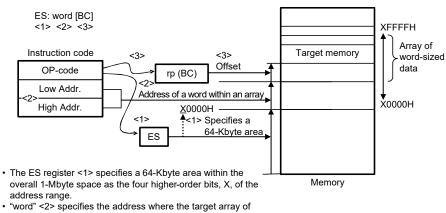

| 3.2.3  | ES and CS registers                                                              | 54 |

| 3.2.4  | Special function registers (SFRs)                                                | 55 |

| 3.2.5  | Extended special function registers (2nd SFRs: 2nd Special Function Registers)   | 59 |

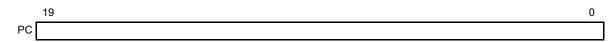

| 3.3    | Instruction Address Addressing                                                   | 66 |

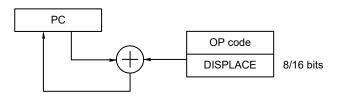

| 3.3.1  | Relative addressing                                                              | 66 |

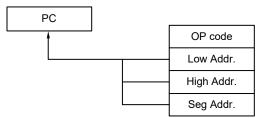

| 3.3.2  | Immediate addressing                                                             | 66 |

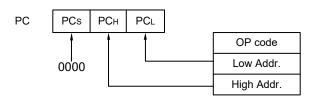

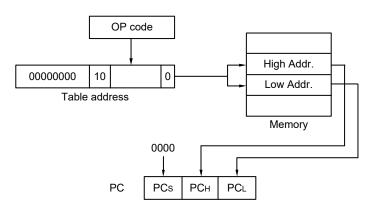

| 3.3.3  | Table indirect addressing                                                        | 67 |

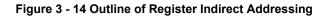

| 3.3.4  | Register indirect addressing                                                     | 67 |

| 3.4    | Addressing for Processing Data Addresses                                         | 68 |

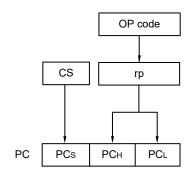

| 3.4.1  | Implied addressing                                                               |    |

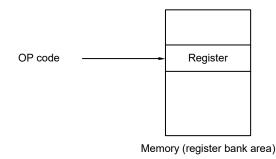

| 3.4.2  | Register addressing                                                              | 68 |

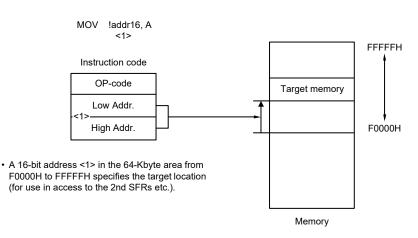

| 3.4.3  | Direct addressing                                                                | 69 |

| 3.4.4  | Short direct addressing                                                          | 70 |

| 3.4.5  | SFR addressing                                                                   | 71 |

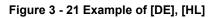

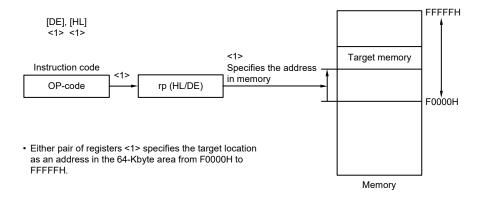

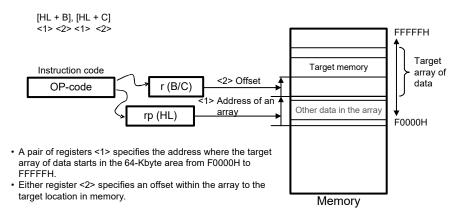

| 3.4.6  | Register indirect addressing                                                     | 72 |

| 3.4.7  | Based addressing                                                                 | 73 |

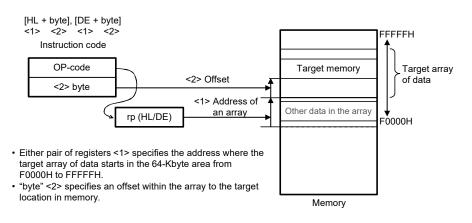

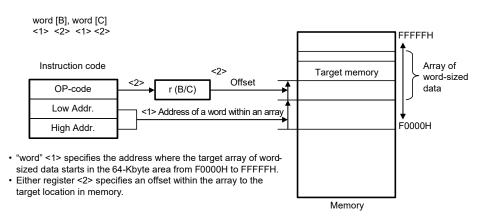

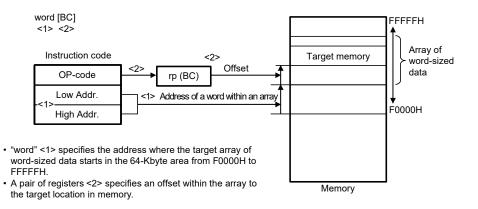

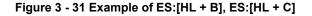

| 3.4.8          | Based indexed addressing                                                   |     |

|----------------|----------------------------------------------------------------------------|-----|

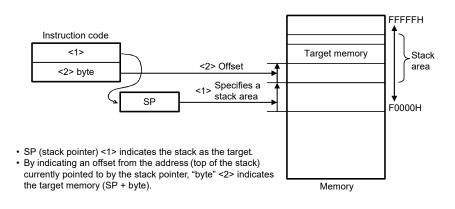

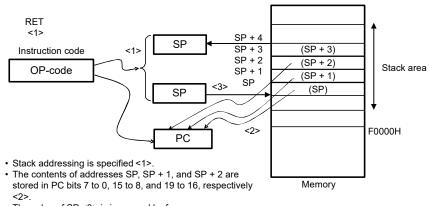

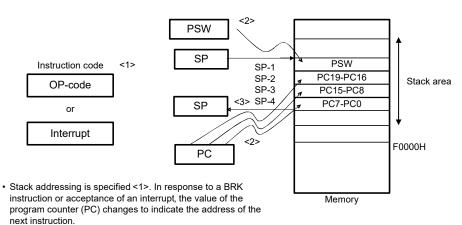

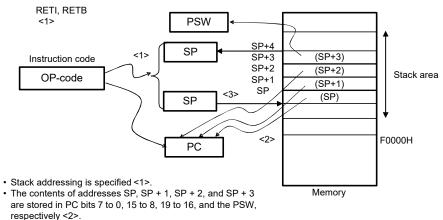

| 3.4.9          | Stack addressing                                                           | 77  |

|                |                                                                            |     |

|                | DRT FUNCTIONS                                                              |     |

| 4.1            | Port Functions                                                             |     |

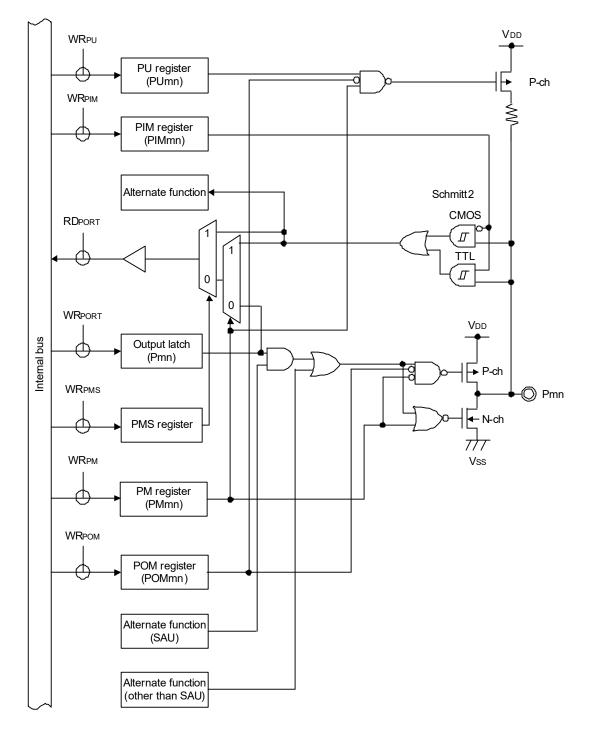

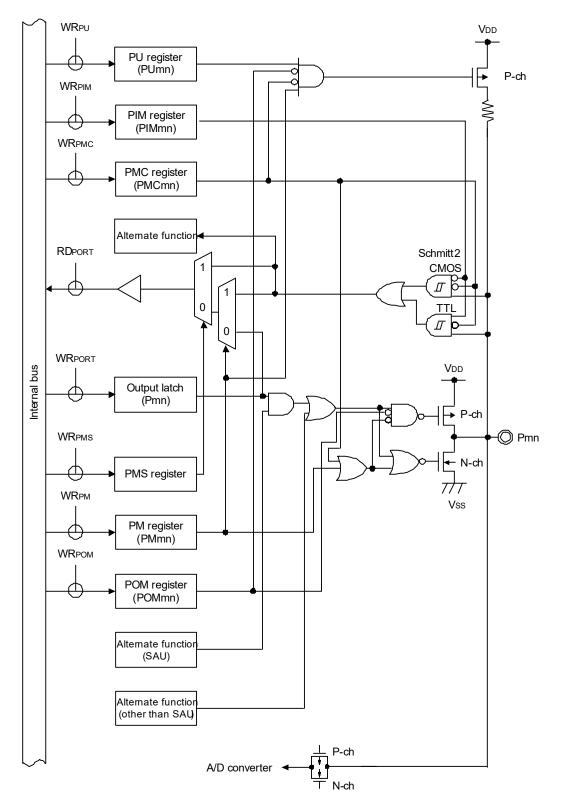

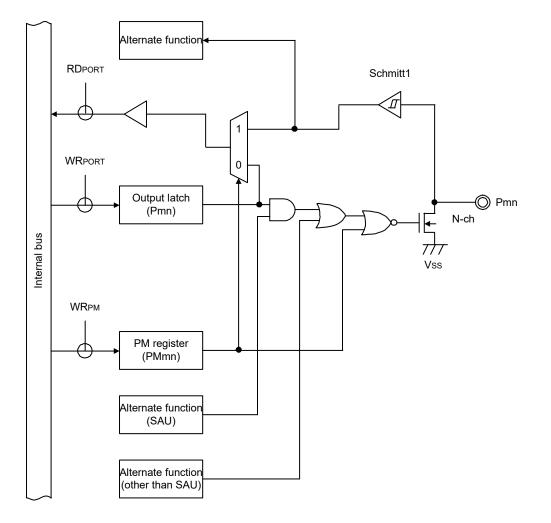

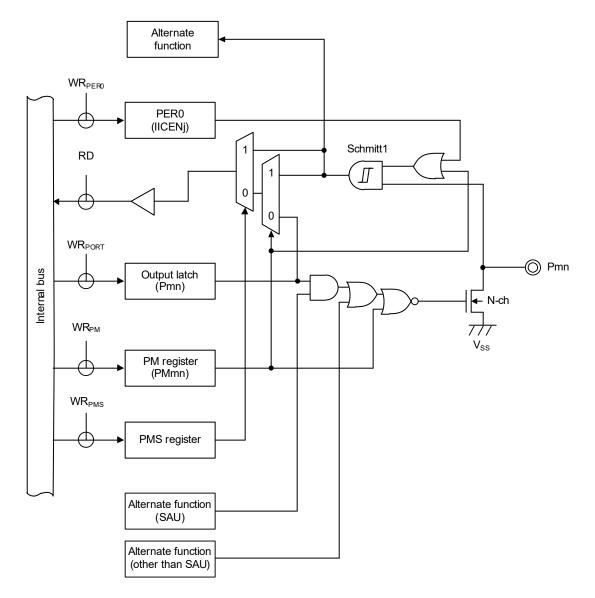

| 4.2            | Port Configuration                                                         |     |

| 4.2.1          | Port 0                                                                     |     |

| 4.2.2          |                                                                            |     |

| 4.2.3          | Port 4                                                                     |     |

| 4.2.4<br>4.2.5 |                                                                            | -   |

| 4.2.5<br>4.2.6 |                                                                            |     |

| 4.2.0          | Port 7<br>Port 12                                                          |     |

| 4.2.7          |                                                                            |     |

| 4.2.0          | Registers Controlling Port Function                                        |     |

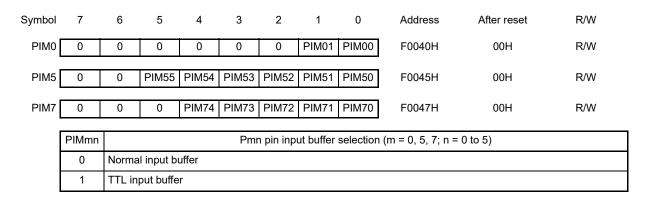

| 4.3.1          | Port mode registers (PMxx)                                                 |     |

| 4.3.2          |                                                                            |     |

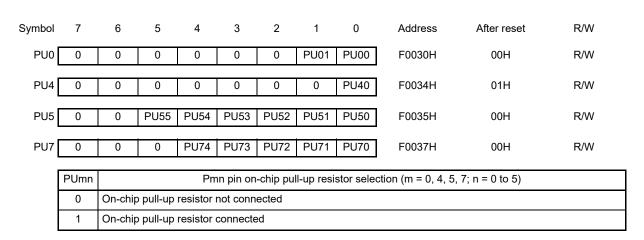

| 4.3.3          | Pull-up resistor option registers (PUxx)                                   |     |

| 4.3.4          |                                                                            |     |

| 4.3.5          |                                                                            |     |

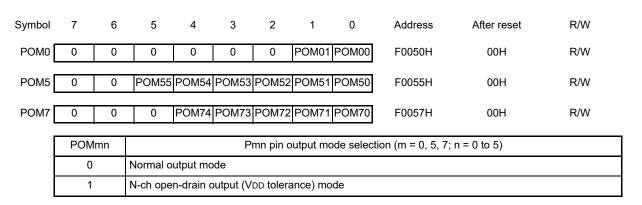

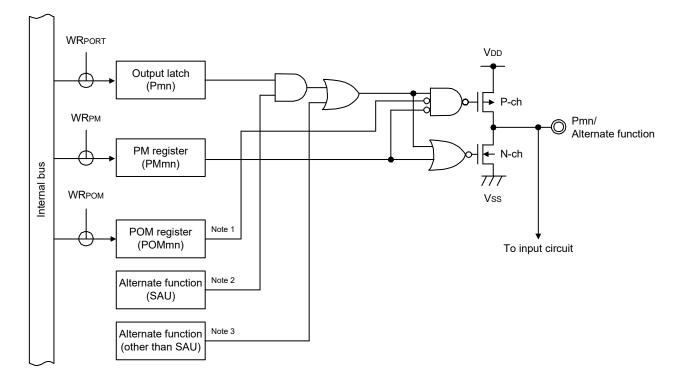

| 4.3.6          | Port mode control registers (PMCxx)                                        |     |

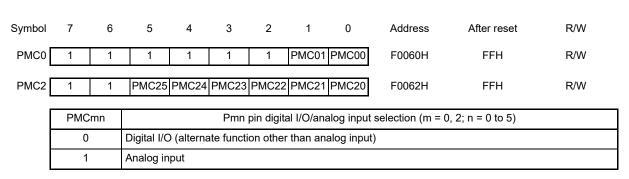

| 4.4            | Port Function Operations                                                   |     |

| 4.4.1          | Writing to I/O port                                                        |     |

| 4.4.2          |                                                                            |     |

| 4.4.3          | Operations on I/O port                                                     | 89  |

| 4.4.4          | Handling different potential (1.8 V, 2.5 V) by using I/O buffers           |     |

| 4.5            | Register Settings When Using Alternate Function                            |     |

| 4.5.1          | Basic concept when using alternate function                                |     |

| 4.5.2          | Register settings for alternate function whose output function is not used | 93  |

| 4.5.3          | Register setting examples for used port and alternate functions            |     |

| 4.6            | Cautions When Using Port Function                                          |     |

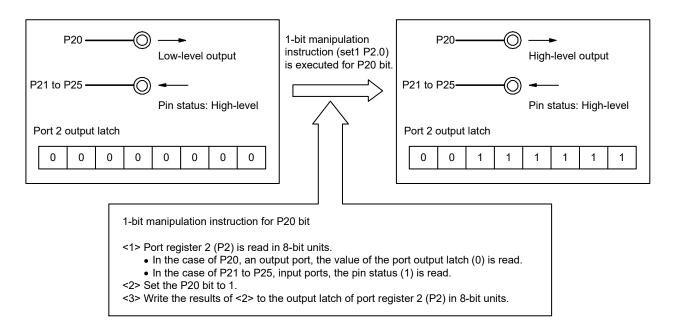

| 4.6.1          | Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)        |     |

| 4.6.2          | Notes on specifying the pin settings                                       | 100 |

| F ()           |                                                                            | 101 |

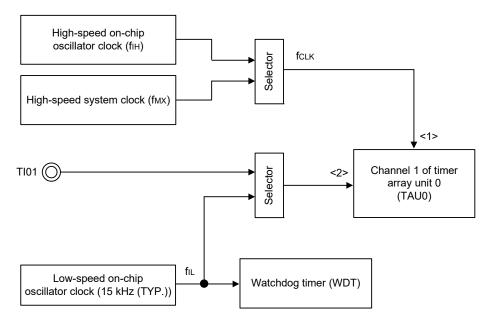

|                | OCK GENERATOR Functions of Clock Generator                                 |     |

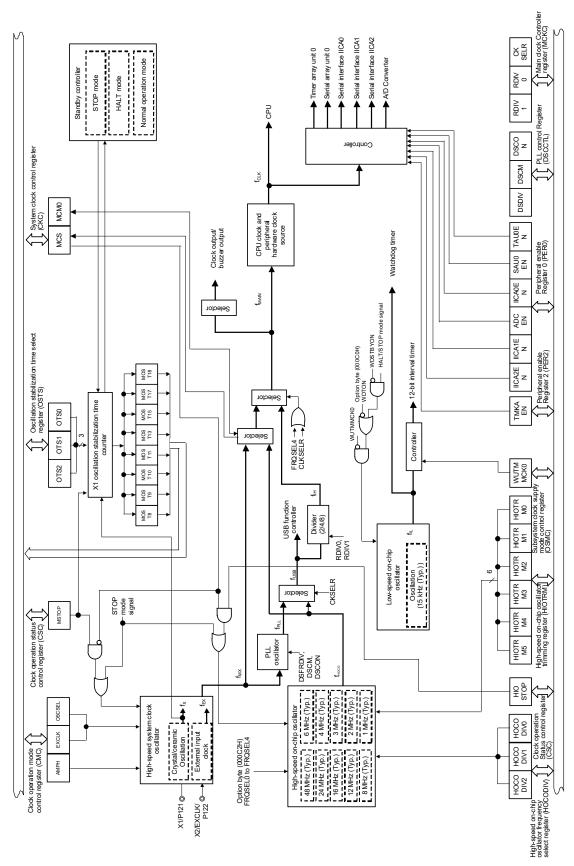

| 5.1<br>5.2     | Configuration of Clock Generator                                           |     |

| 5.2<br>5.3     | Registers Controlling Clock Generator                                      |     |

| 5.3.1          | Clock operation mode control register (CMC)                                |     |

| 5.3.2          |                                                                            |     |

| 5.3.3          |                                                                            |     |

| 5.3.4          |                                                                            |     |

| 5.3.5          |                                                                            |     |

| 5.3.6          |                                                                            |     |

| 5.3.7          |                                                                            |     |

| 5.3.8          |                                                                            |     |

| 5.3.9          |                                                                            |     |

| 5.3.1          |                                                                            |     |

| 5.3.1          | 1 Main clock control register (MCKC)                                       | 120 |

| 5.3.12 | USB clock selection register (UCKSEL)                                       | 121 |

|--------|-----------------------------------------------------------------------------|-----|

| 5.4    | System Clock Oscillator                                                     | 122 |

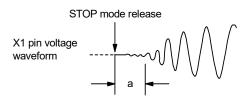

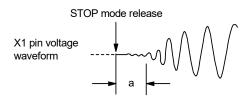

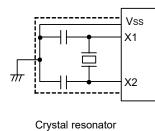

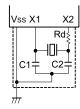

| 5.4.1  | X1 oscillator                                                               | 122 |

| 5.4.2  | High-speed on-chip oscillator                                               | 125 |

| 5.4.3  | Low-speed on-chip oscillator                                                | 125 |

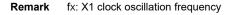

| 5.4.4  | PLL (Phase Locked Loop)                                                     | 125 |

| 5.5    | Clock Generator Operation                                                   | 126 |

| 5.6    | Controlling Clock                                                           | 128 |

| 5.6.1  | Example of setting high-speed on-chip oscillator                            | 128 |

| 5.6.2  | Example of setting X1 oscillation clock                                     | 130 |

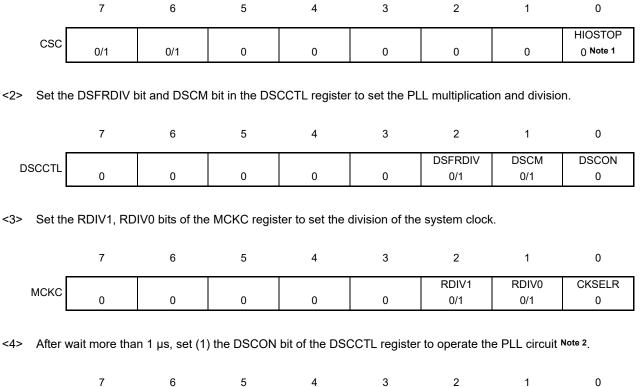

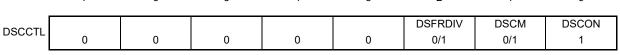

| 5.6.3  | Example of setting PLL circuit                                              | 131 |

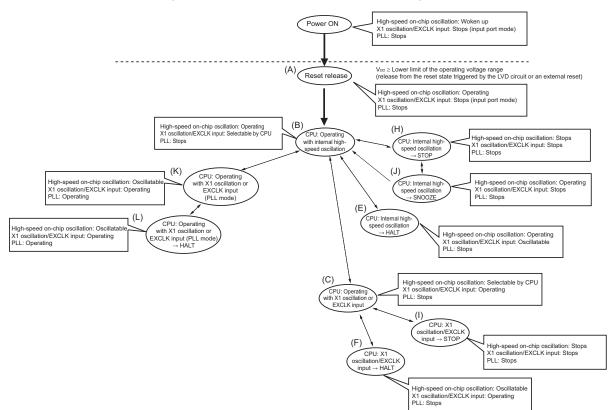

| 5.6.4  | CPU clock status transition diagram                                         | 133 |

| 5.6.5  | Condition before changing CPU clock and processing after changing CPU clock | 138 |

| 5.6.6  | Time required for switchover of CPU clock and system clock                  | 140 |

| 5.6.7  | Conditions before clock oscillation is stopped                              | 141 |

| 5.7    | Resonator and Oscillator Constants                                          | 142 |

|        |                                                                             |     |

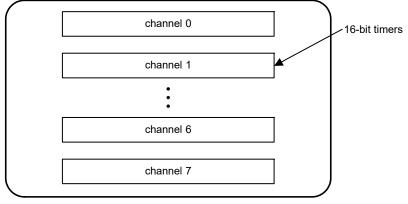

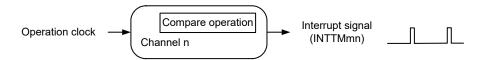

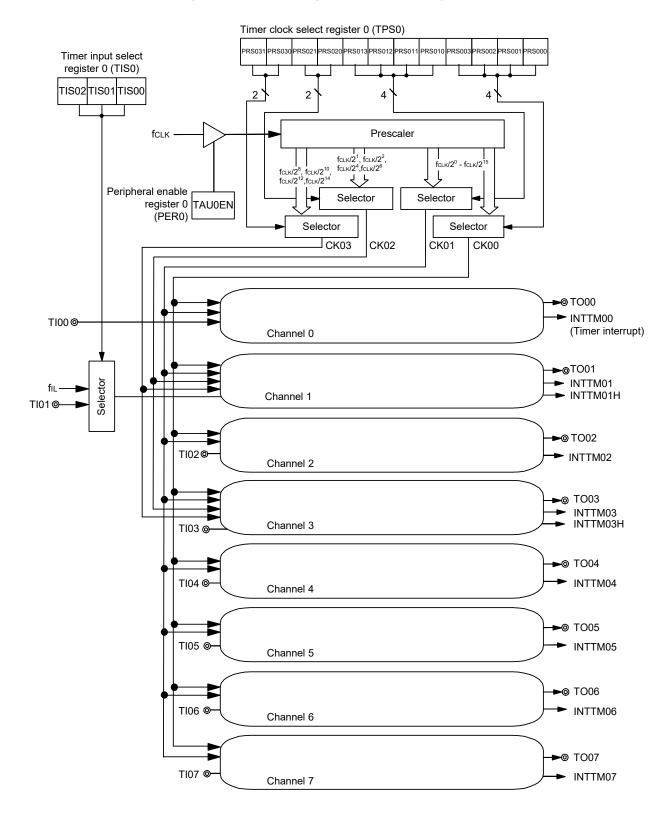

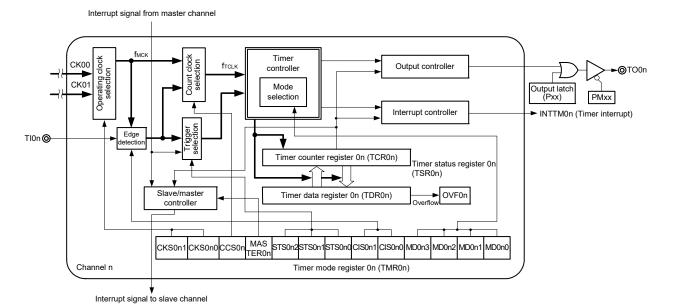

| 6. TIM | ER ARRAY UNIT                                                               | 145 |

| 6.1    | Functions of Timer Array Unit                                               | 146 |

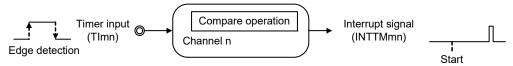

| 6.1.1  | Independent channel operation function                                      | 146 |

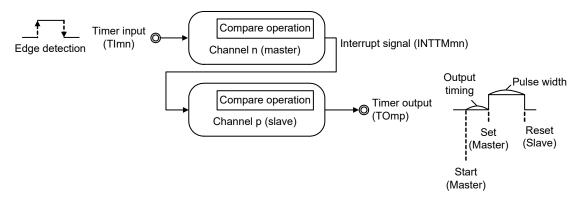

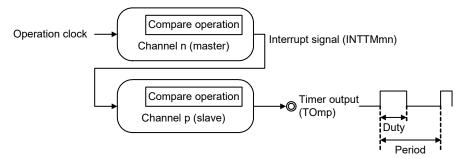

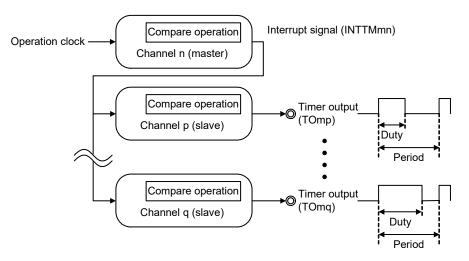

| 6.1.2  | Simultaneous channel operation function                                     | 147 |

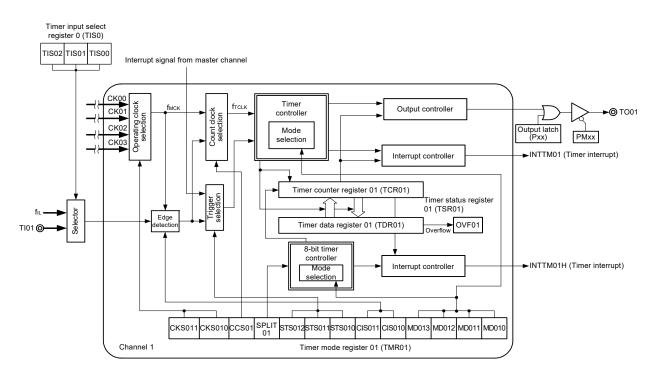

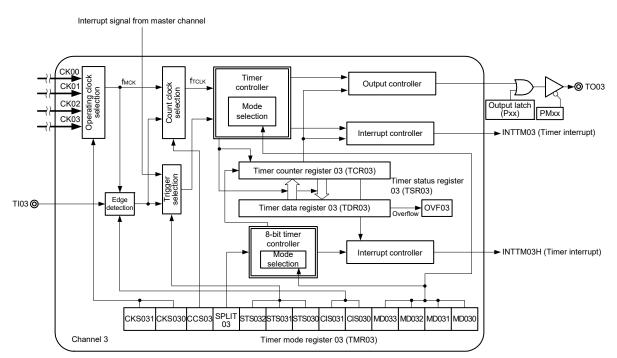

| 6.1.3  | 8-bit timer operation function (channels 1 and 3 only)                      | 148 |

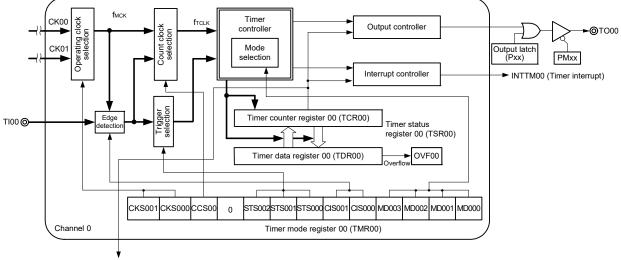

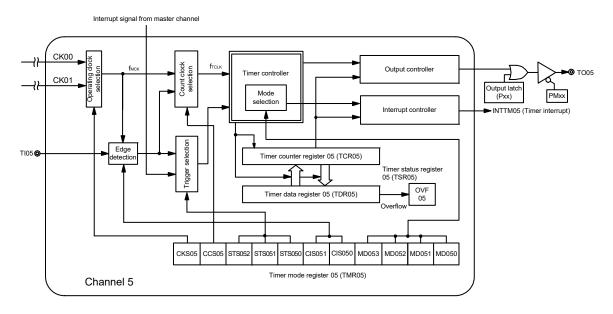

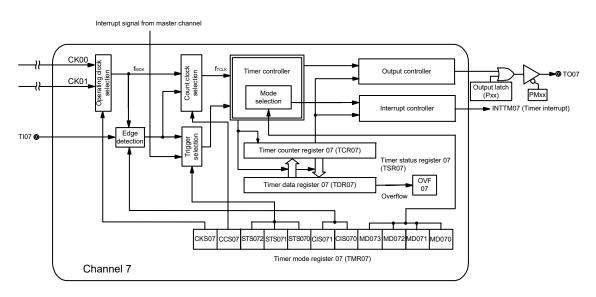

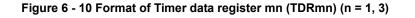

| 6.2    | Configuration of Timer Array Unit                                           | 149 |

| 6.2.1  | Timer count register mn (TCRmn)                                             | 155 |

| 6.2.2  | Timer data register mn (TDRmn)                                              | 157 |

| 6.3    | Registers Controlling Timer Array Unit                                      | 158 |

| 6.3.1  | Peripheral enable register 0 (PER0)                                         | 159 |

| 6.3.2  | Timer clock select register m (TPSm)                                        | 160 |

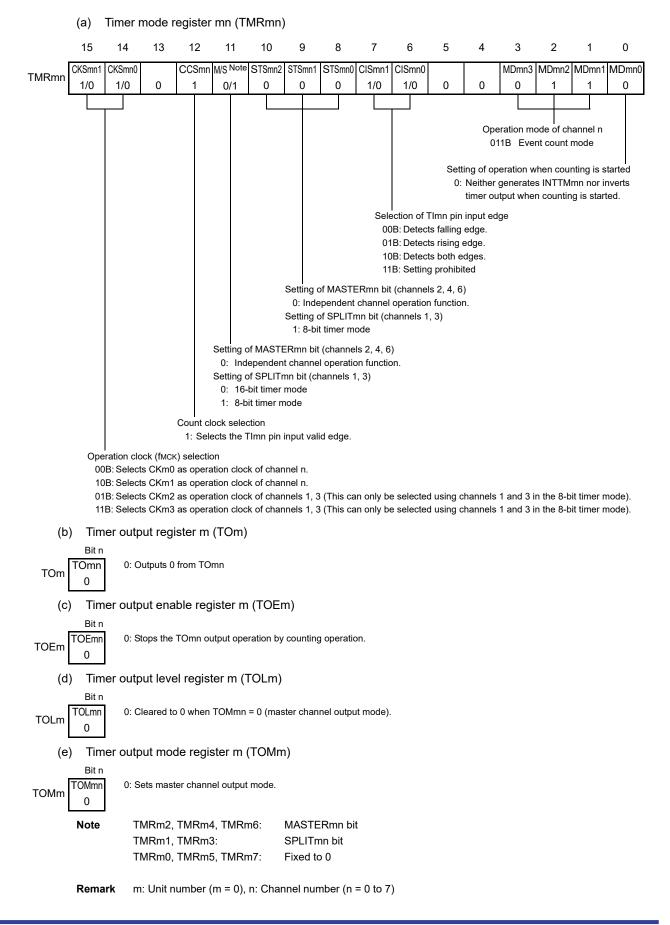

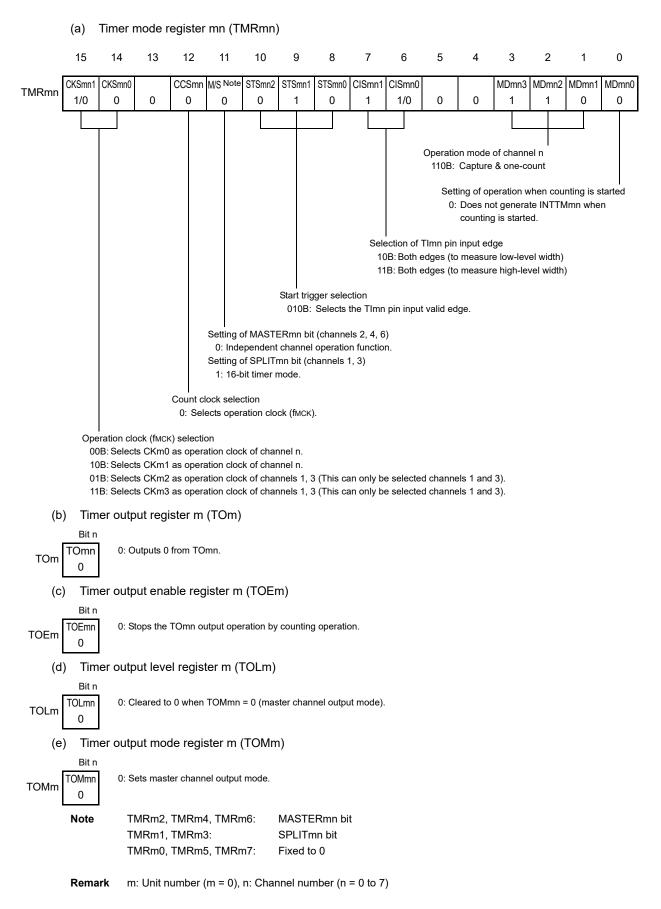

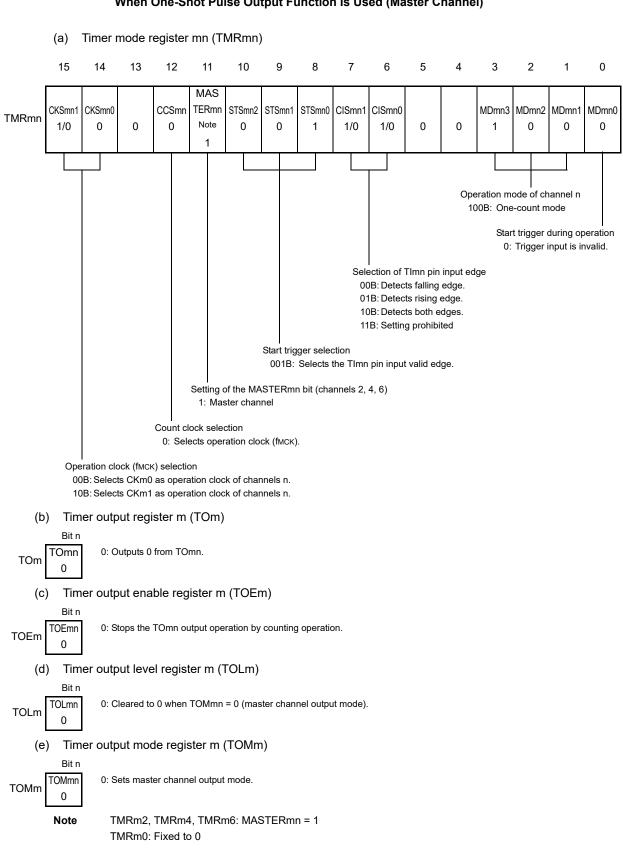

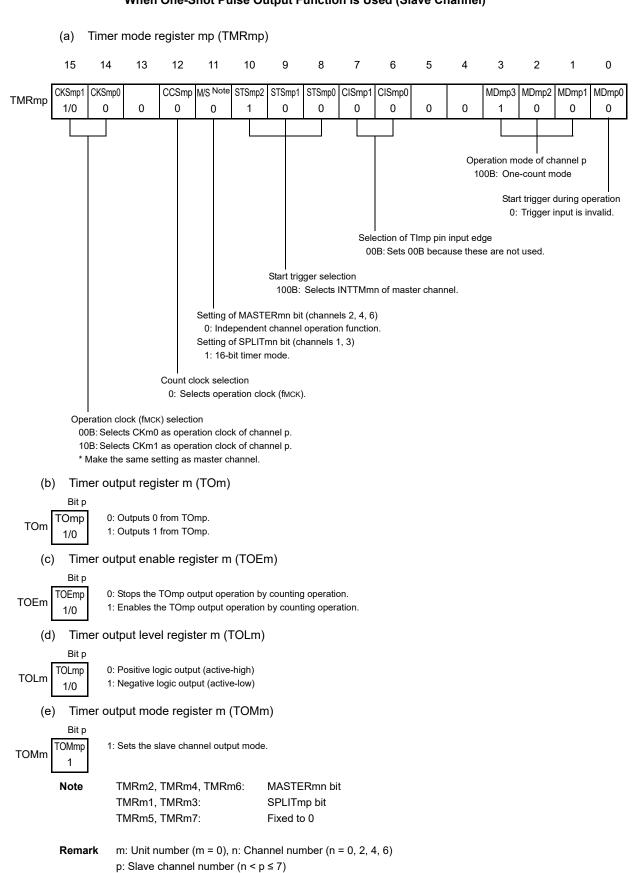

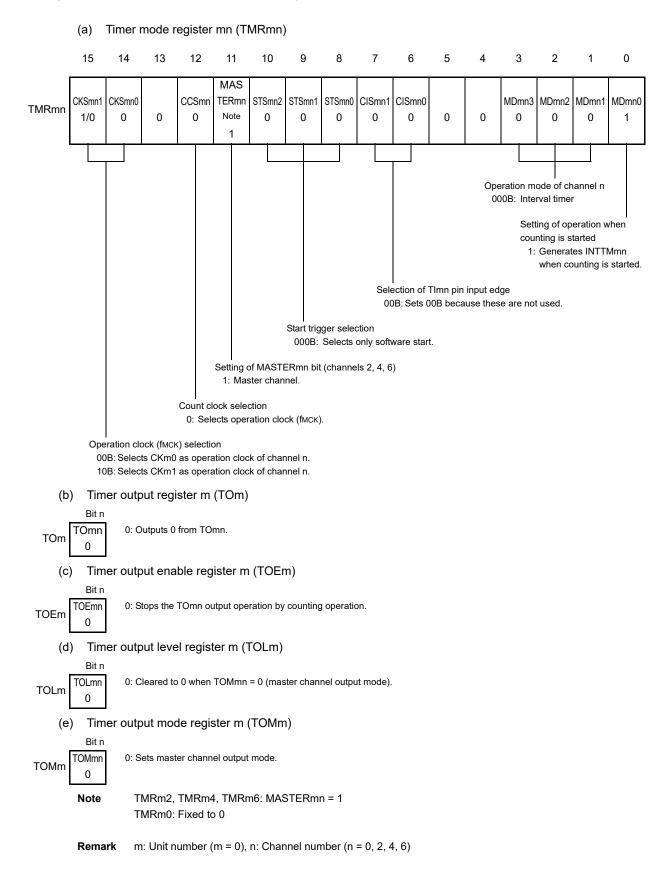

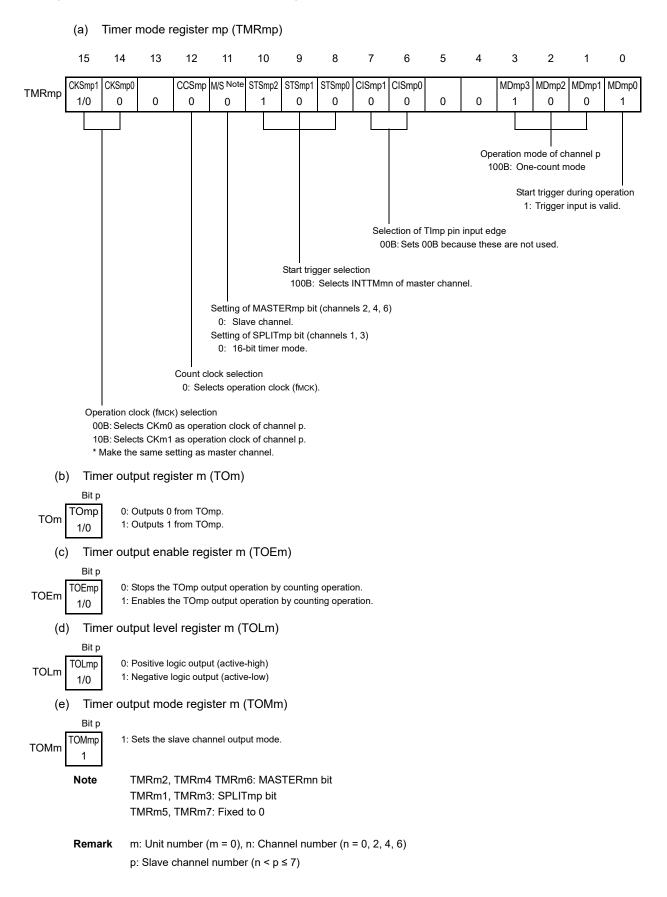

| 6.3.3  | Timer mode register mn (TMRmn)                                              | 163 |

| 6.3.4  | Timer status register mn (TSRmn)                                            | 168 |

| 6.3.5  | Timer channel enable status register m (TEm)                                | 169 |

| 6.3.6  | Timer channel start register m (TSm)                                        | 170 |

| 6.3.7  | Timer channel stop register m (TTm)                                         | 171 |

| 6.3.8  | Timer input select register 0 (TIS0)                                        | 172 |

| 6.3.9  | Timer output enable register m (TOEm)                                       | 173 |

| 6.3.10 |                                                                             |     |

| 6.3.11 | Timer output level register m (TOLm)                                        |     |

| 6.3.12 |                                                                             |     |

| 6.3.13 | 5 ( )                                                                       |     |

| 6.3.14 |                                                                             |     |

| 6.4    | Basic Rules of Timer Array Unit                                             |     |

| 6.4.1  | Basic rules of simultaneous channel operation function                      |     |

| 6.4.2  | Basic rules of 8-bit timer operation function (channels 1 and 3 only)       |     |

| 6.5    | Operation of Counter                                                        |     |

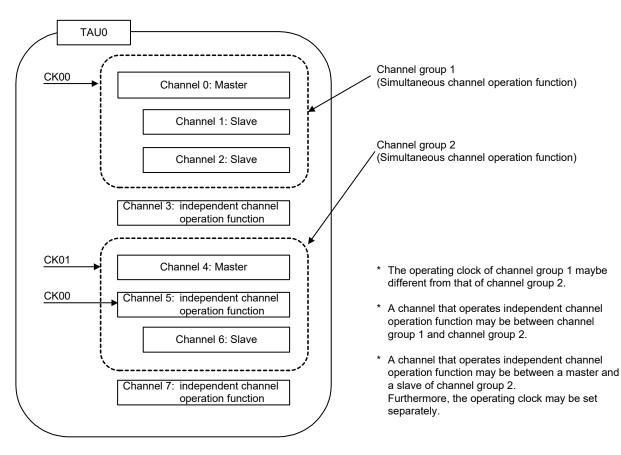

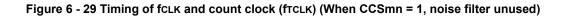

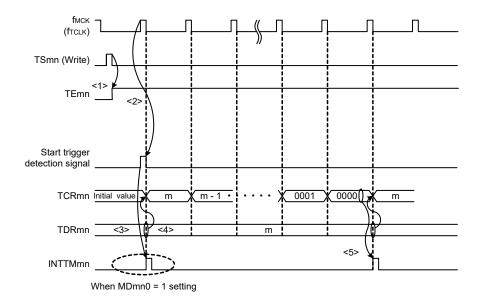

| 6.5.1  | Count clock (fTCLK)                                                         |     |

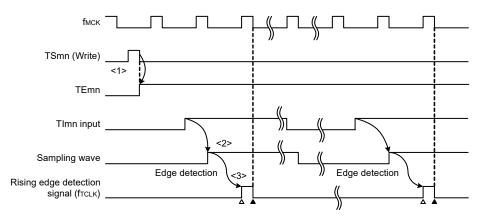

| 6.5.2  | Start timing of counter                                                     |     |

| 6.5.3  | Operation of counter                                                        |     |

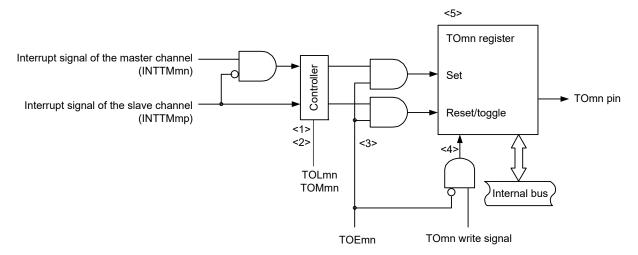

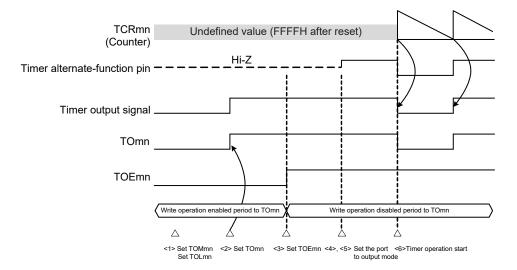

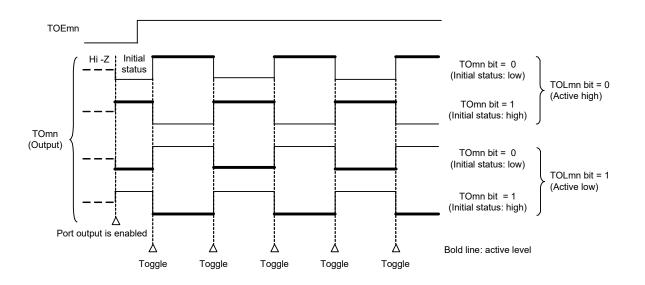

| 6.6    | Channel Output (TOmn pin) Control                                           |     |

| 6.6.1  | TOmn pin output circuit configuration                                       | 191 |

| 6.6.2      | TOmn Pin Output Setting                                                                                      | 192   |

|------------|--------------------------------------------------------------------------------------------------------------|-------|

| 6.6.3      | Cautions on Channel Output Operation                                                                         | 193   |

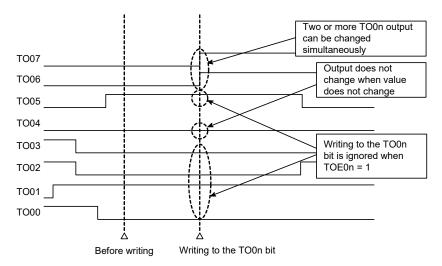

| 6.6.4      | Collective manipulation of TOmn bit                                                                          | 198   |

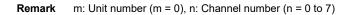

| 6.6.5      | Timer Interrupt and TOmn Pin Output at Operation Start                                                       | 199   |

| 6.7        | Timer Input (TImn) Control                                                                                   | 200   |

| 6.7.1      | TImn input circuit configuration                                                                             | 200   |

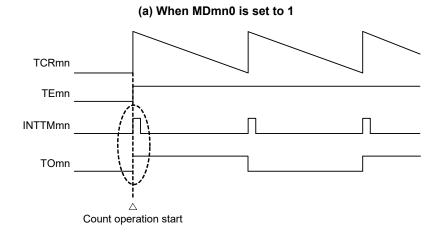

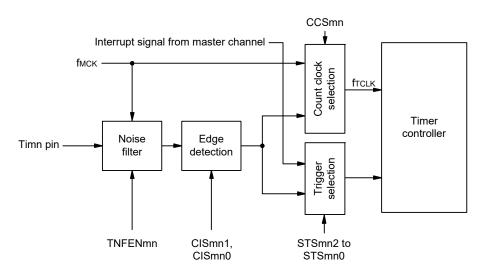

| 6.7.2      | Noise filter                                                                                                 | 200   |

| 6.7.3      | Cautions on channel input operation                                                                          | 201   |

| 6.8        | Independent Channel Operation Function of Timer Array Unit                                                   | 202   |

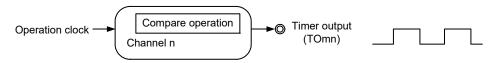

| 6.8.1      | Operation as interval timer/square wave output                                                               | 202   |

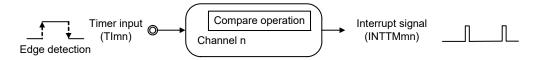

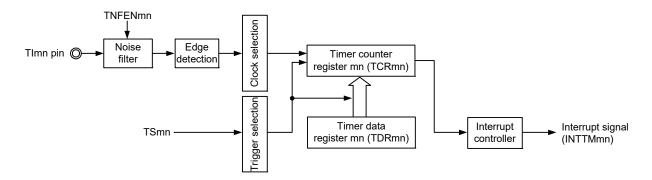

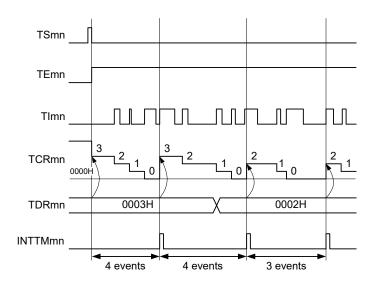

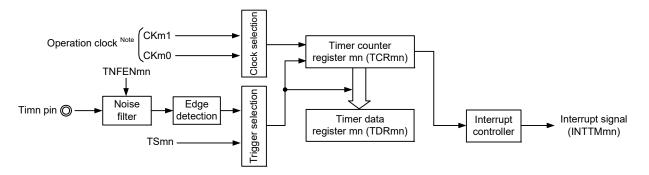

| 6.8.2      | Operation as external event counter                                                                          |       |

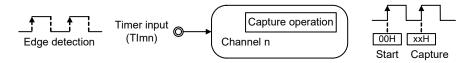

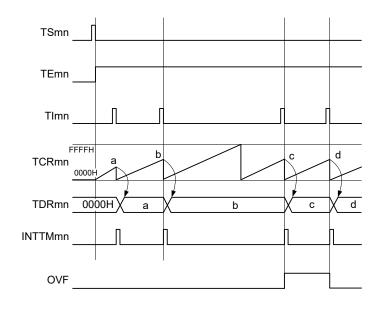

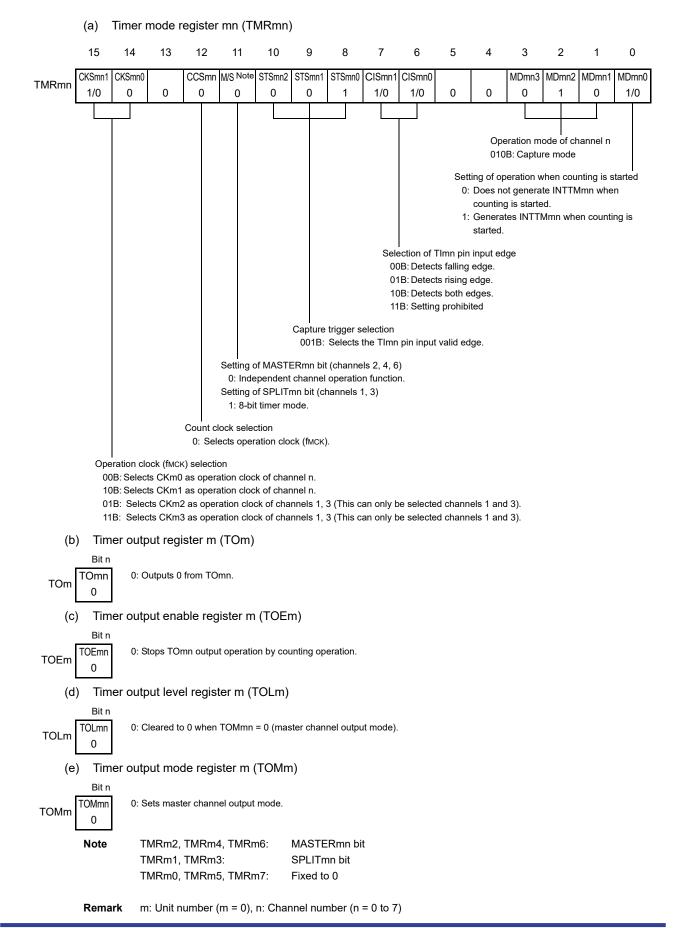

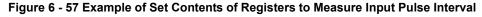

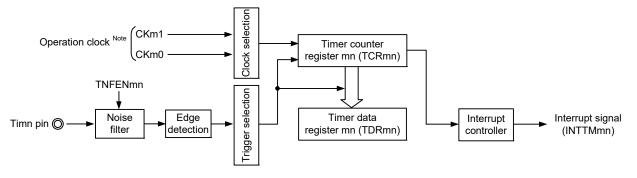

| 6.8.3      | Operation as input pulse interval measurement                                                                | . 211 |

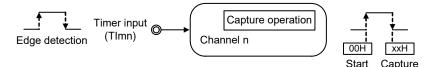

| 6.8.4      | Operation as input signal high-/low-level width measurement                                                  | . 215 |

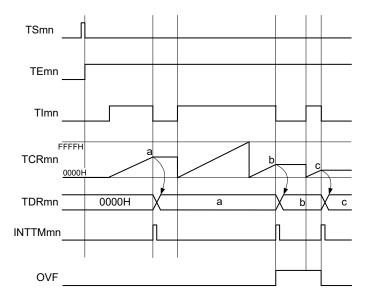

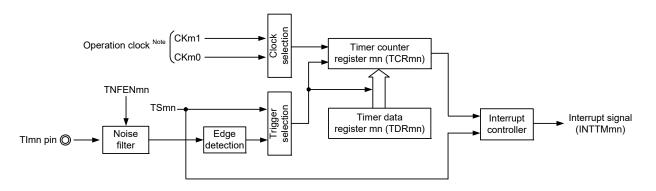

| 6.8.5      | Operation as delay counter                                                                                   |       |

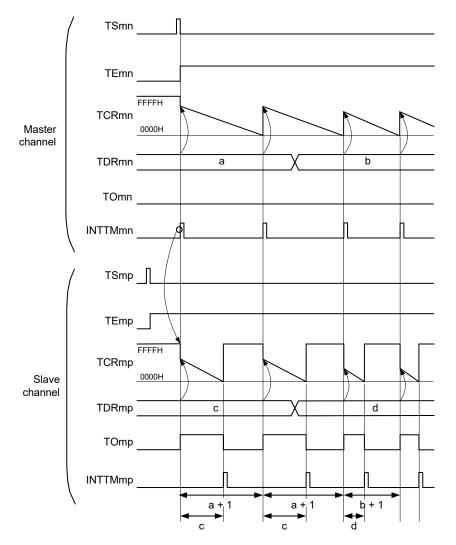

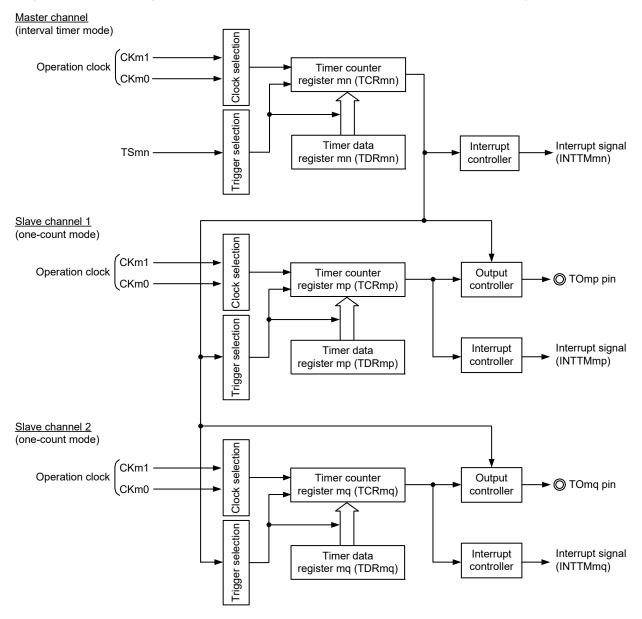

| 6.9        | Simultaneous Channel Operation Function of Timer Array Unit                                                  | 223   |

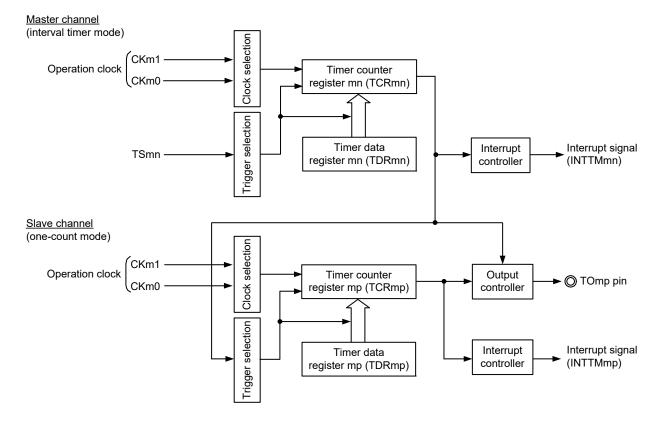

| 6.9.1      | Operation as one-shot pulse output function                                                                  | 223   |

| 6.9.2      | Operation as PWM function                                                                                    | 230   |

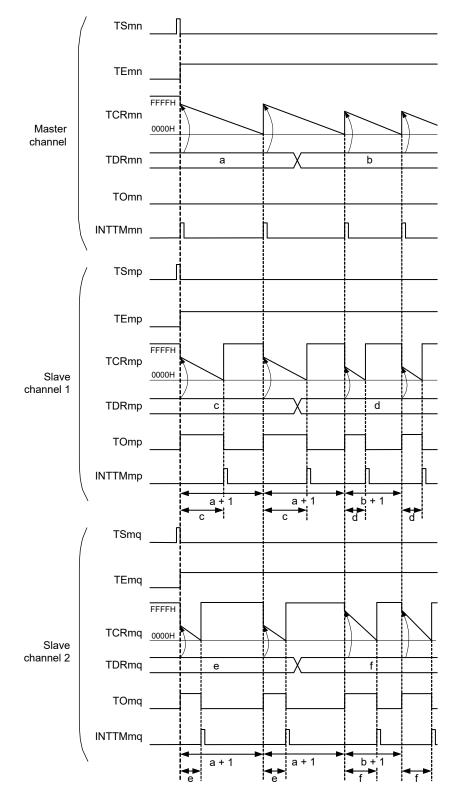

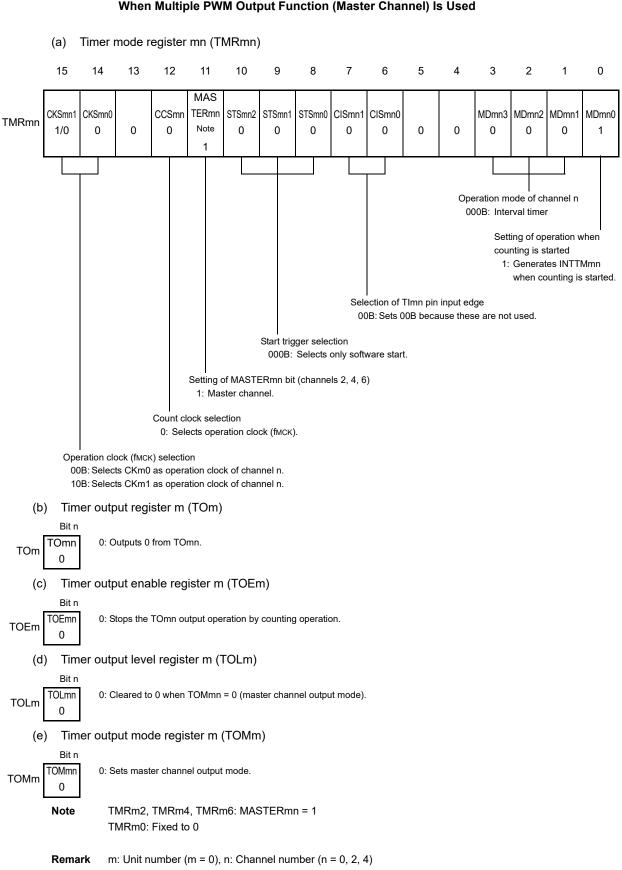

| 6.9.3      | Operation as multiple PWM output function                                                                    | 237   |

| 6.10       | Cautions When Using Timer Array Unit                                                                         |       |

| 6.10.1     | 1 Cautions When Using Timer output                                                                           | 245   |

|            |                                                                                                              |       |

| 7. 12-     | BIT INTERVAL TIMER                                                                                           | 246   |

| 7.1        | Functions of 12-bit Interval Timer                                                                           |       |

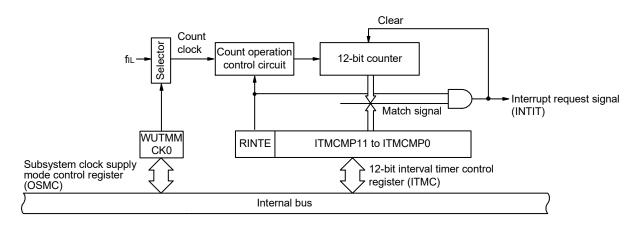

| 7.2        | Configuration of 12-bit Interval Timer                                                                       |       |

| 7.3        | Registers Controlling 12-bit Interval Timer                                                                  |       |

| 7.3.1      | Peripheral enable register 2 (PER2)                                                                          |       |

| 7.3.2      | Peripheral reset control register 2 (PRR2)                                                                   |       |

| 7.3.3      | Subsystem clock supply mode control register (OSMC)                                                          |       |

| 7.3.4      | 12-bit interval timer control register (ITMC)                                                                |       |

| 7.4        | 12-bit Interval Timer Operation                                                                              |       |

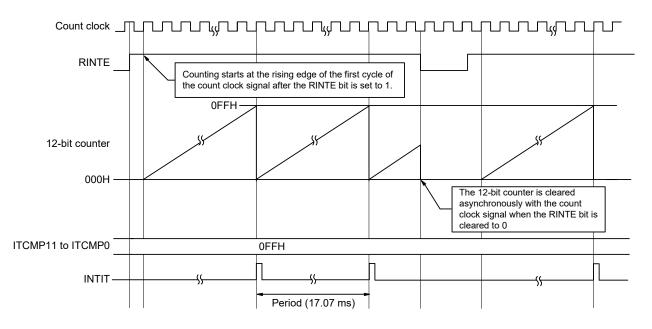

| 7.4.1      | 12-bit interval timer operation timing                                                                       | 250   |

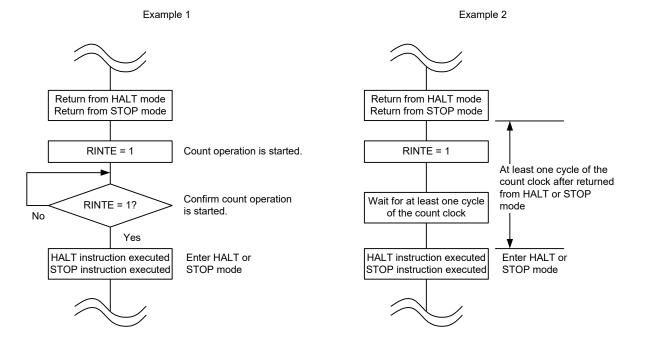

| 7.4.2      | Start of count operation and re-enter to HALT/STOP mode after returned from                                  | 054   |

|            | HALT/STOP mode                                                                                               | . 251 |

| 8. CL      | OCK OUTPUT/BUZZER OUTPUT CONTROLLER                                                                          | 252   |

| 8.1        |                                                                                                              |       |

|            | Functions of Clock Output/Buzzer Output Controller<br>Configuration of Clock Output/Buzzer Output Controller |       |

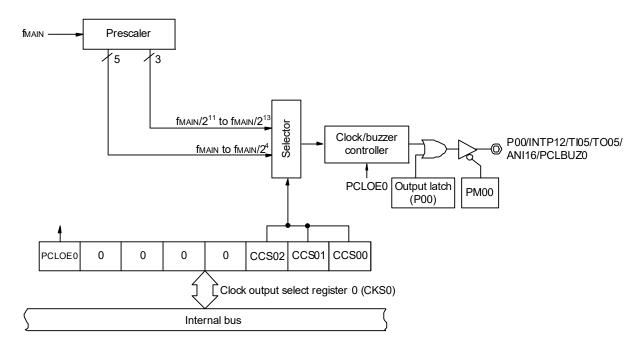

| 8.2<br>8.3 | Registers Controlling Clock Output/Buzzer Output Controller                                                  |       |

| 8.3.1      | Clock output select registers n (CKSn)                                                                       |       |

| 8.3.1      | Registers controlling port functions of pins to be used for clock or buzzer output                           |       |

| 8.4        | Operations of Clock Output/Buzzer Output Controller                                                          |       |

| 8.4.1      | Operation as output pin                                                                                      |       |

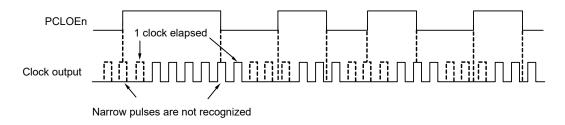

| 8.5        | Cautions of clock output/buzzer output controller                                                            |       |

| 0.0        |                                                                                                              | 201   |

| 9. WA      | ATCHDOG TIMER                                                                                                | 258   |

| 9.1        | Functions of Watchdog Timer                                                                                  | 258   |

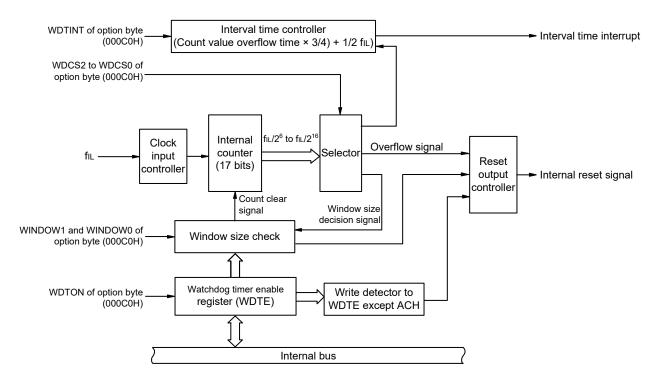

| 9.2        | Configuration of Watchdog Timer                                                                              |       |

| 9.3        | Register Controlling Watchdog Timer                                                                          |       |

| 9.3.1      | Watchdog timer enable register (WDTE)                                                                        |       |

|            |                                                                                                              |       |

| 9.4     | Operation of Watchdog Timer                                             | . 261 |

|---------|-------------------------------------------------------------------------|-------|

| 9.4.1   | Controlling operation of watchdog timer                                 | . 261 |

| 9.4.2   | Setting overflow time of watchdog timer                                 | . 262 |

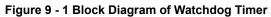

| 9.4.3   | Setting window open period of watchdog timer                            | . 263 |

| 9.4.4   | Setting watchdog timer interval interrupt                               | . 264 |

|         |                                                                         |       |

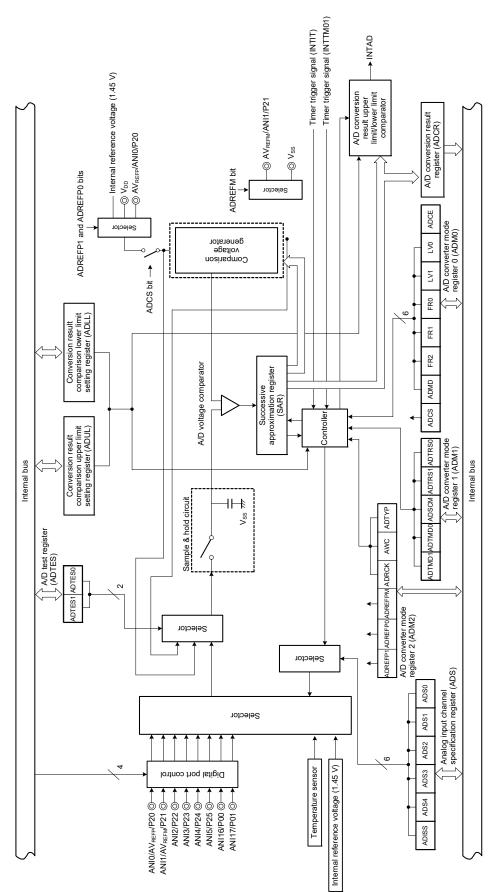

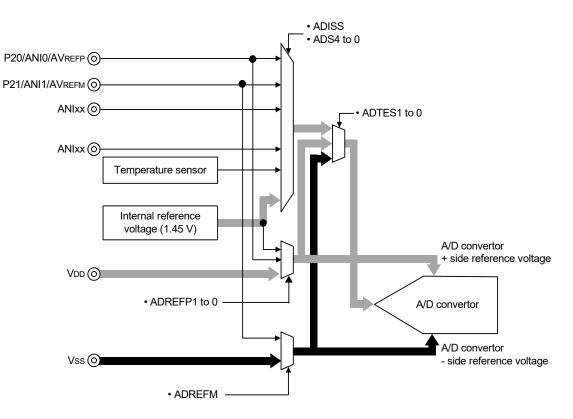

| 10. A/E | OONVERTER                                                               | . 265 |

| 10.1    | Function of A/D Converter                                               | . 265 |

| 10.2    | Configuration of A/D Converter                                          | . 268 |

| 10.3    | Registers Controlling A/D Converter                                     | . 270 |

| 10.3.1  | Peripheral enable register 0 (PER0)                                     | . 271 |

| 10.3.2  | A/D converter mode register 0 (ADM0)                                    | . 272 |

| 10.3.3  | A/D converter mode register 1 (ADM1)                                    | . 278 |

| 10.3.4  | A/D converter mode register 2 (ADM2)                                    | . 279 |

| 10.3.5  | 5 10-bit A/D conversion result register (ADCR)                          | . 281 |

| 10.3.6  | 8-bit A/D conversion result register (ADCRH)                            | . 282 |

| 10.3.7  | Analog input channel specification register (ADS)                       | . 283 |

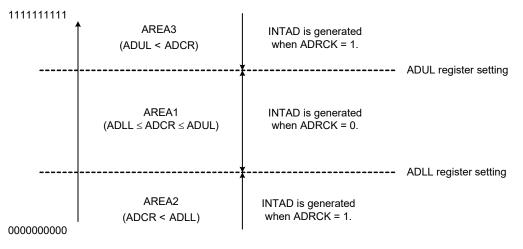

| 10.3.8  | Conversion result comparison upper limit setting register (ADUL)        | . 285 |

| 10.3.9  | O Conversion result comparison lower limit setting register (ADLL)      | . 285 |

| 10.3.1  | 0 A/D test register (ADTES)                                             | . 286 |

| 10.3.1  | 1 Registers controlling port function of analog input pins              | . 286 |

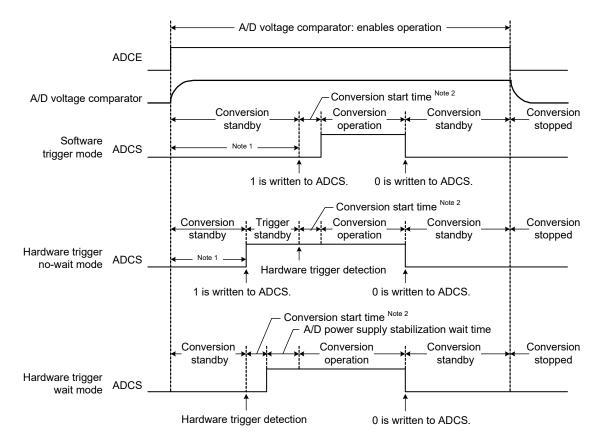

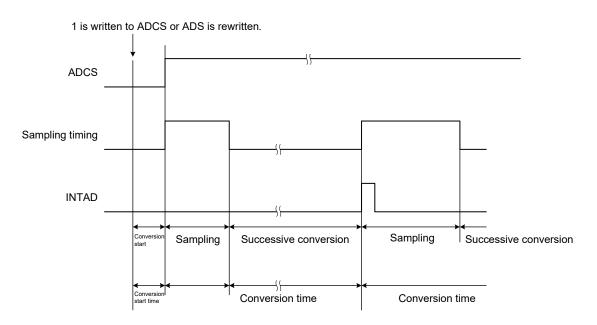

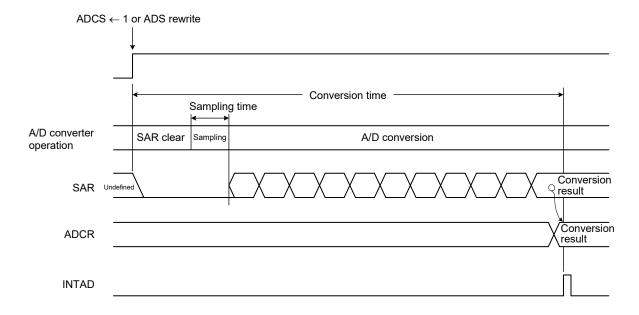

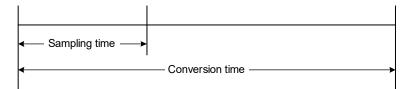

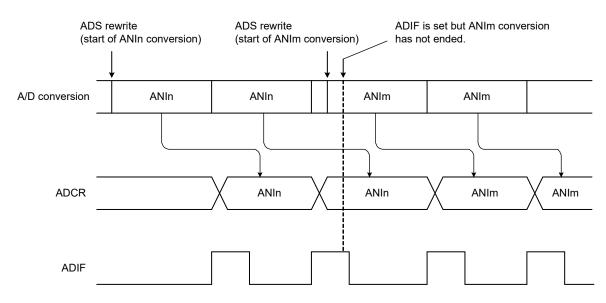

| 10.4    | A/D Converter Conversion Operations                                     | . 287 |

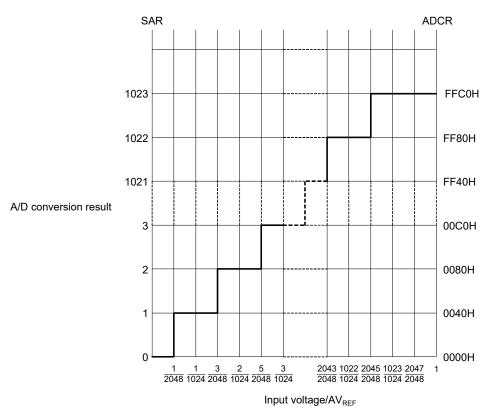

| 10.5    | Input Voltage and Conversion Results                                    | . 289 |

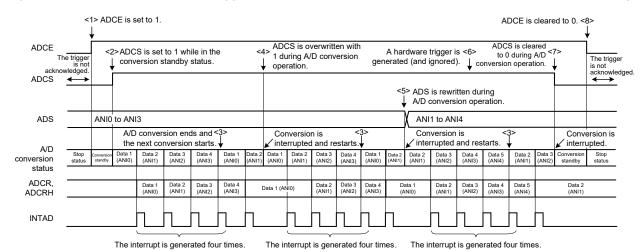

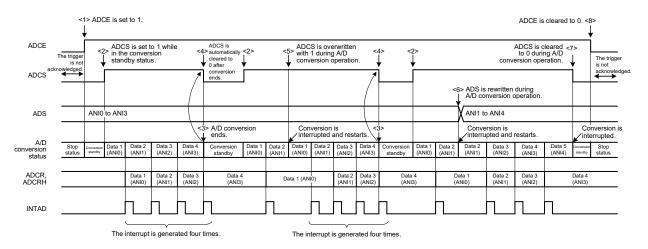

| 10.6    | A/D Converter Operation Modes                                           | . 290 |

| 10.6.1  | Software trigger mode (select mode, sequential conversion mode)         | . 290 |

| 10.6.2  | 2 Software trigger mode (select mode, one-shot conversion mode)         | . 291 |

| 10.6.3  | Software trigger mode (scan mode, sequential conversion mode)           | . 292 |

| 10.6.4  | Software trigger mode (scan mode, one-shot conversion mode)             | . 293 |

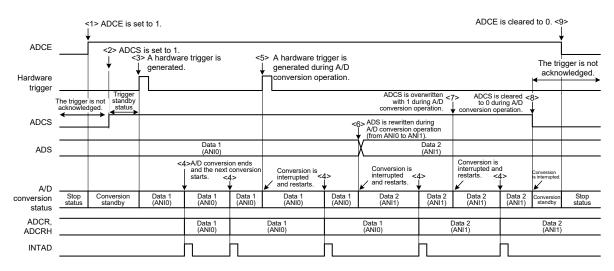

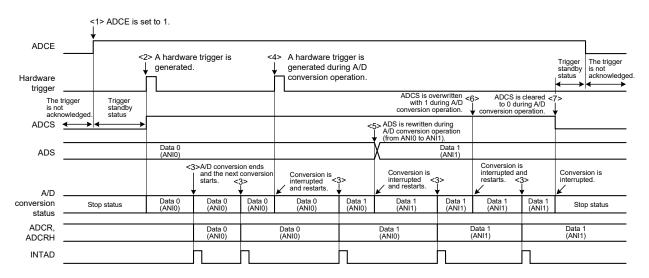

| 10.6.5  | Hardware trigger no-wait mode (select mode, sequential conversion mode) | . 294 |

| 10.6.6  | B Hardware trigger no-wait mode (select mode, one-shot conversion mode) | . 295 |

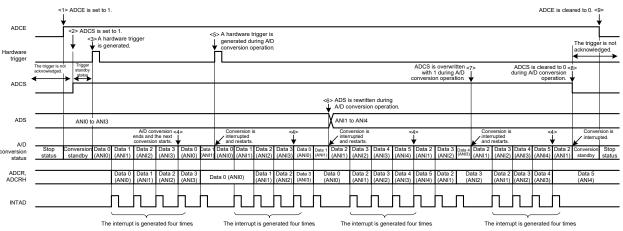

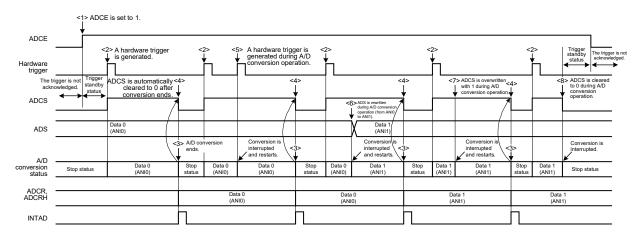

| 10.6.7  | ' Hardware trigger no-wait mode (scan mode, sequential conversion mode) | 296   |

| 10.6.8  | B Hardware trigger no-wait mode (scan mode, one-shot conversion mode)   | . 297 |

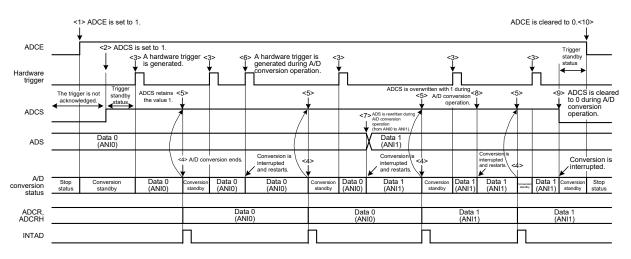

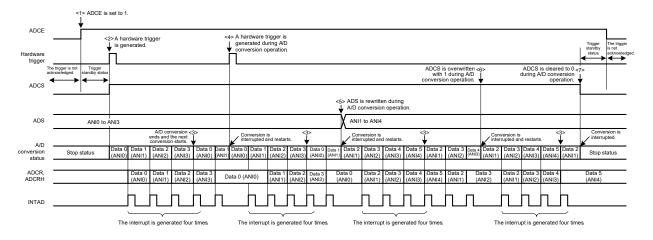

| 10.6.9  | Hardware trigger wait mode (select mode, sequential conversion mode)    | . 298 |

| 10.6.1  | 0 Hardware trigger wait mode (select mode, one-shot conversion mode)    | 299   |

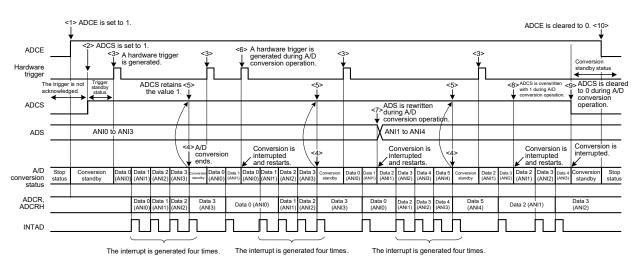

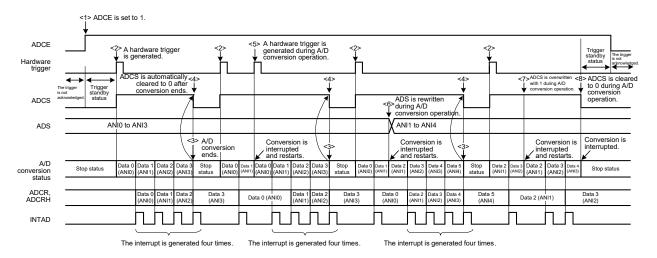

| 10.6.1  | 1 Hardware trigger wait mode (scan mode, sequential conversion mode)    | . 300 |

| 10.6.1  | 2 Hardware trigger wait mode (scan mode, one-shot conversion mode)      | . 301 |

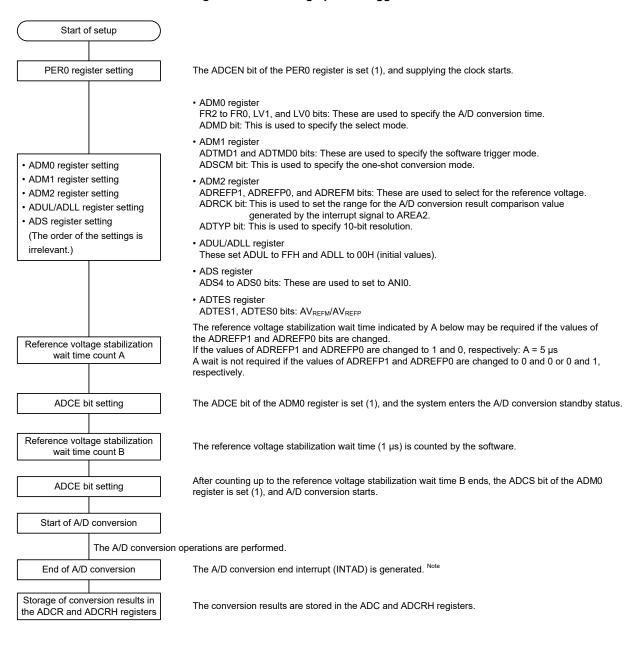

| 10.7    | A/D Converter Setup Flowchart                                           | . 302 |

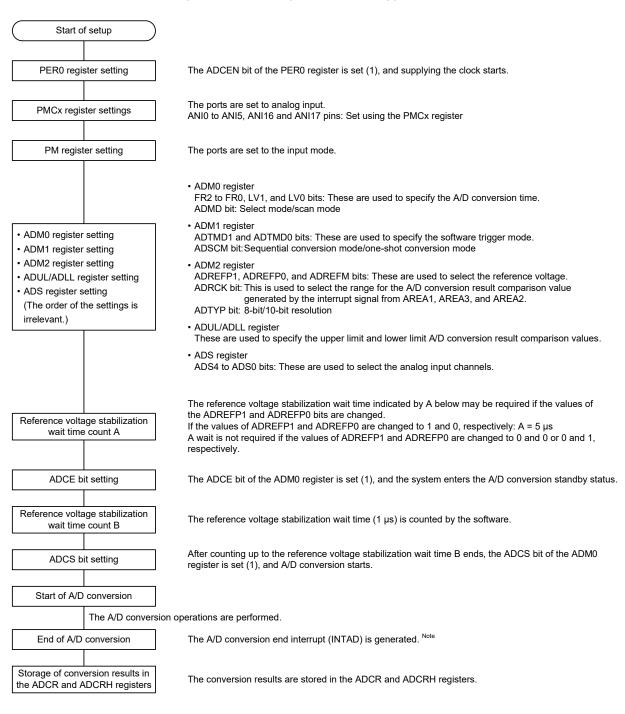

| 10.7.1  | Setting up software trigger mode                                        | . 302 |

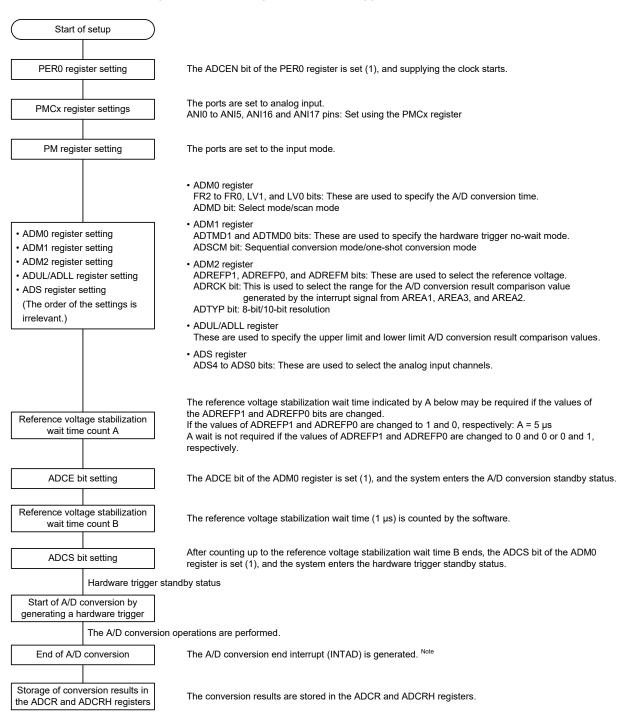

| 10.7.2  | 2 Setting up hardware trigger no-wait mode                              | . 303 |

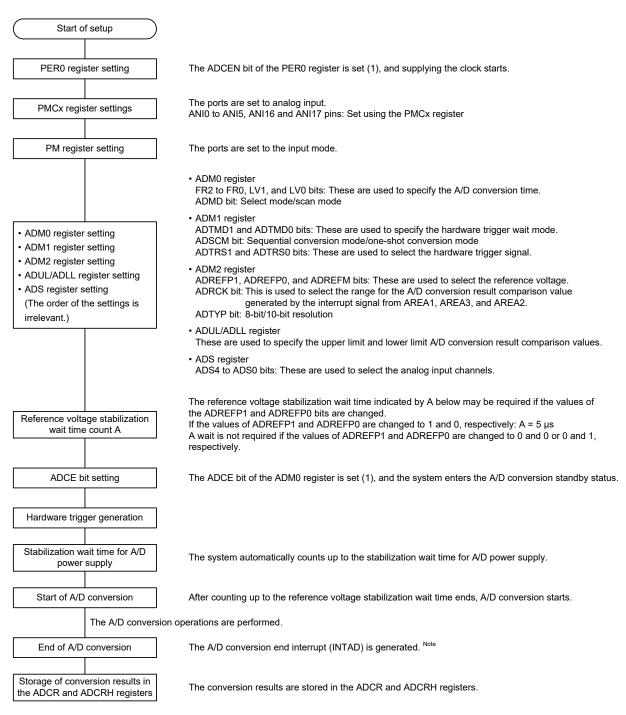

| 10.7.3  | Setting up hardware trigger wait mode                                   | . 304 |

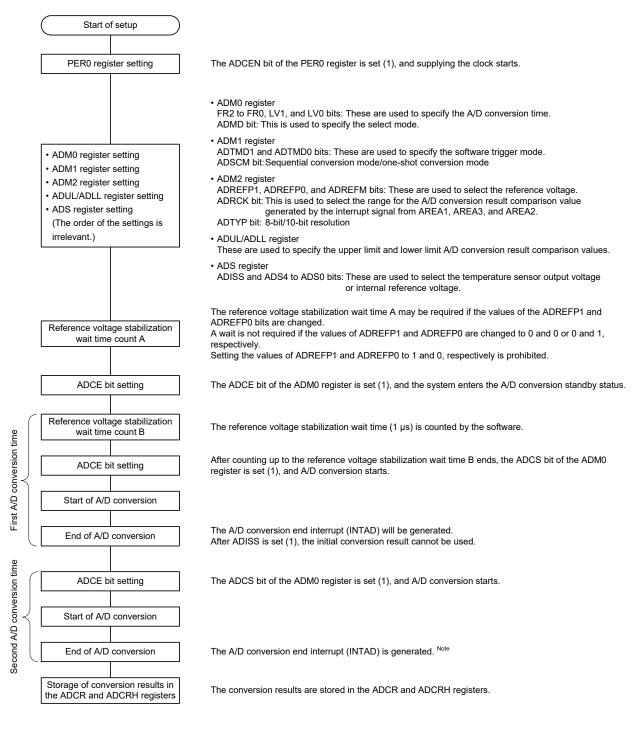

| 10.7.4  | Setup when using temperature sensor                                     |       |

|         | (example for software trigger mode and one-shot conversion mode)        | 305   |

| 10.7.5  | 5 Setting up test mode                                                  | . 306 |

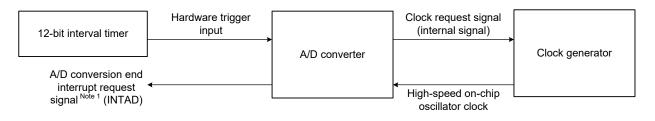

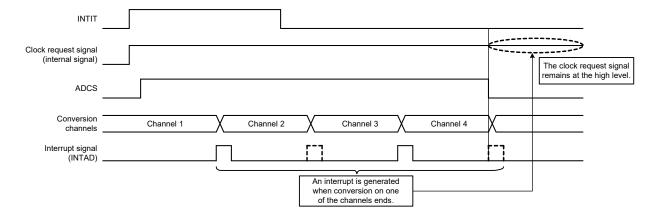

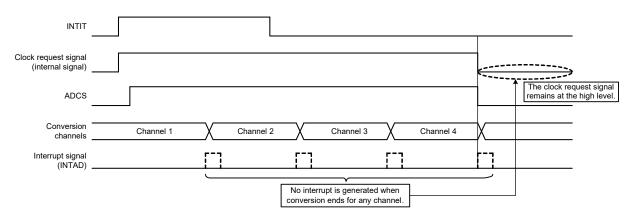

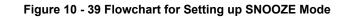

| 10.8    | SNOOZE Mode Function                                                    | . 307 |

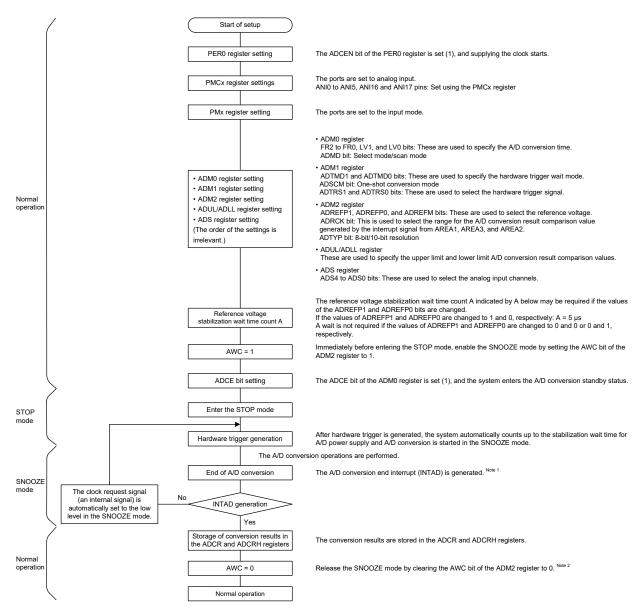

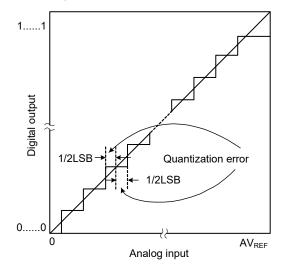

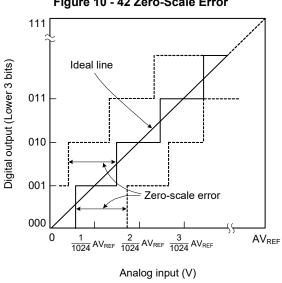

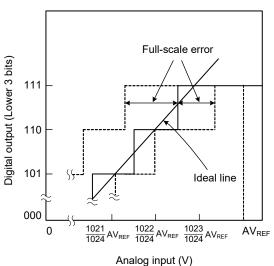

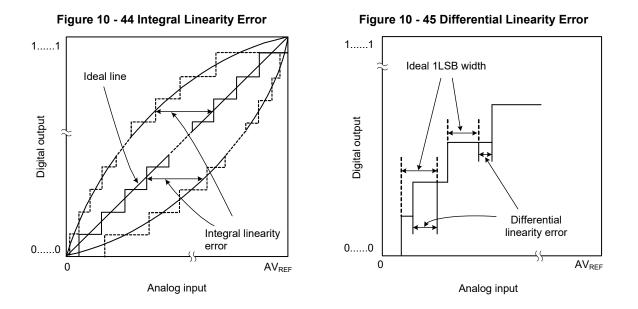

| 10.9    | How to Read A/D Converter Characteristics Table                         | 311   |

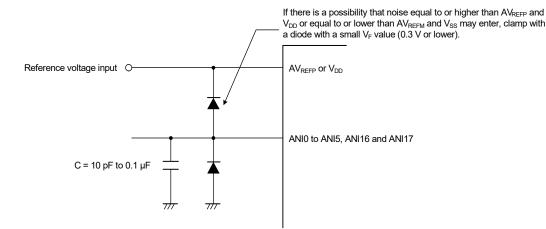

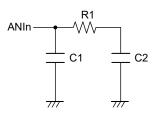

| 10.10   | Cautions for A/D Converter                                              | . 314 |

|         |                                                                         |       |

| 11. SE  | RIAL ARRAY UNIT                                                         |       |

| 11.1    | Functions of Serial Array Unit                                          | . 319 |

|         |                                                                         |       |

| 11.1.1  | 3-wire serial I/O (CSI00, CSI01)                                                      | 319 |

|---------|---------------------------------------------------------------------------------------|-----|

| 11.1.2  | UART (UART0)                                                                          | 320 |

| 11.1.3  | Simplified I <sup>2</sup> C (IIC00, IIC01)                                            | 321 |

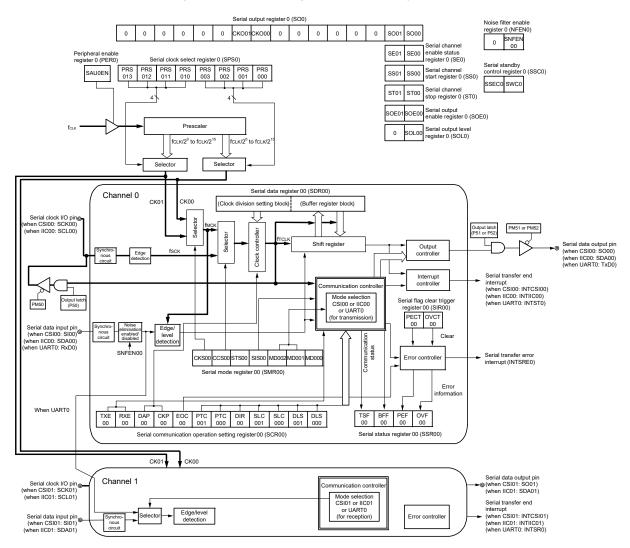

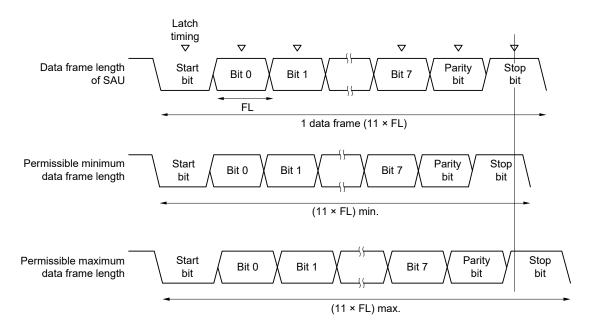

| 11.2 C  | onfiguration of Serial Array Unit                                                     | 322 |

| 11.2.1  | Shift register                                                                        | 325 |

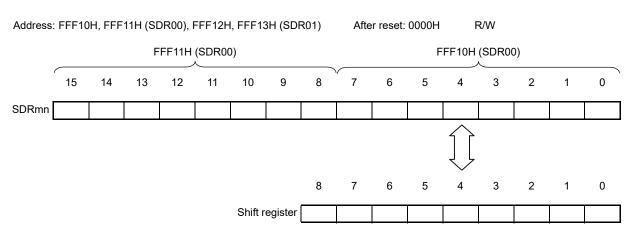

| 11.2.2  | Lower 8/9 bits of the serial data register mn (SDRmn)                                 | 325 |

| 11.3 R  | egisters Controlling Serial Array Unit                                                |     |

| 11.3.1  | Peripheral enable register 0 (PER0)                                                   | 328 |

| 11.3.2  | Peripheral reset control register 0 (PRR0)                                            | 329 |

| 11.3.3  | Serial clock select register m (SPSm)                                                 | 330 |

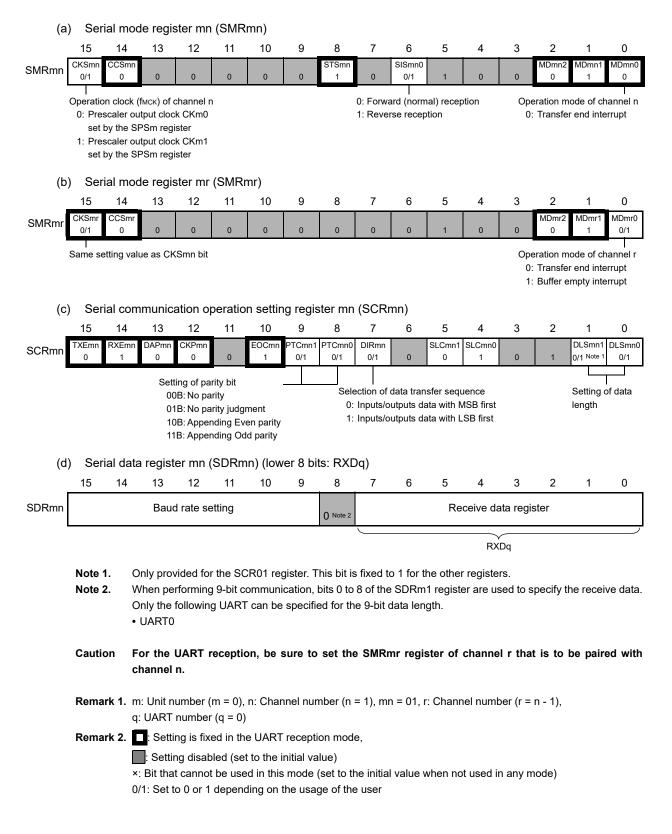

| 11.3.4  | Serial mode register mn (SMRmn)                                                       | 332 |

| 11.3.5  | Serial communication operation setting register mn (SCRmn)                            | 333 |

| 11.3.6  | Serial data register mn (SDRmn)                                                       | 336 |

| 11.3.7  | Serial flag clear trigger register mn (SIRmn)                                         | 337 |

| 11.3.8  | Serial status register mn (SSRmn)                                                     |     |

| 11.3.9  | Serial channel start register m (SSm)                                                 |     |

| 11.3.10 | Serial channel stop register m (STm)                                                  | 341 |

| 11.3.11 | Serial channel enable status register m (SEm)                                         | 342 |

| 11.3.12 | Serial output enable register m (SOEm)                                                | 343 |

| 11.3.13 | Serial output register m (SOm)                                                        | 344 |

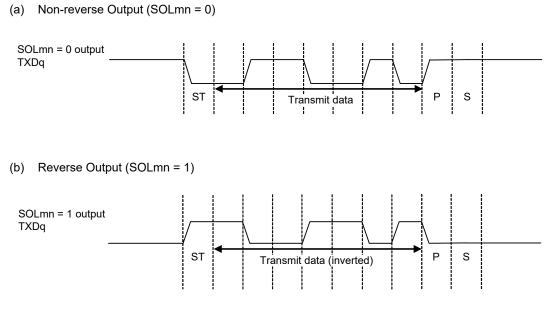

|         | Serial output level register m (SOLm)                                                 |     |

|         | Serial standby control register m (SSCm)                                              |     |

|         | Noise filter enable register 0 (NFEN0)                                                |     |

|         | Registers controlling port functions of serial input/output pins                      |     |

|         | peration Stop Mode                                                                    |     |

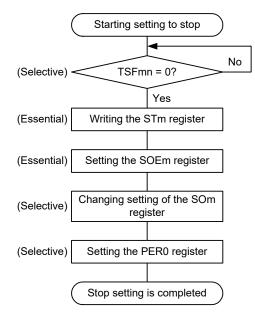

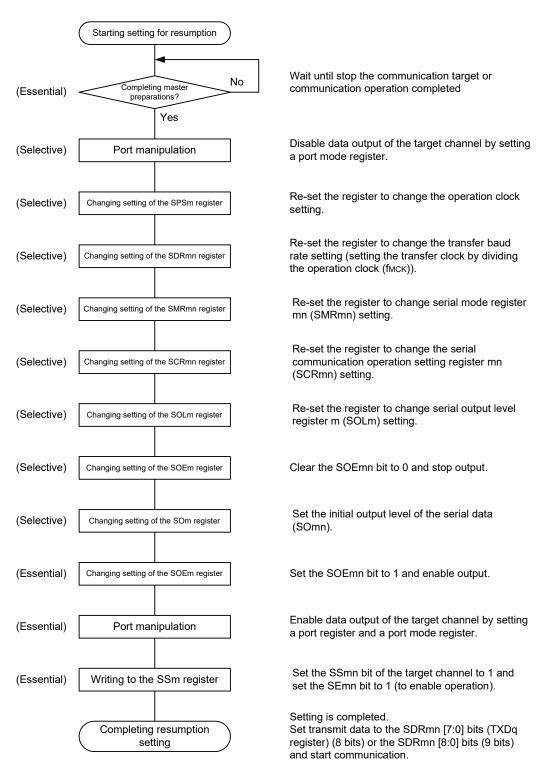

| 11.4.1  | Stopping the operation by units                                                       | 351 |

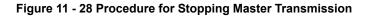

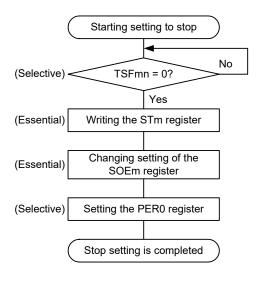

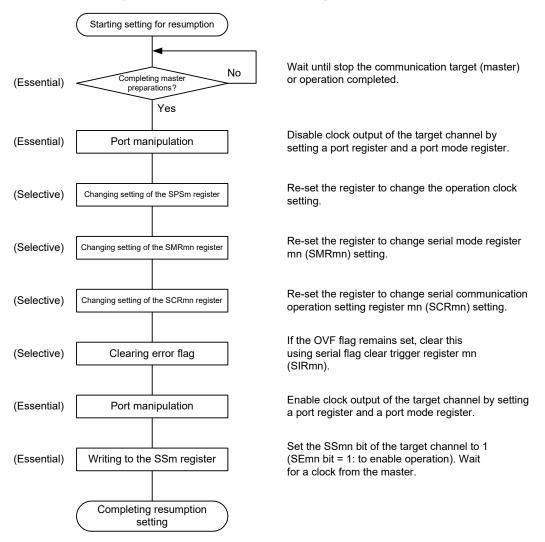

| 11.4.2  | Stopping the operation by channels                                                    | 352 |

| 11.5 C  | peration of 3-Wire Serial I/O (CSI00, CSI01) Communication                            |     |

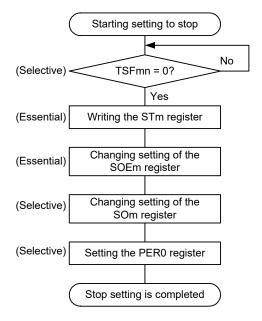

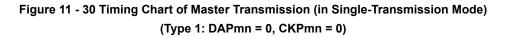

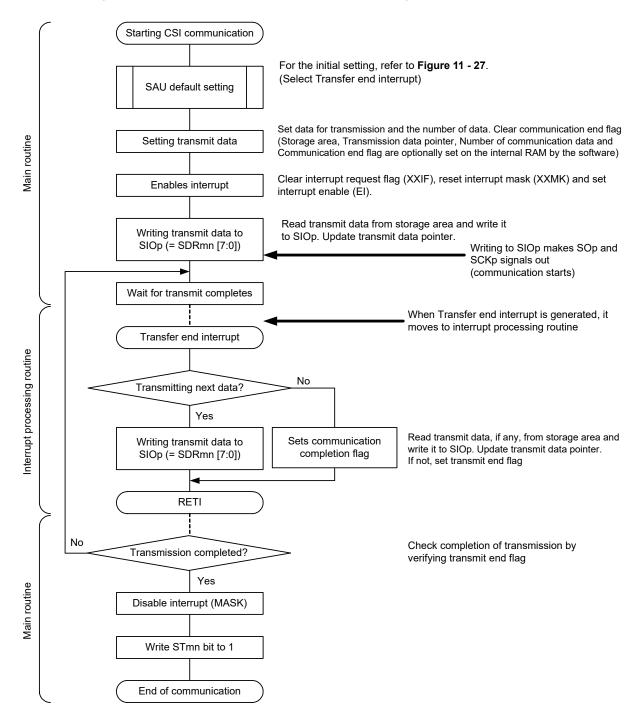

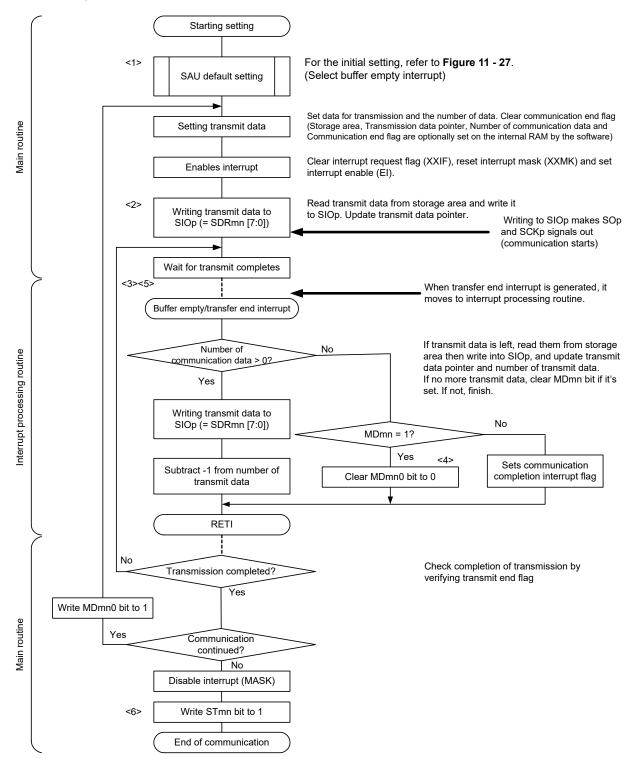

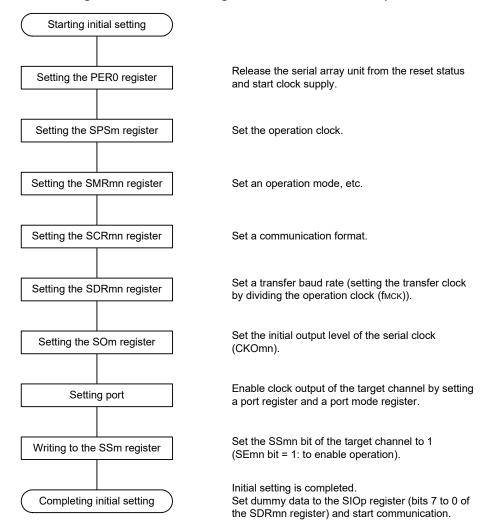

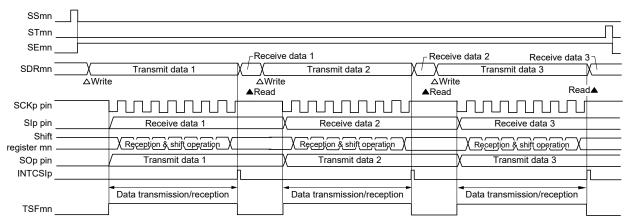

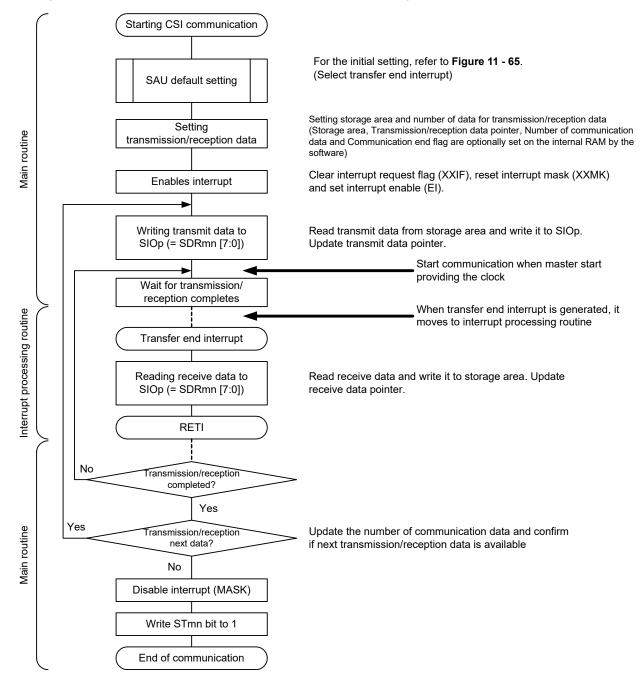

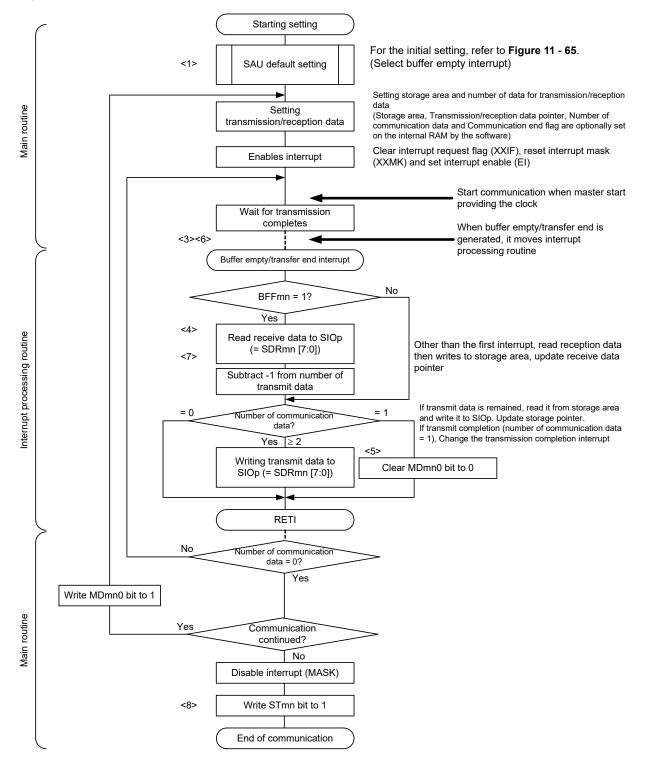

| 11.5.1  | Master transmission                                                                   |     |

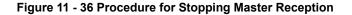

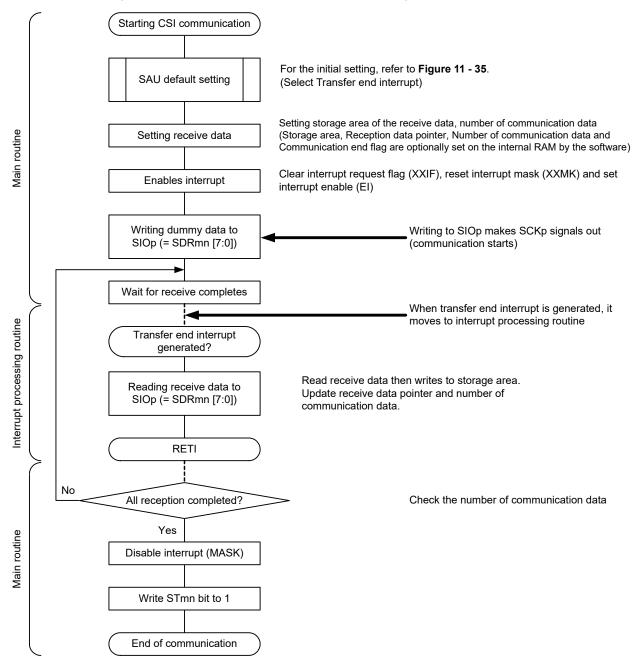

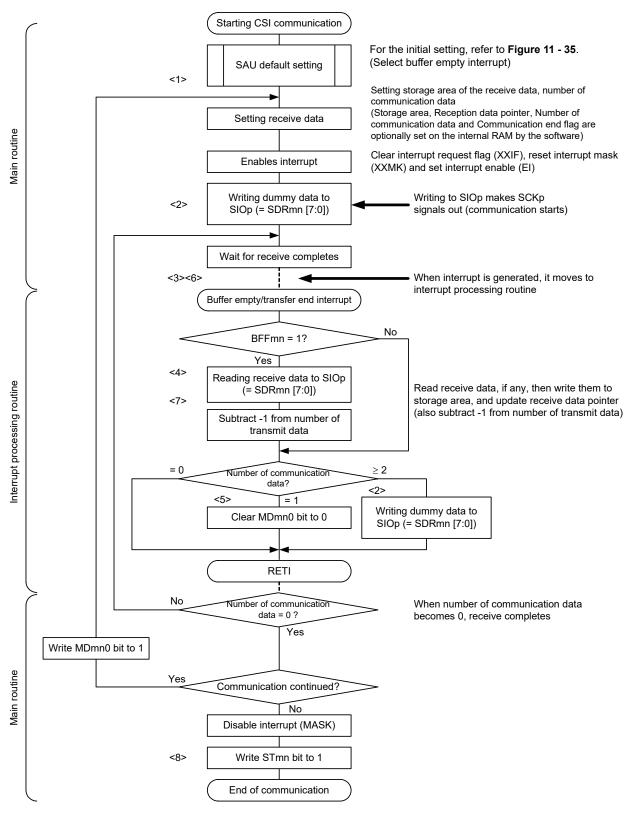

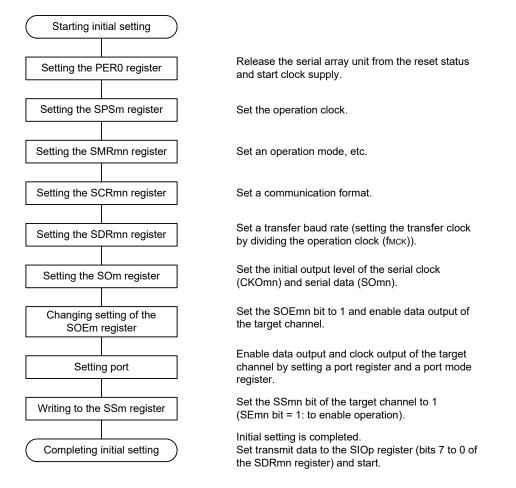

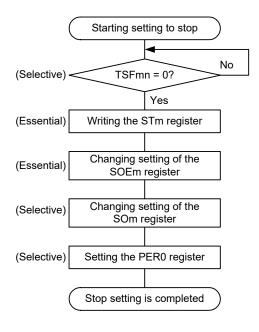

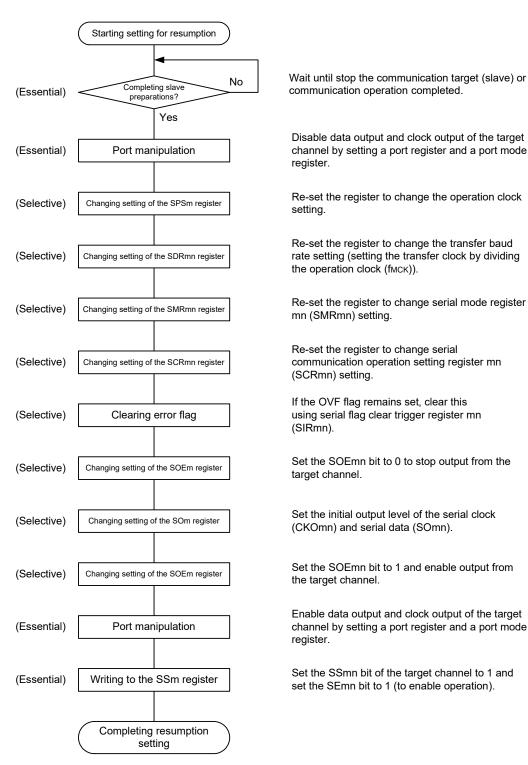

| 11.5.2  | Master reception                                                                      | 363 |

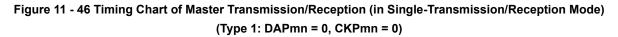

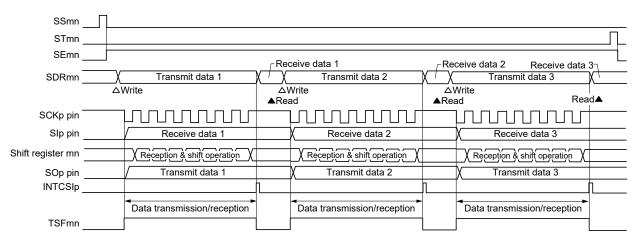

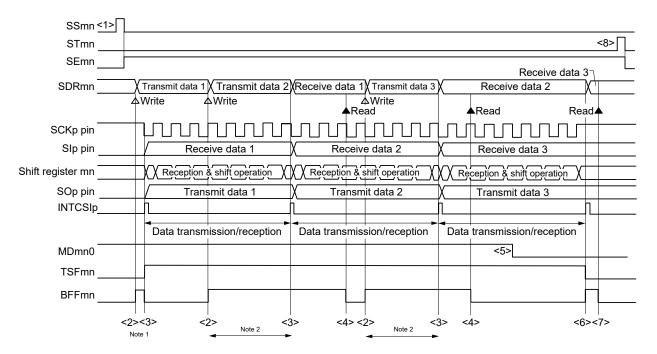

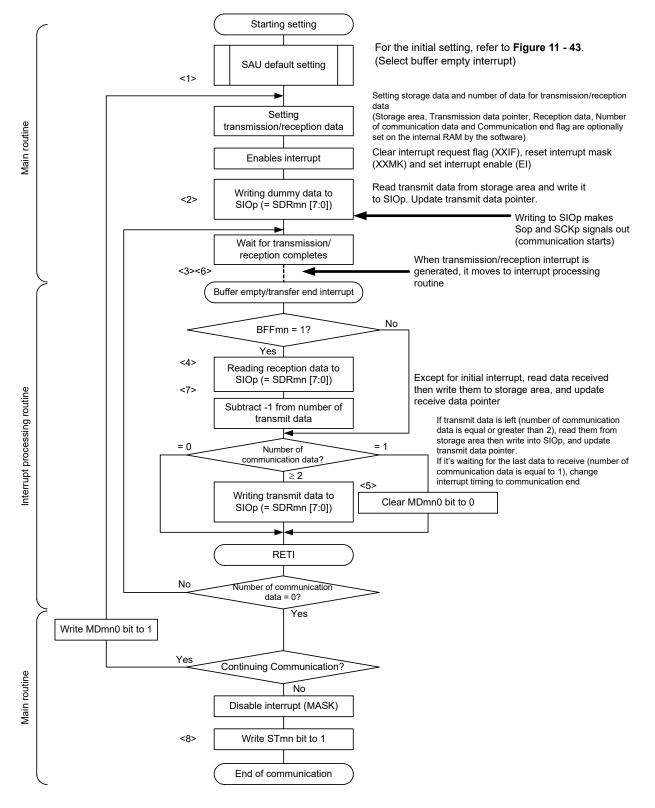

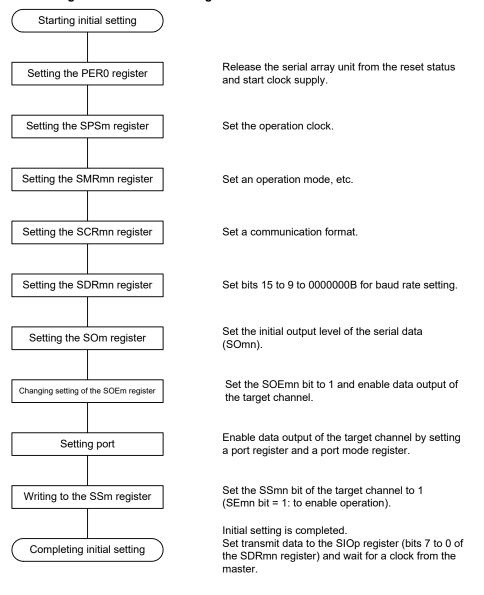

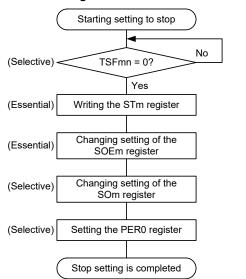

| 11.5.3  | Master transmission/reception                                                         | 371 |

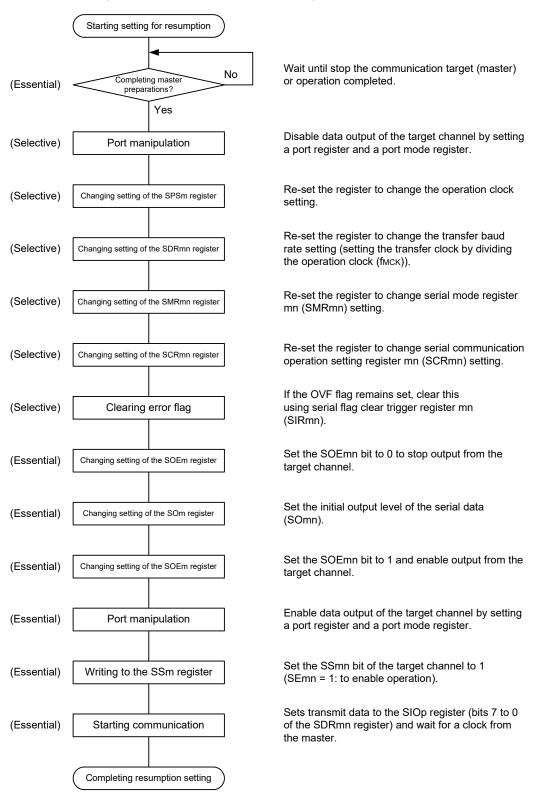

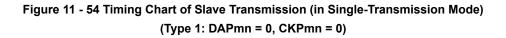

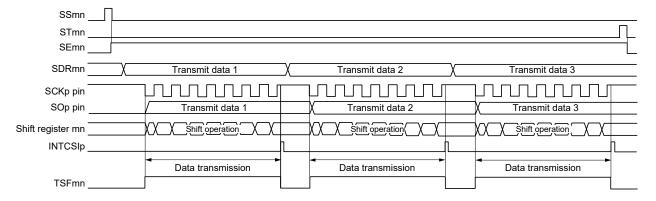

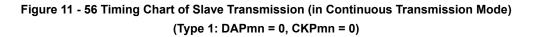

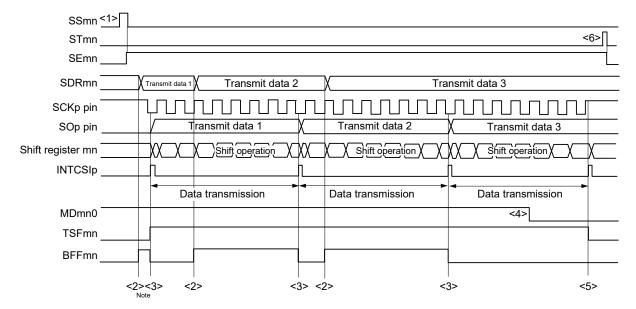

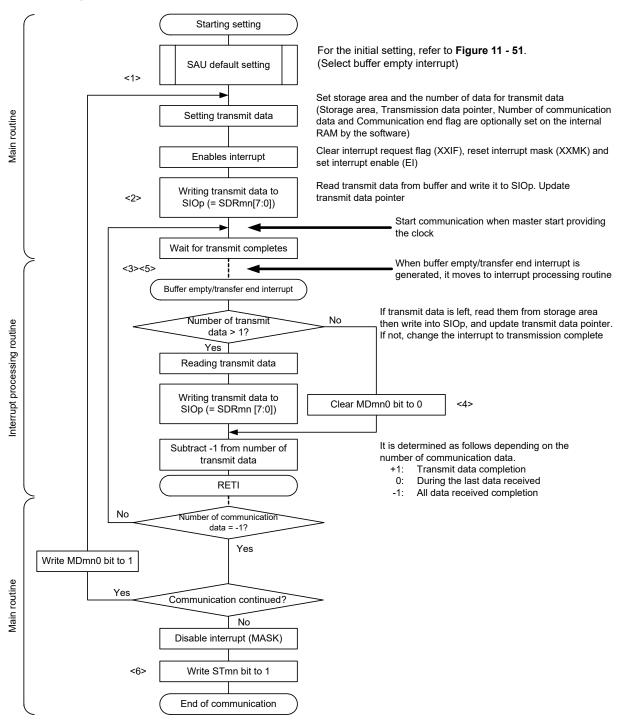

| 11.5.4  | Slave transmission                                                                    | 379 |

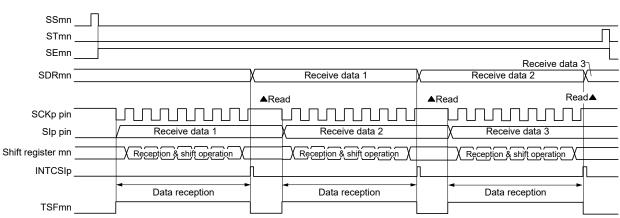

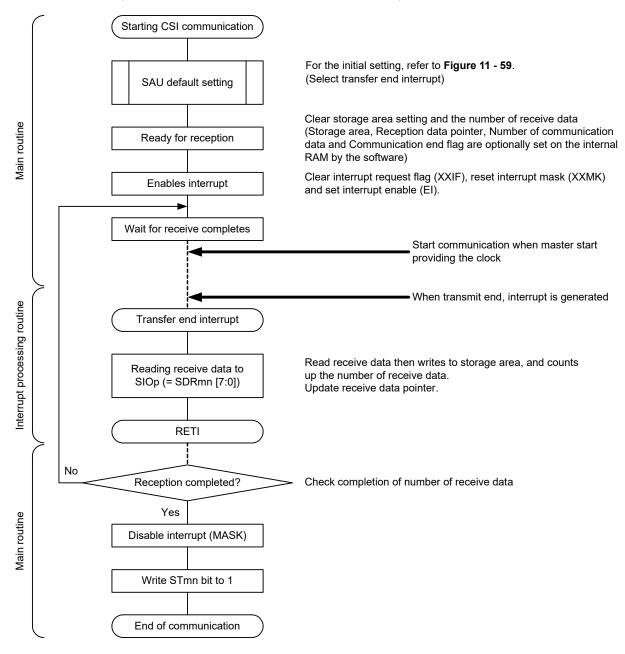

| 11.5.5  | Slave reception                                                                       | 387 |

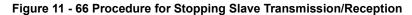

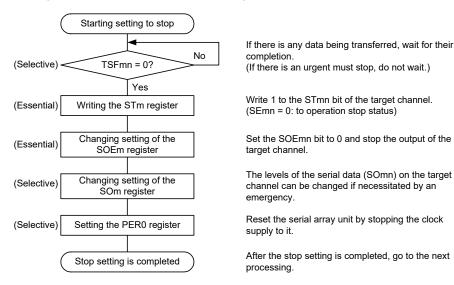

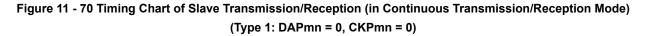

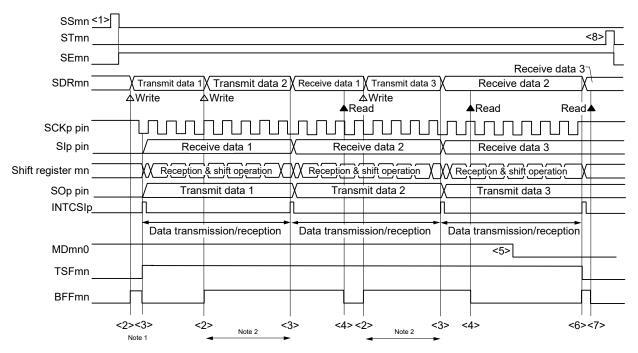

| 11.5.6  | Slave transmission/reception                                                          | 393 |

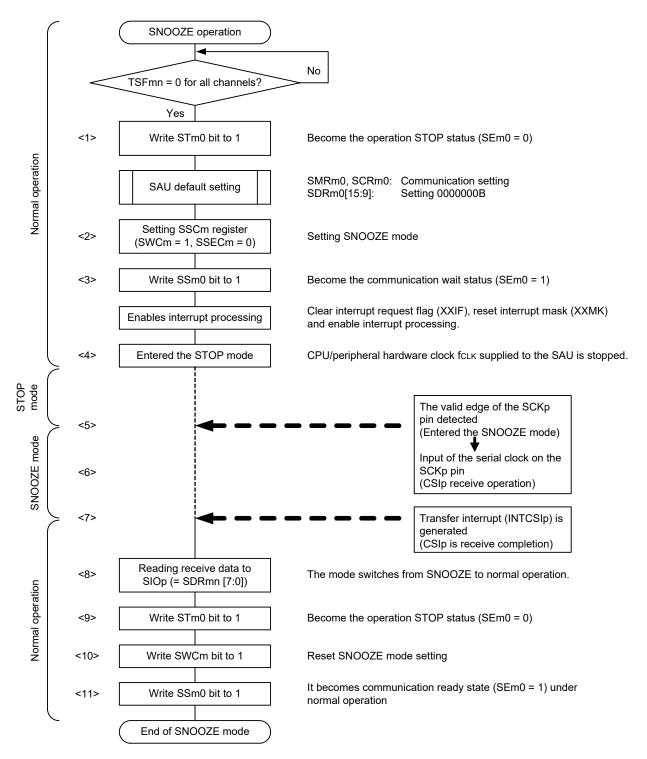

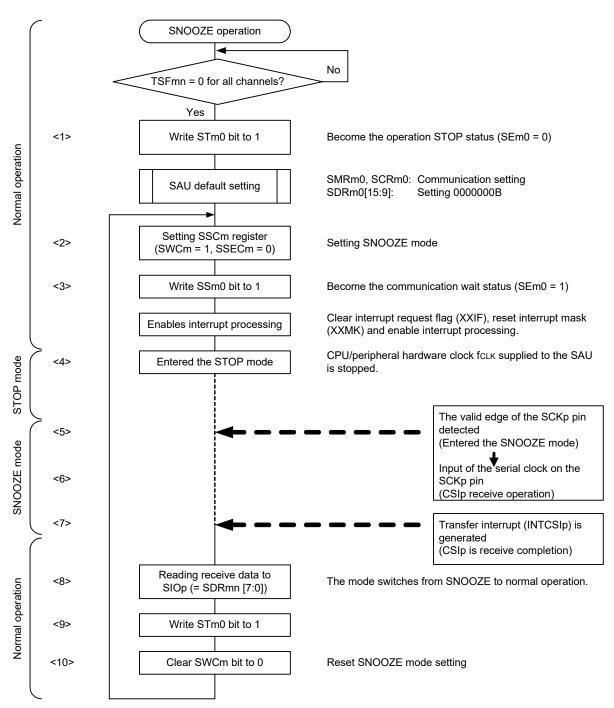

| 11.5.7  | SNOOZE mode function                                                                  | 401 |

| 11.5.8  | Calculating transfer clock frequency                                                  | 405 |

| 11.5.9  | Procedure for processing errors that occurred during 3-wire serial I/O (CSI00, CSI01) |     |

|         | communication                                                                         |     |

| 11.6 C  | peration of UART (UART0) Communication                                                |     |

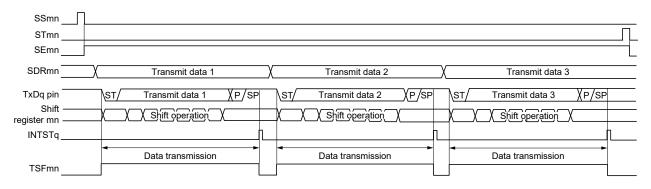

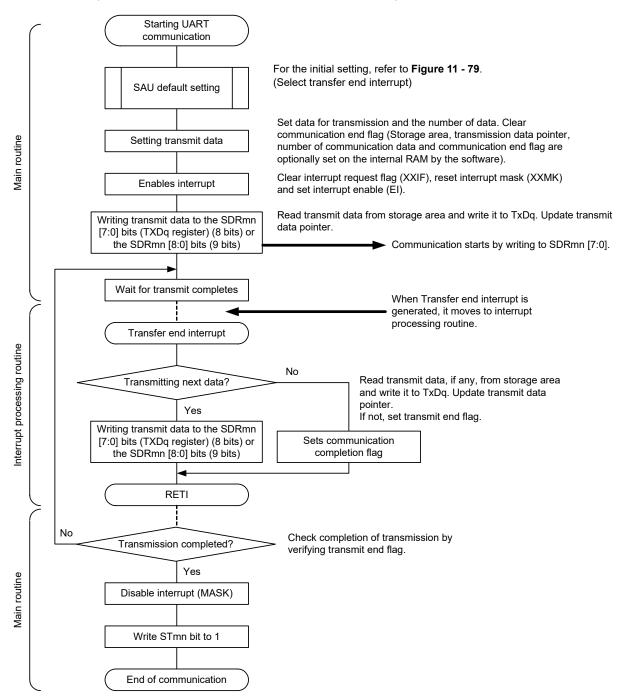

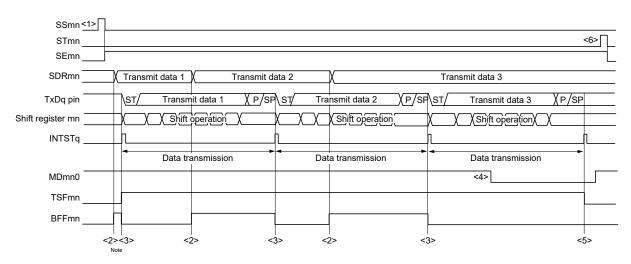

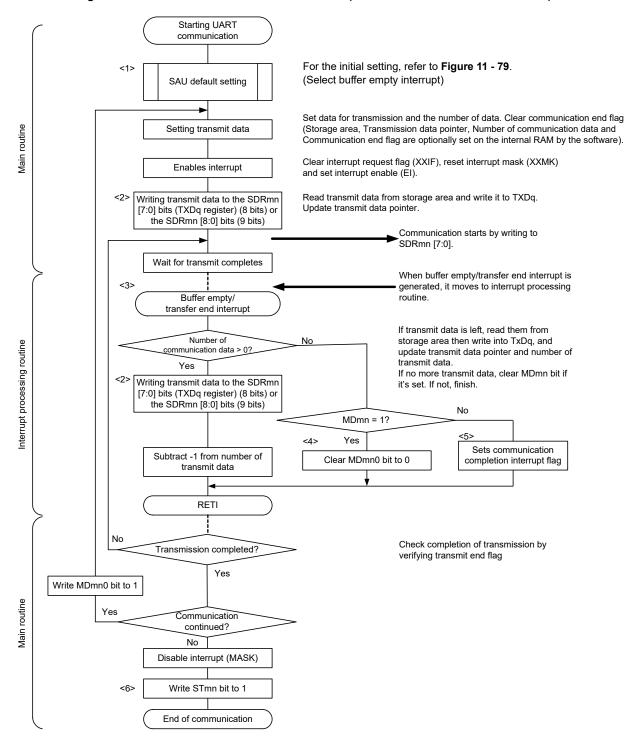

| 11.6.1  | UART transmission                                                                     | 410 |

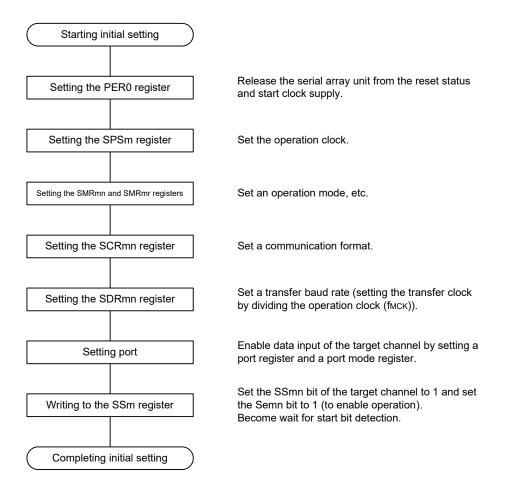

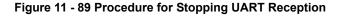

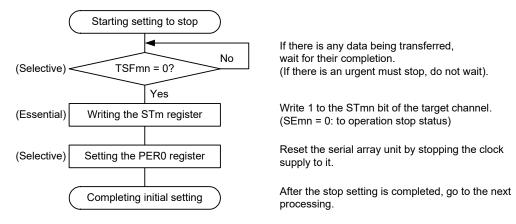

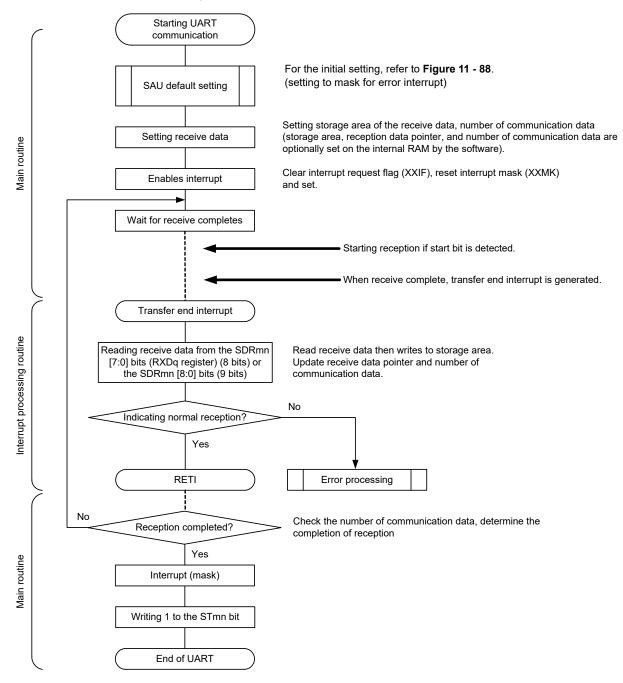

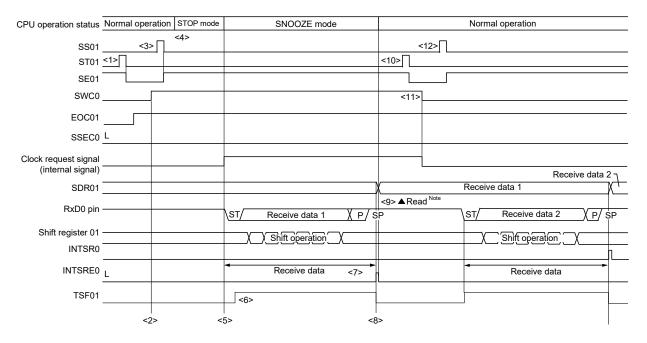

| 11.6.2  | UART reception                                                                        | 419 |

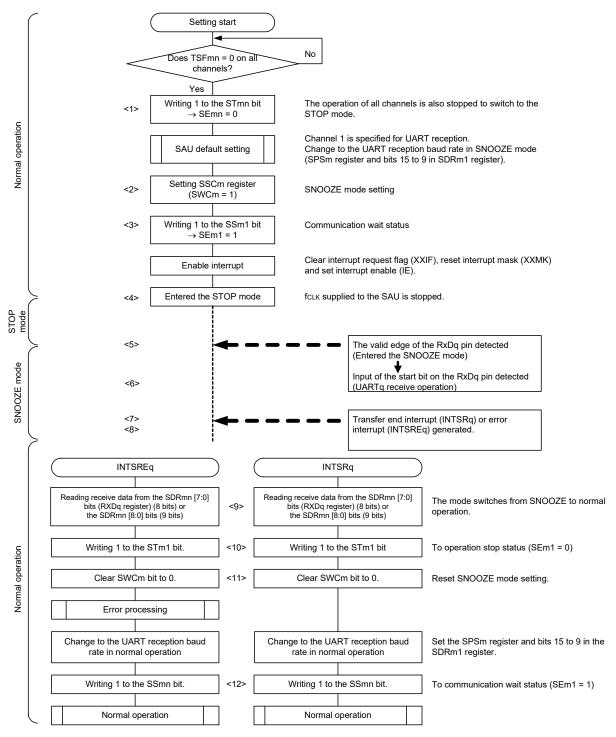

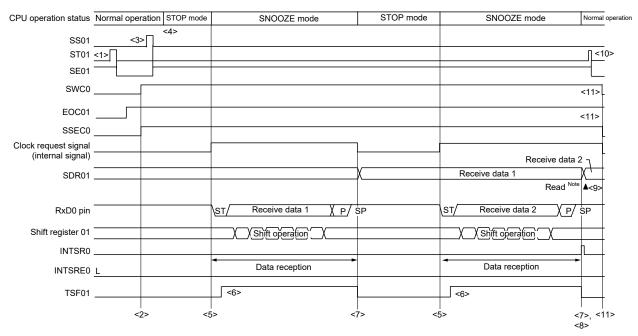

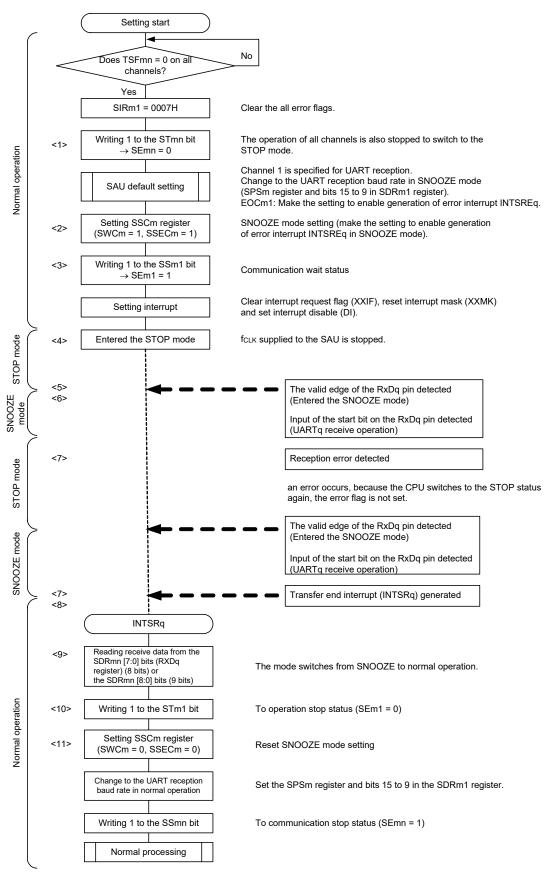

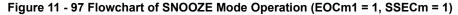

| 11.6.3  | SNOOZE mode function                                                                  | 426 |

| 11.6.4  | Calculating baud rate                                                                 |     |

| 11.6.5  | Procedure for processing errors that occurred during UART (UART0) communication       |     |

|         | peration of Simplified I <sup>2</sup> C (IIC00, IIC01) Communication                  |     |

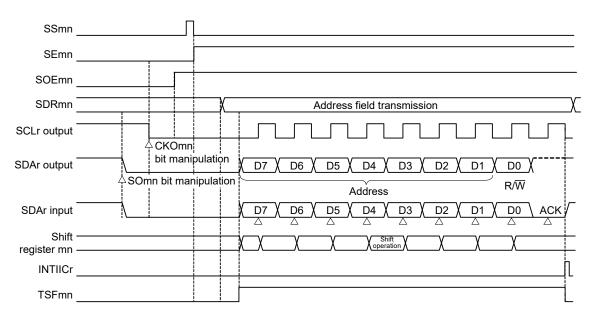

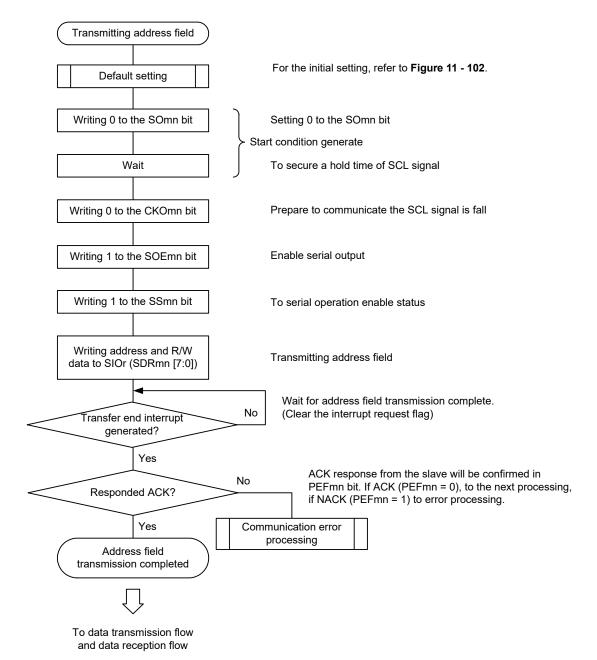

| 11.7.1  | Address field transmission                                                            | 441 |

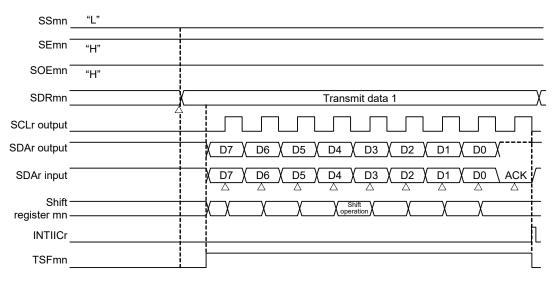

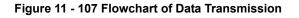

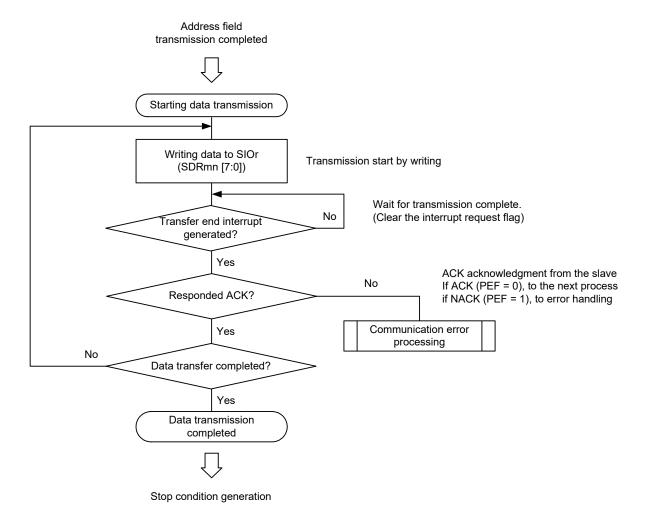

| 11.7.2  | Data transmission                                                                     |     |

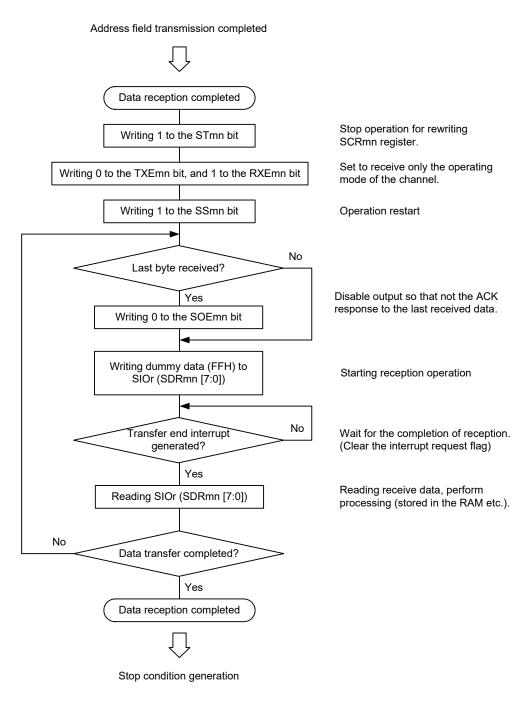

| 11.7.3  | Data reception                                                                        |     |

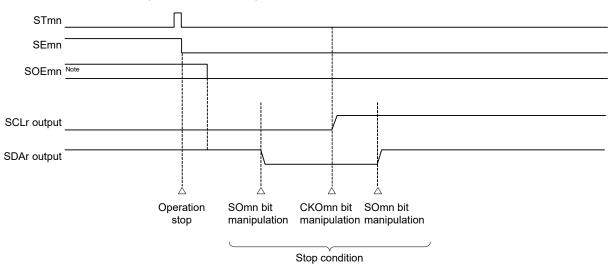

| 11.7.4  | Stop condition generation                                                             | 453 |

| 11.7.5  | 8                                                                                                             | 454   |

|---------|---------------------------------------------------------------------------------------------------------------|-------|

| 11.7.6  | Procedure for processing errors that occurred during simplified I <sup>2</sup> C (IIC00, IIC01) communication | . 456 |

| 12. SEI | RIAL INTERFACE IICA                                                                                           | 457   |

| 12.1    | Functions of Serial Interface IICA                                                                            |       |

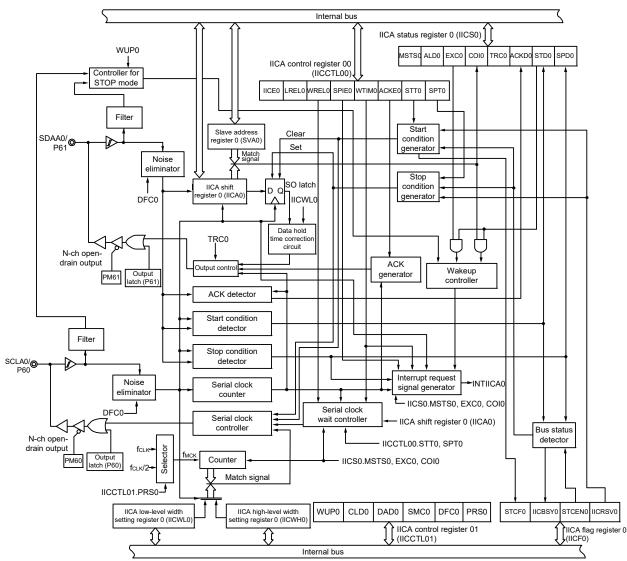

| 12.2    | Configuration of Serial Interface IICA                                                                        |       |

| 12.3    | Registers Controlling Serial Interface IICA                                                                   |       |

| 12.3.1  |                                                                                                               |       |

| 12.3.2  |                                                                                                               |       |

| 12.3.3  | IICA status register n (IICSn)                                                                                | 469   |

| 12.3.4  | IICA flag register n (IICFn)                                                                                  | 471   |

| 12.3.5  | IICA control register n1 (IICCTLn1)                                                                           | 473   |

| 12.3.6  | IICA low-level width setting register n (IICWLn)                                                              | 475   |

| 12.3.7  | IICA high-level width setting register n (IICWHn)                                                             | 475   |

| 12.3.8  | Port mode registers 6, 7 (PM6, PM7)                                                                           | 476   |

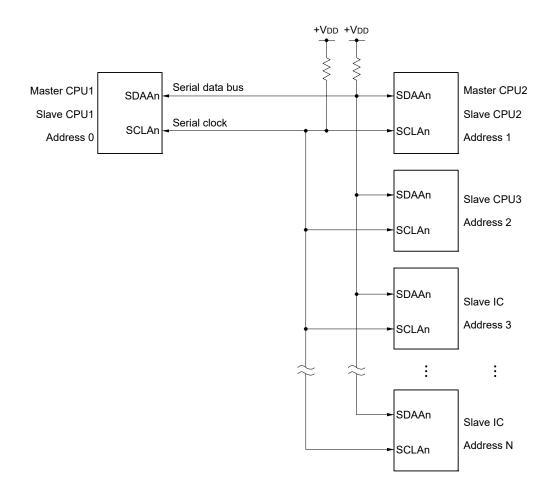

| 12.4    | I <sup>2</sup> C Bus Mode Functions                                                                           | 477   |

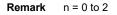

| 12.4.1  | Pin configuration                                                                                             | 477   |

| 12.4.2  | Setting transfer clock by using IICWLn and IICWHn registers                                                   | 478   |

| 12.5    | I <sup>2</sup> C Bus Definitions and Control Methods                                                          | 480   |

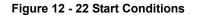

| 12.5.1  | Start conditions                                                                                              | 480   |

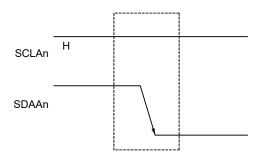

| 12.5.2  | Addresses                                                                                                     | 481   |

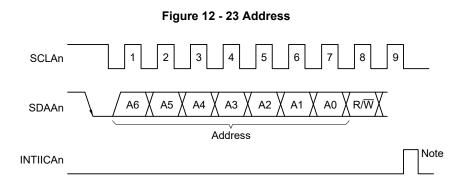

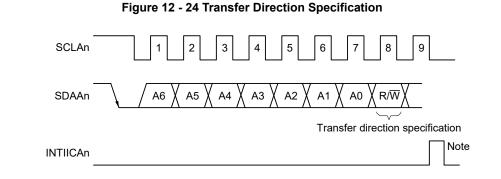

| 12.5.3  | Transfer direction specification                                                                              | 481   |

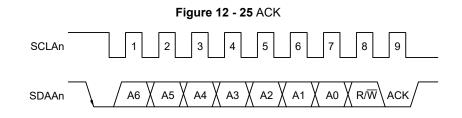

| 12.5.4  | Acknowledge (ACK)                                                                                             | 482   |

| 12.5.5  | Stop condition                                                                                                | 483   |

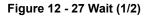

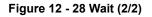

| 12.5.6  | Wait                                                                                                          | 484   |

| 12.5.7  | Canceling wait                                                                                                | 486   |

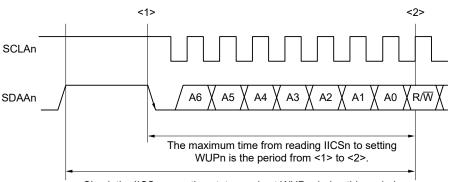

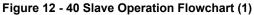

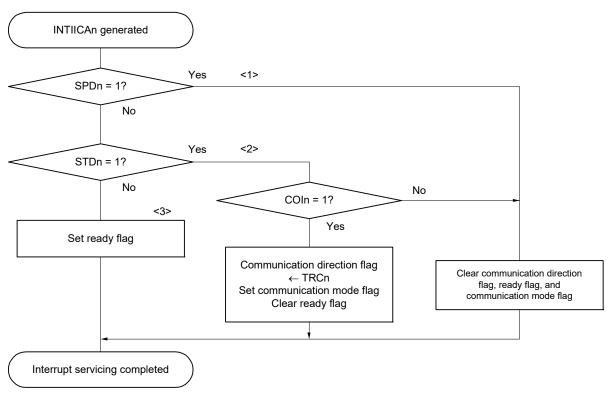

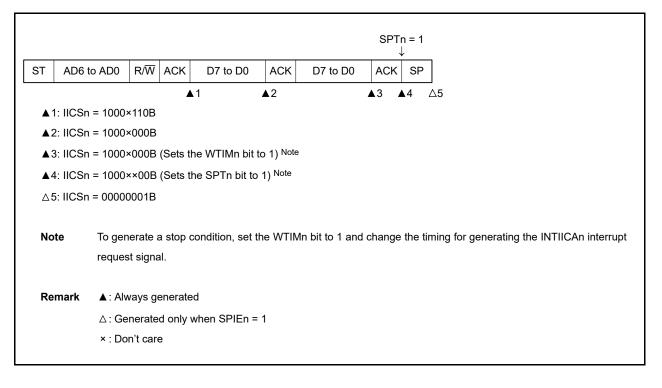

| 12.5.8  | Interrupt request (INTIICAn) generation timing and wait control                                               | 487   |

| 12.5.9  |                                                                                                               |       |

| 12.5.1  | 0 Error detection                                                                                             | 488   |

| 12.5.1  | 1 Extension code                                                                                              | 489   |

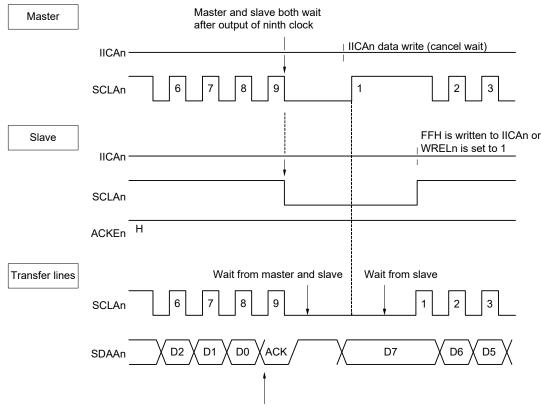

| 12.5.1  | 2 Arbitration                                                                                                 | 490   |

| 12.5.1  | 3 Wakeup function                                                                                             | 492   |

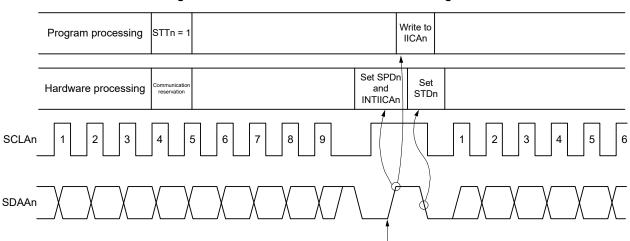

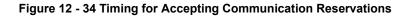

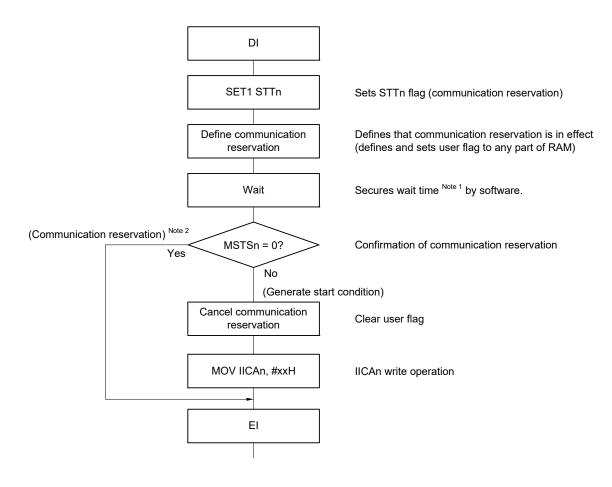

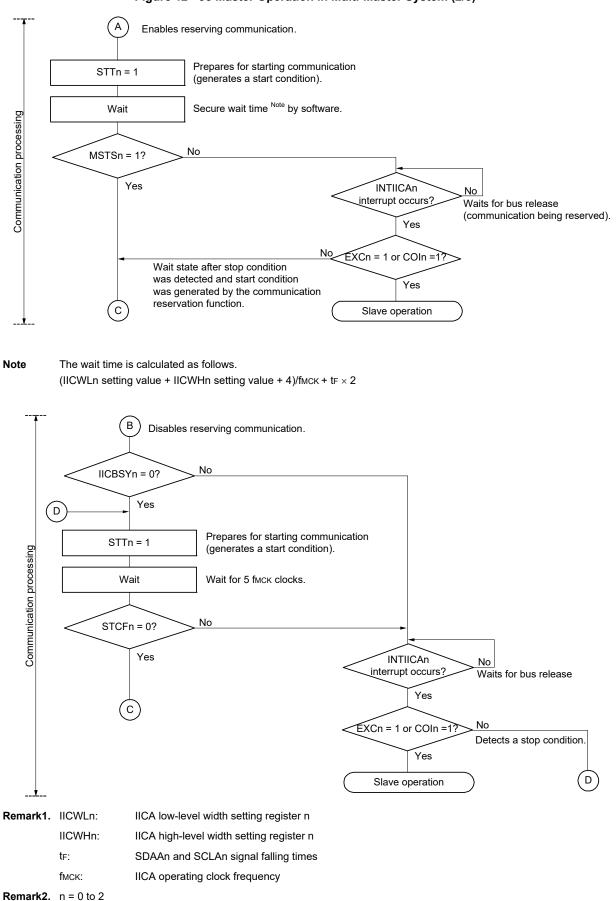

| 12.5.1  | 4 Communication reservation                                                                                   | 495   |

| 12.5.1  | 5 Cautions                                                                                                    | 499   |

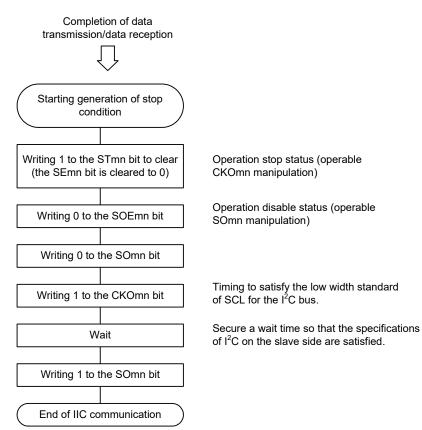

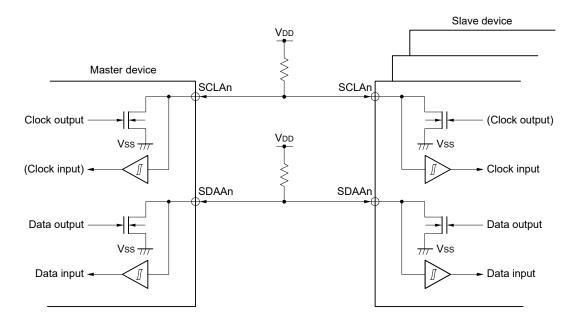

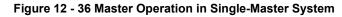

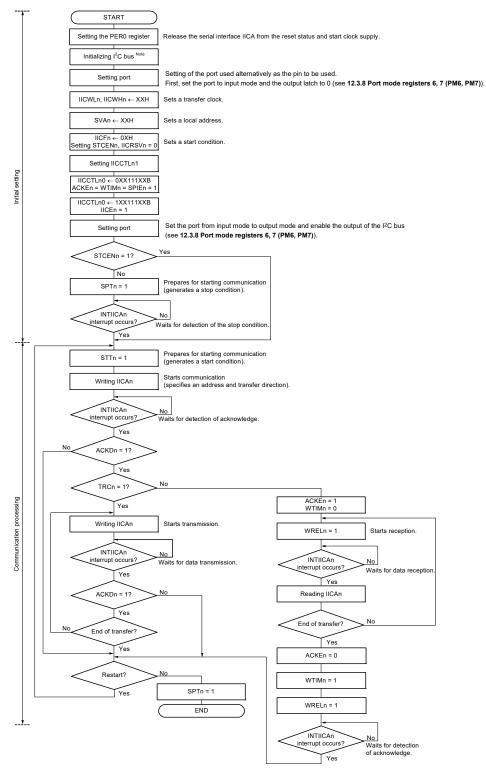

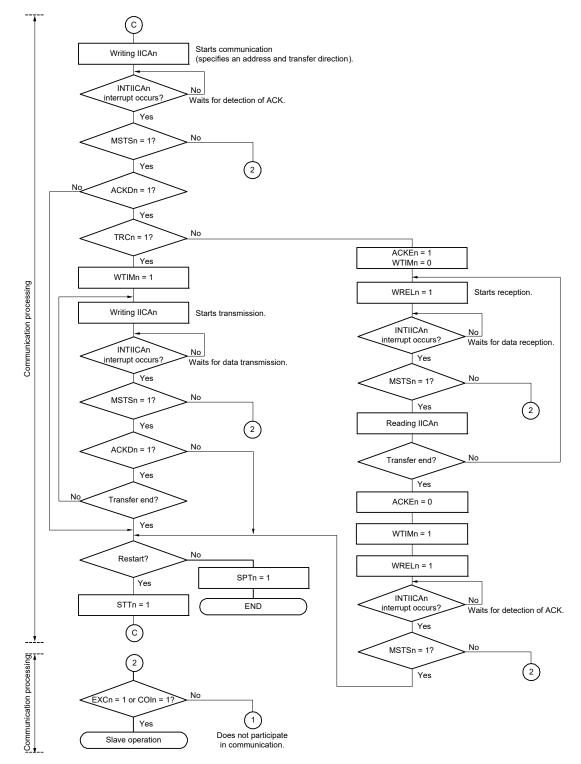

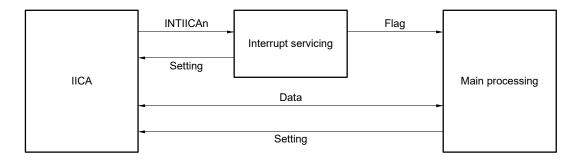

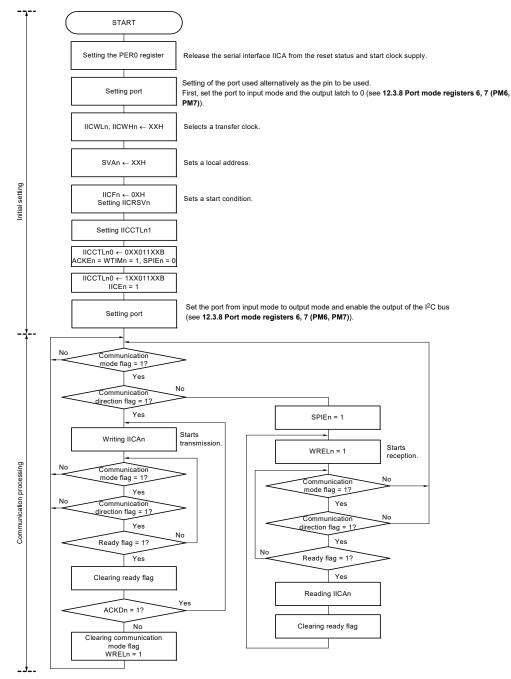

| 12.5.1  | 6 Communication operations                                                                                    | 500   |

| 12.5.1  | 7 Timing of I <sup>2</sup> C interrupt request (INTIICAn) occurrence                                          | 508   |

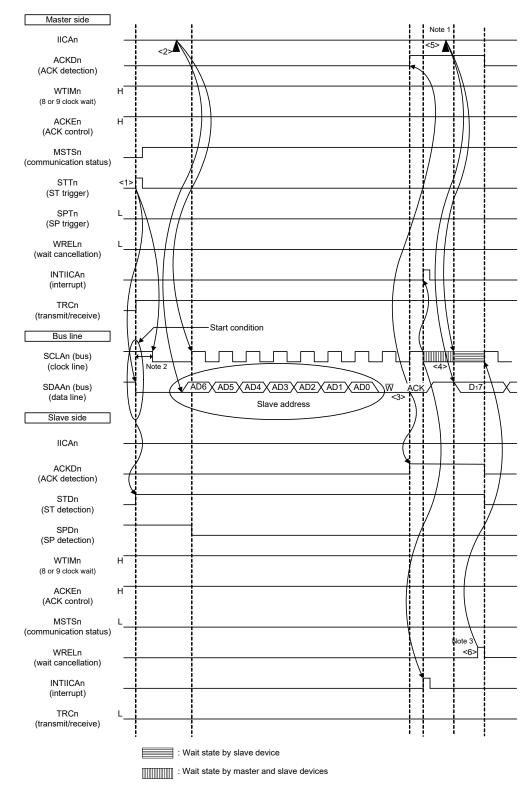

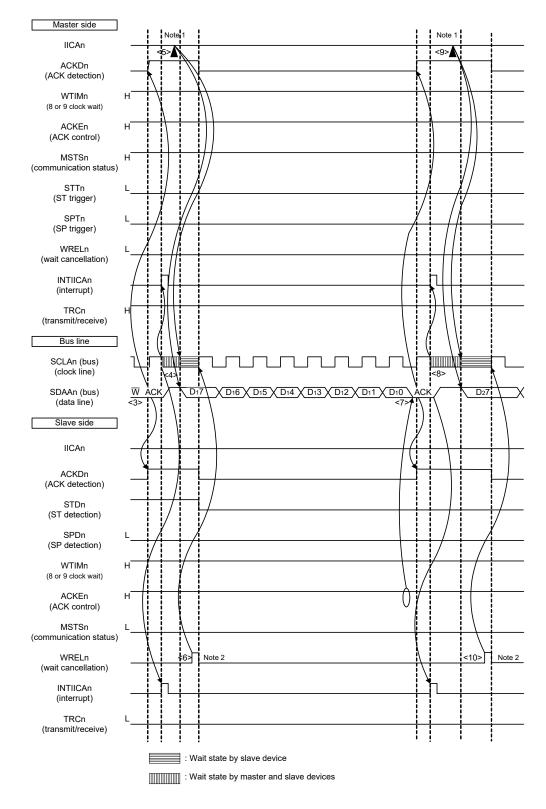

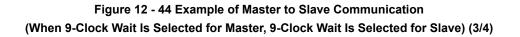

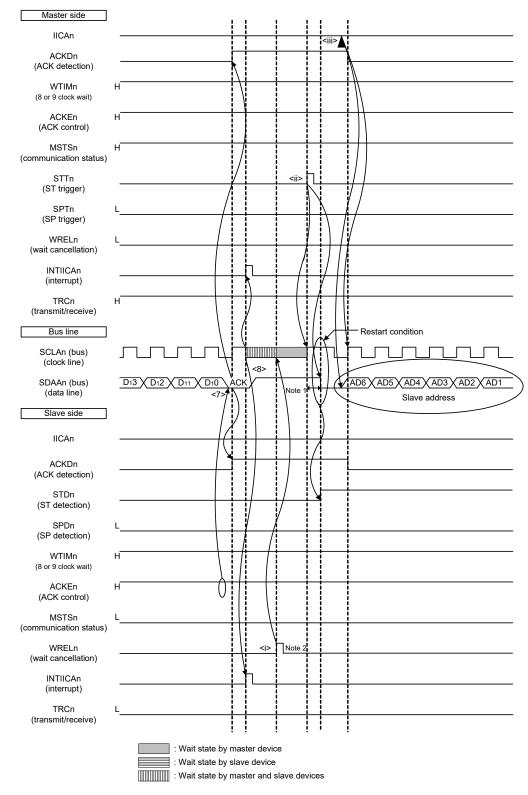

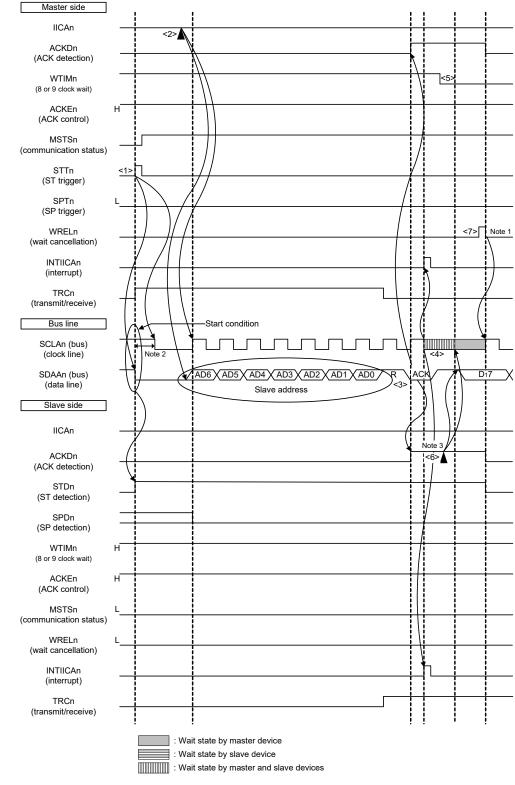

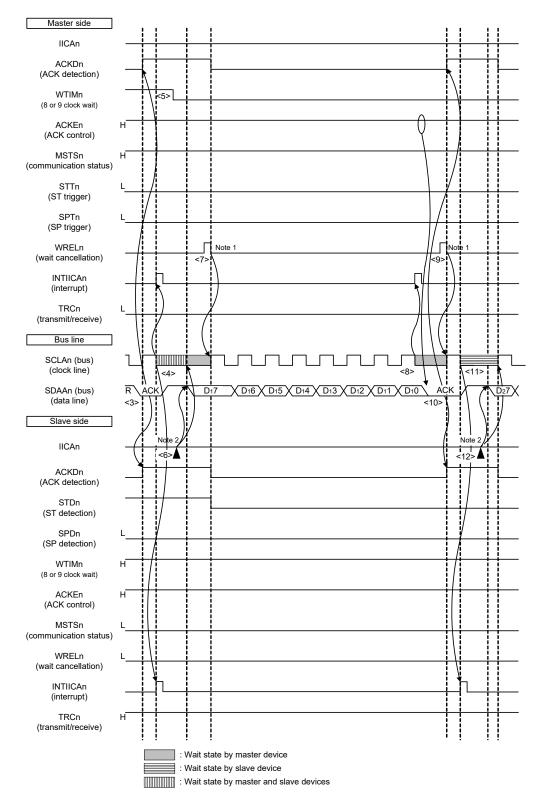

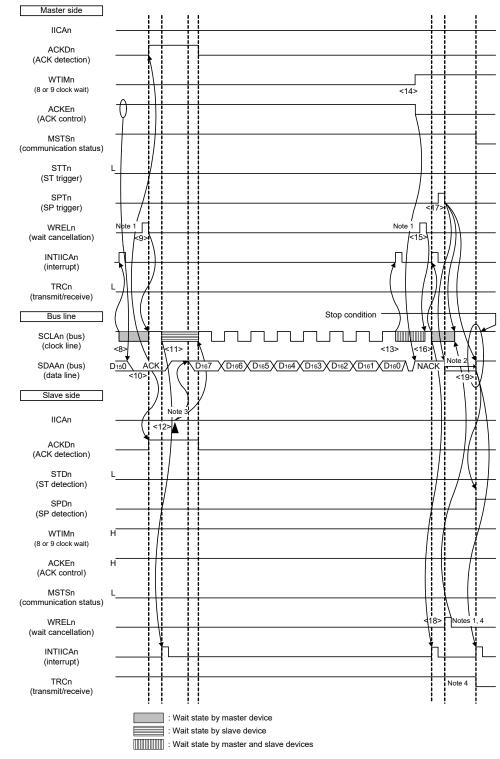

| 12.6    | Timing Charts                                                                                                 | 529   |

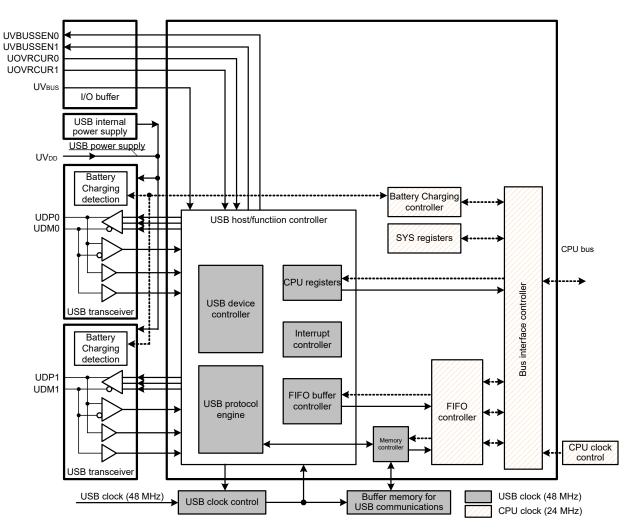

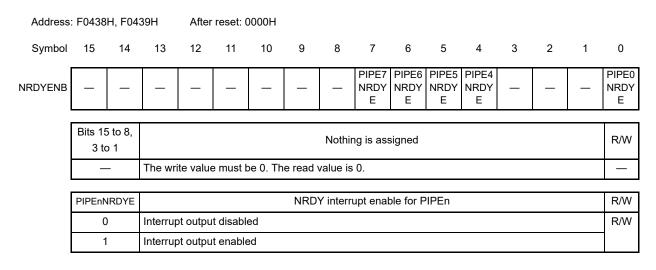

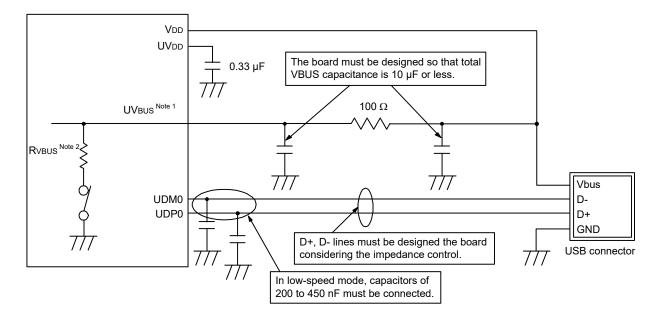

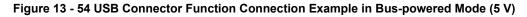

| 13. US  | B 2.0 HOST/FUNCTION MODULE (USB)                                                                              | 544   |

| 13.1    | Functions of USB 2.0 Host/Function Module                                                                     | 544   |

| 13.2    | Configuration of USB 2.0 Host/Function Module                                                                 |       |

| 13.3    | Registers Used in USB 2.0 Host/Function Module                                                                |       |

| 13.3.1  | •                                                                                                             |       |

|         | system configuration control register 1 (SYSCFG1)                                                             | . 551 |

| 13.3.2  | System configuration status register n (SYSSTSn) (n = 0, 1)                                                   | 554   |

| 13.3.3  | Device state control register n (DVSTCTRn) (n = 0, 1)                                                         | 555   |

| 13.3.4  | CFIFO port register (CFIFOM), DnFIFO port register (DnFIFOM) (n = 0, 1)                                       | 560   |

| 13.3.5  | CFIFO port select register (CFIFOSEL), DnFIFO port select register (DnFIFOSEL) (n = 0, 1)      | 562 |

|---------|------------------------------------------------------------------------------------------------|-----|

| 13.3.6  | CFIFO port control register (CFIFOCTR), DnFIFO port control register (DnFIFOCTR)<br>(n = 0, 1) |     |

| 13.3.7  | Interrupt enable register 0 (INTENB0)                                                          |     |

| 13.3.8  | Interrupt enable register n (INTENBn) (n = 1, 2)                                               |     |

| 13.3.9  | BRDY interrupt enable register (BRDYENB)                                                       |     |

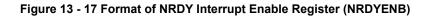

|         | NRDY interrupt enable register (NRDYENB)                                                       |     |

|         | BEMP interrupt enable register (BEMPENB)                                                       |     |

|         | SOF output configuration register (SOFCFG)                                                     |     |

|         | Interrupt status register 0 (INTSTS0)                                                          |     |

|         | Interrupt status register 0 (INTSTS0) (n = 1, 2)                                               |     |

|         | BRDY interrupt status register (BRDYSTS)                                                       |     |

|         | NRDY interrupt status register (NRDYSTS)                                                       |     |

|         | BEMP interrupt status register (BEMPSTS)                                                       |     |

|         |                                                                                                |     |

|         | Frame number register (FRMNUM)                                                                 |     |

|         | USB address register (USBADDR)                                                                 |     |

|         | USB request type register (USBREQ)                                                             |     |

|         | USB request value register (USBVAL)                                                            |     |

|         | USB request index register (USBINDX)                                                           |     |

|         | USB request length register (USBLENG)                                                          |     |

|         | DCP configuration register (DCPCFG)                                                            |     |

|         | DCP maximum packet size register (DCPMAXP)                                                     |     |

|         | DCP control register (DCPCTR)                                                                  |     |

|         | Pipe window select register (PIPESEL)                                                          |     |

|         | Pipe configuration register (PIPECFG)                                                          |     |

|         | Pipe maximum packet size register (PIPEMAXP)                                                   |     |

|         | Pipe cycle control register (PIPEPERI)                                                         |     |

|         | PIPEn control registers (PIPEnCTR) (n = 4 to 7)                                                |     |

| 13.3.32 | PIPEn transaction counter enable registers (PIPEnTRE) (n = 4, 5)                               | 608 |

| 13.3.33 | PIPEn transaction counter registers (PIPEnTRN) (n = 4, 5)                                      | 609 |

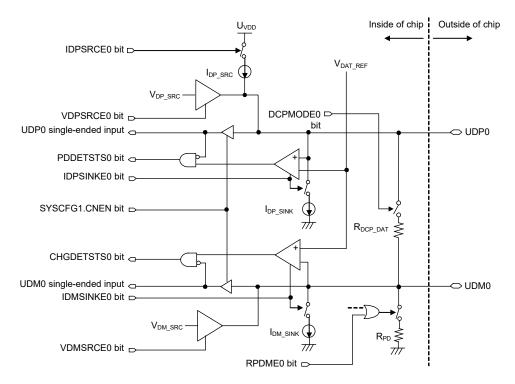

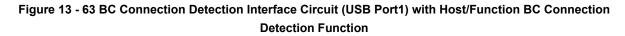

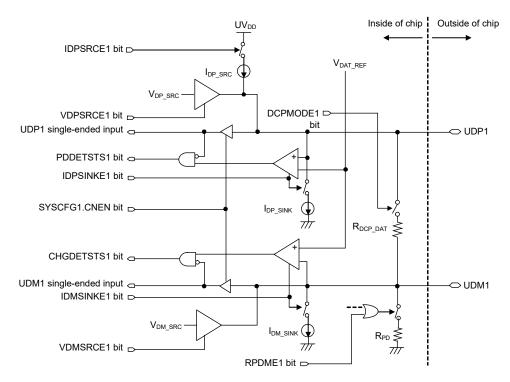

| 13.3.34 | BC control register n (USBBCCTRLn) (n = 0, 1)                                                  | 610 |

| 13.3.35 | BC option control register n (USBBCOPTn) (n = 0, 1)                                            | 614 |

| 13.3.36 | USB clock selection register (UCKSEL)                                                          | 618 |

| 13.3.37 | USB module control register (USBMC)                                                            | 619 |

| 13.3.38 | Device address n configuration registers (DEVADDn) (n = 0 to 5)                                | 620 |

| 13.4 O  | peration                                                                                       | 621 |

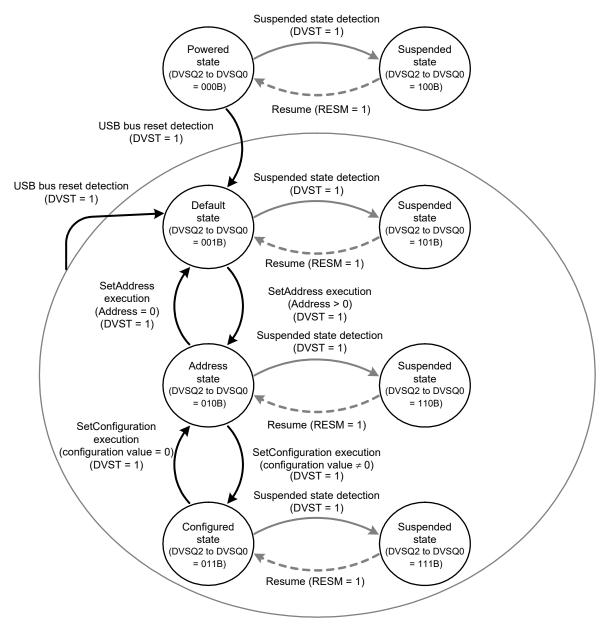

| 13.4.1  | System control                                                                                 | 621 |

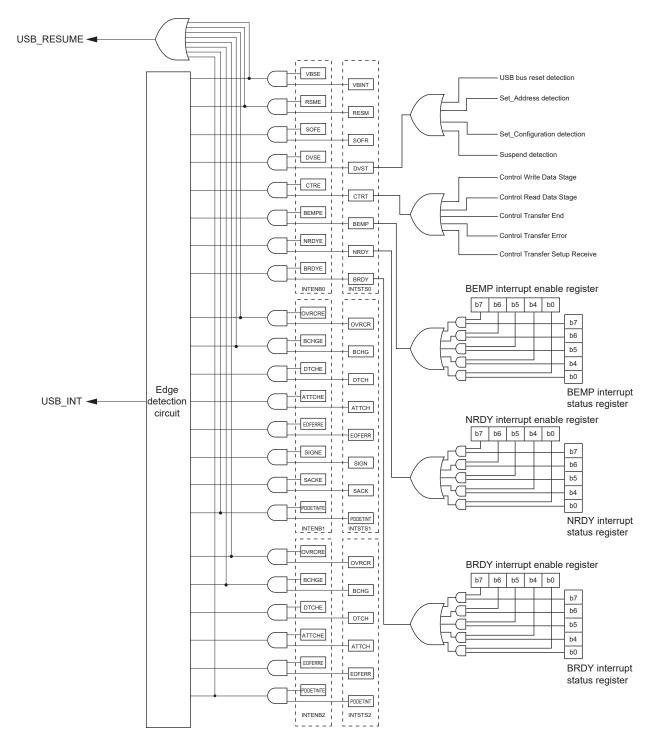

| 13.4.2  | Interrupt sources                                                                              | 626 |

| 13.4.3  | Interrupts                                                                                     | 630 |

| 13.4.4  | Pipe control                                                                                   |     |

| 13.4.5  | FIFO buffer memory                                                                             |     |

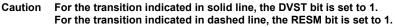

| 13.4.6  | Control transfers (DCP)                                                                        |     |

| 13.4.7  | Bulk transfers (PIPE4, PIPE5)                                                                  |     |

| 13.4.8  | Interrupt transfers (PIPE6, PIPE7)                                                             |     |

| 13.4.9  | SOF interpolation function                                                                     |     |

|         | Pipe schedule                                                                                  |     |

|         | Controlling battery charging detection                                                         |     |

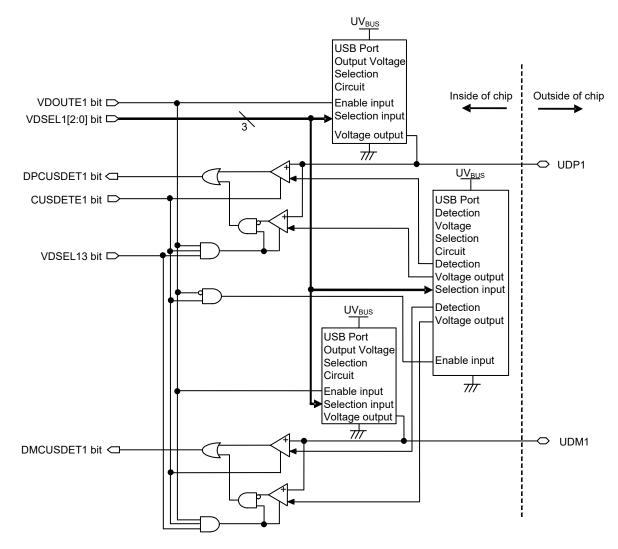

|         | Battery charging connection detection optional functions                                       |     |

| 10.7.12 |                                                                                                | 000 |

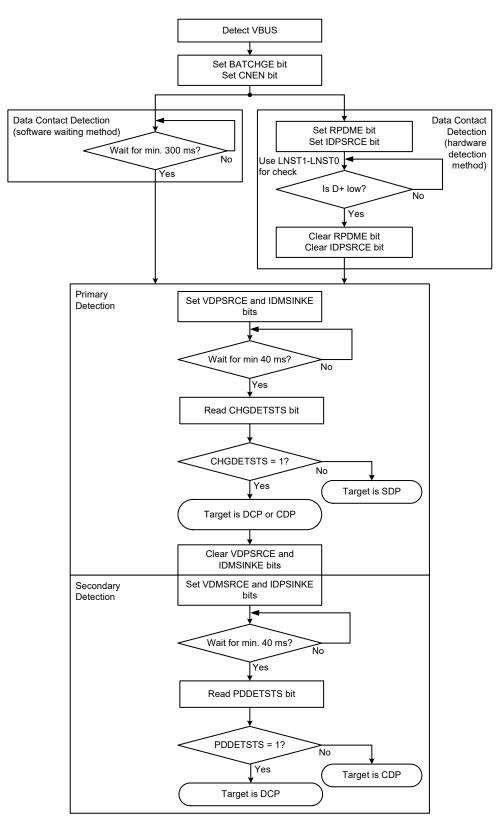

| 13.4.13 Battery charging detection processing                                                                              | . 661 |

|----------------------------------------------------------------------------------------------------------------------------|-------|

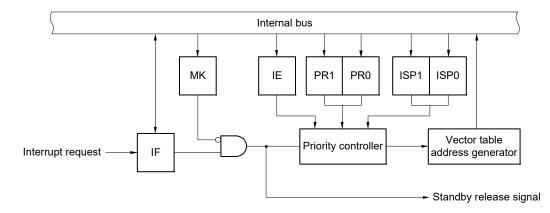

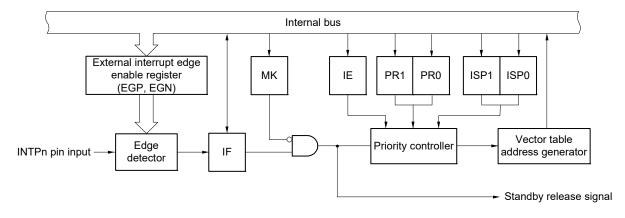

| 14. INTERRUPT FUNCTIONS                                                                                                    | . 666 |

| 14.1 Interrupt Function Types                                                                                              | . 666 |

| 14.2 Interrupt Sources and Configuration                                                                                   |       |

| 14.3 Registers Controlling Interrupt Functions                                                                             |       |

| 14.3.1 Interrupt request flag registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H)                                               |       |

| 14.3.2 Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)                                                  |       |

| 14.3.3 Priority specification flag registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H) |       |

| 14.3.4 External interrupt rising edge enable register (EGP0, EGP1),                                                        | -     |

| external interrupt falling edge enable register (EGN0, EGN1)                                                               | 679   |

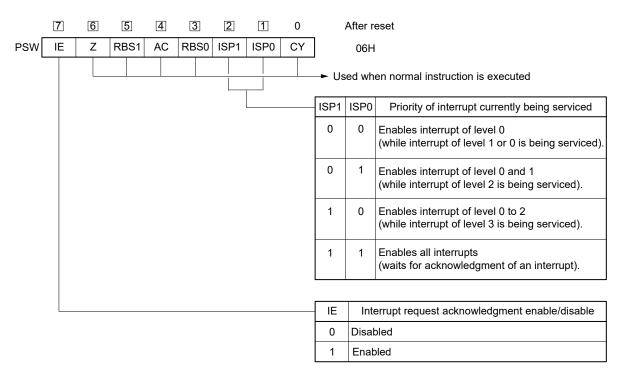

| 14.3.5 Program status word (PSW)                                                                                           | . 681 |

| 14.4 Interrupt Servicing Operations                                                                                        |       |

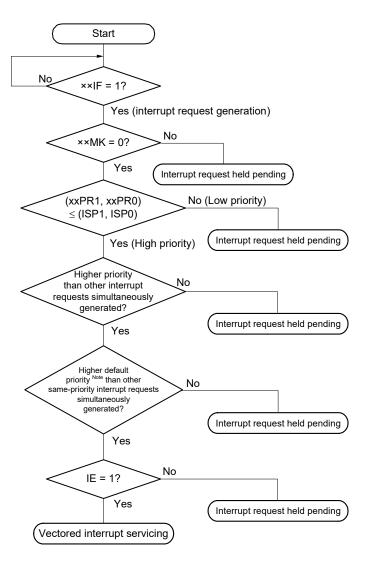

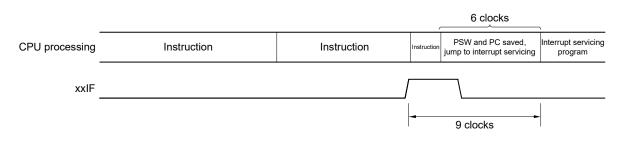

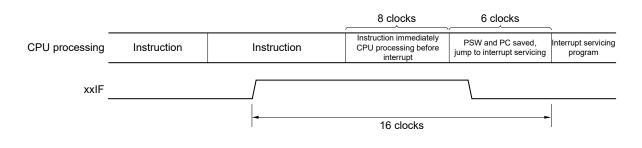

| 14.4.1 Maskable interrupt request acknowledgment                                                                           | . 682 |

| 14.4.2 Software interrupt request acknowledgment                                                                           | . 685 |

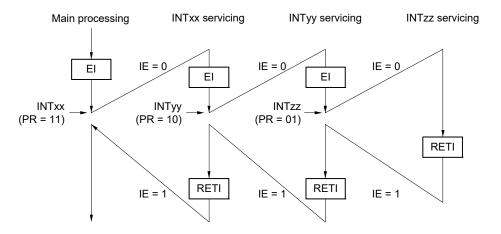

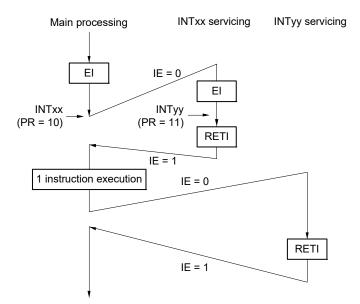

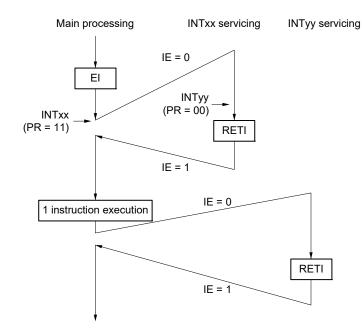

| 14.4.3 Multiple interrupt servicing                                                                                        | . 685 |

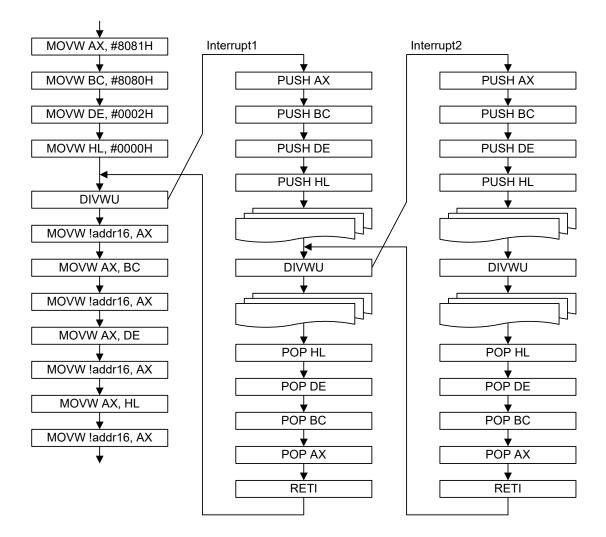

| 14.4.4 Interrupt servicing during division instruction                                                                     | . 689 |

| 14.4.5 Interrupt request hold                                                                                              | . 691 |

| 15. STANDBY FUNCTION                                                                                                       | . 692 |

| 15.1 Standby Function                                                                                                      | . 692 |

| 15.2 Registers controlling standby function                                                                                | . 693 |

| 15.3 Standby Function Operation                                                                                            |       |

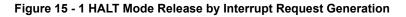

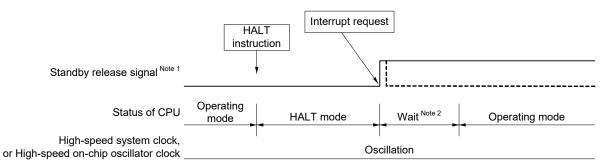

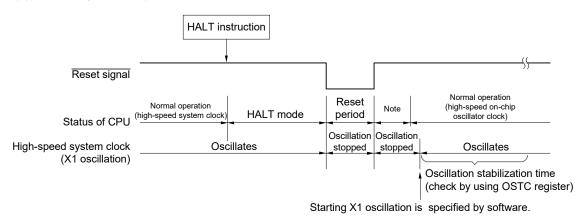

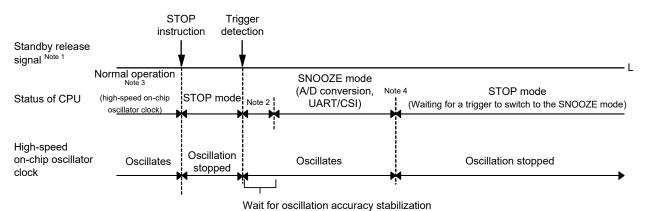

| 15.3.1 HALT mode                                                                                                           | . 694 |

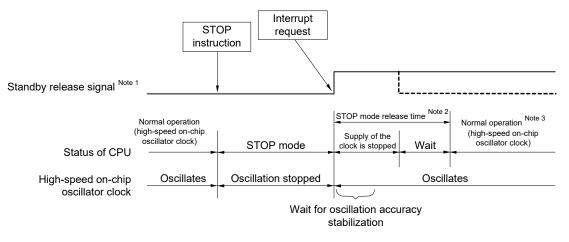

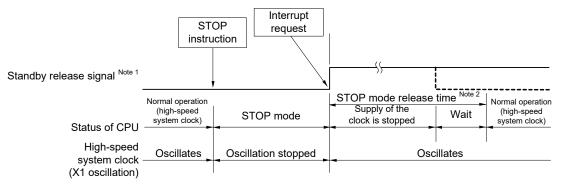

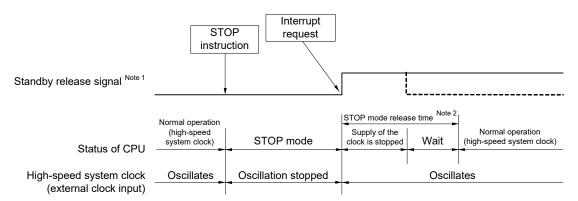

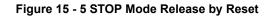

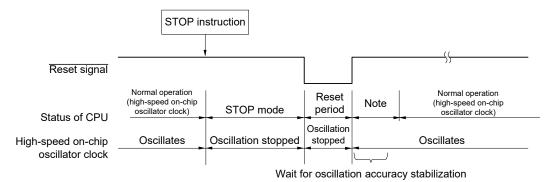

| 15.3.2 STOP mode                                                                                                           | . 698 |

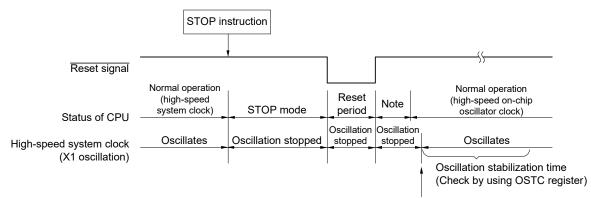

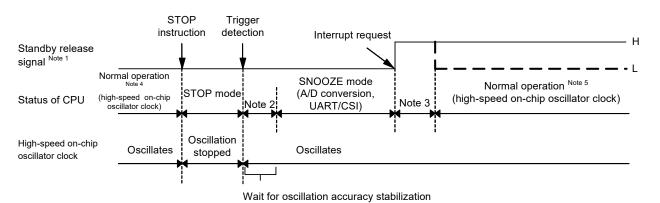

| 15.3.3 SNOOZE mode                                                                                                         | . 703 |

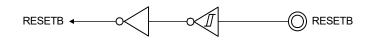

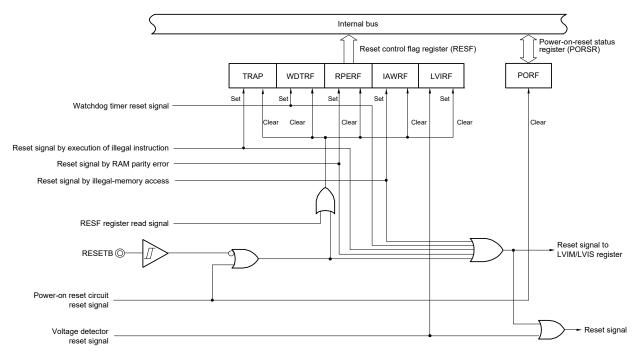

| 16. RESET FUNCTION                                                                                                         | . 706 |

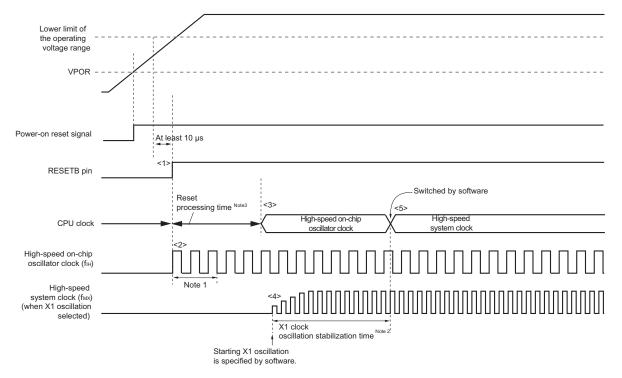

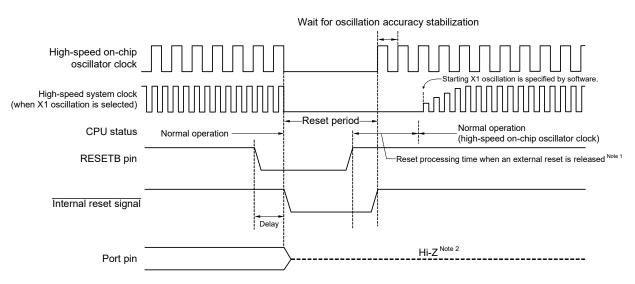

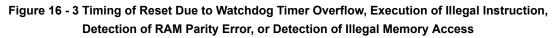

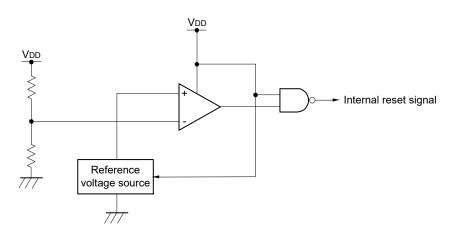

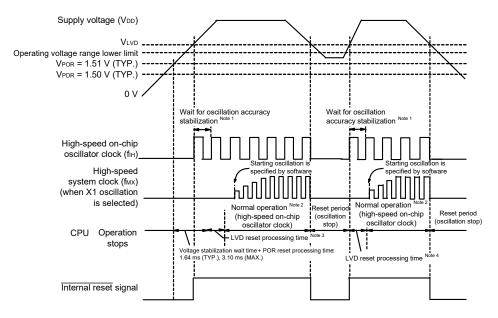

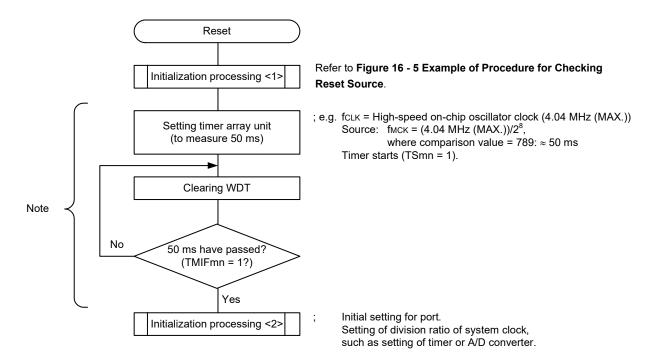

| 16.1 Timing of Reset Operation                                                                                             | . 708 |

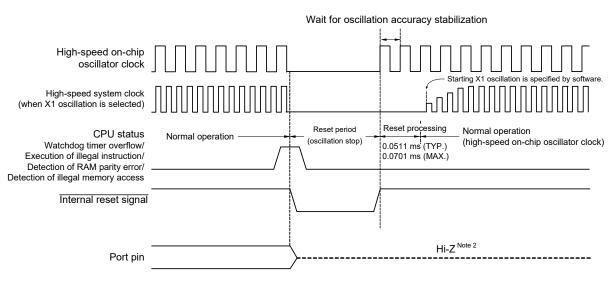

| 16.2 Register for Confirming Reset Source                                                                                  |       |

| 16.2.1 Reset control flag register (RESF)                                                                                  |       |

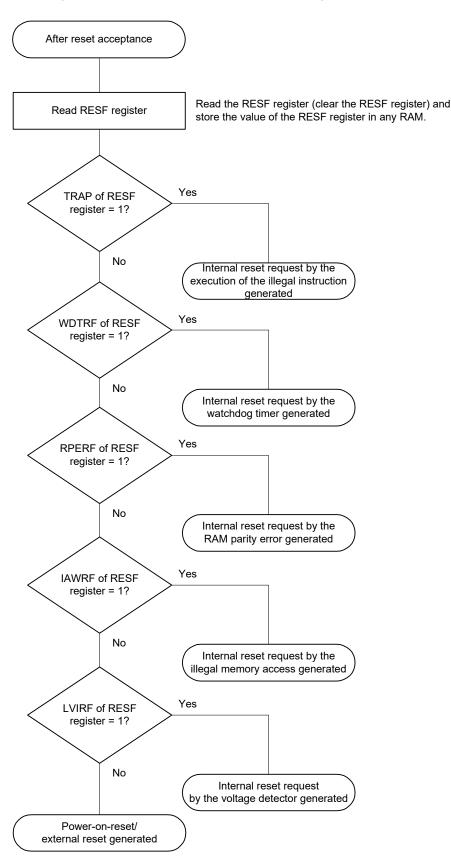

| 16.2.2 Peripheral reset control register 0 (PRR0)                                                                          |       |

| 16.2.3 Peripheral reset control register 2 (PRR2)                                                                          |       |

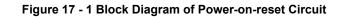

| 17. POWER-ON-RESET CIRCUIT                                                                                                 | . 717 |

| 17.1 Functions of Power-on-reset Circuit                                                                                   |       |

| 17.2 Configuration of Power-on-reset Circuit                                                                               |       |

| 17.3     Operation of Power-on-reset Circuit                                                                               |       |

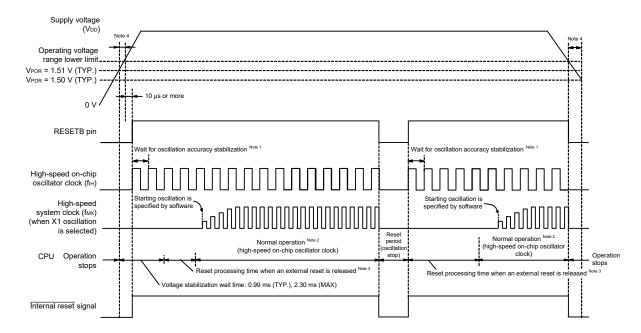

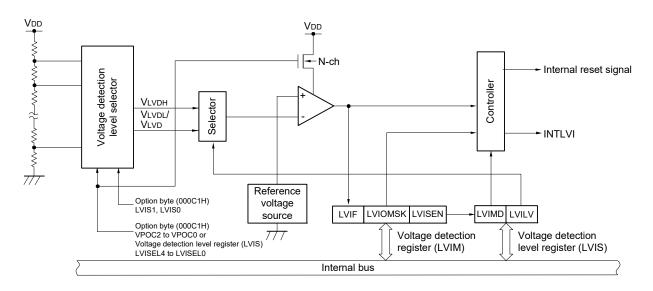

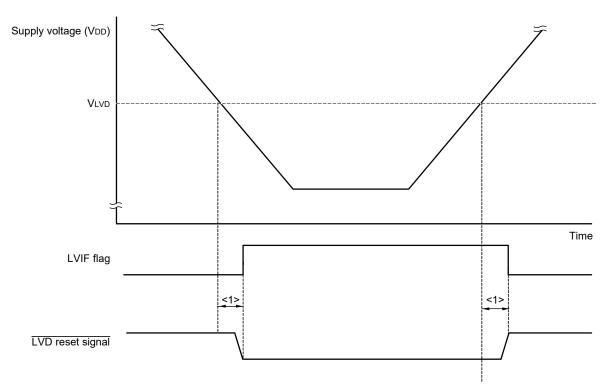

| 18. VOLTAGE DETECTOR                                                                                                       | . 722 |

| 18.1 Functions of Voltage Detector                                                                                         |       |

| 18.2 Configuration of Voltage Detector                                                                                     |       |

| 18.3 Registers Controlling Voltage Detector                                                                                |       |

| 18.3.1 Voltage detection register (LVIM)                                                                                   |       |

| 18.3.2 Voltage detection level register (LVIS)                                                                             |       |

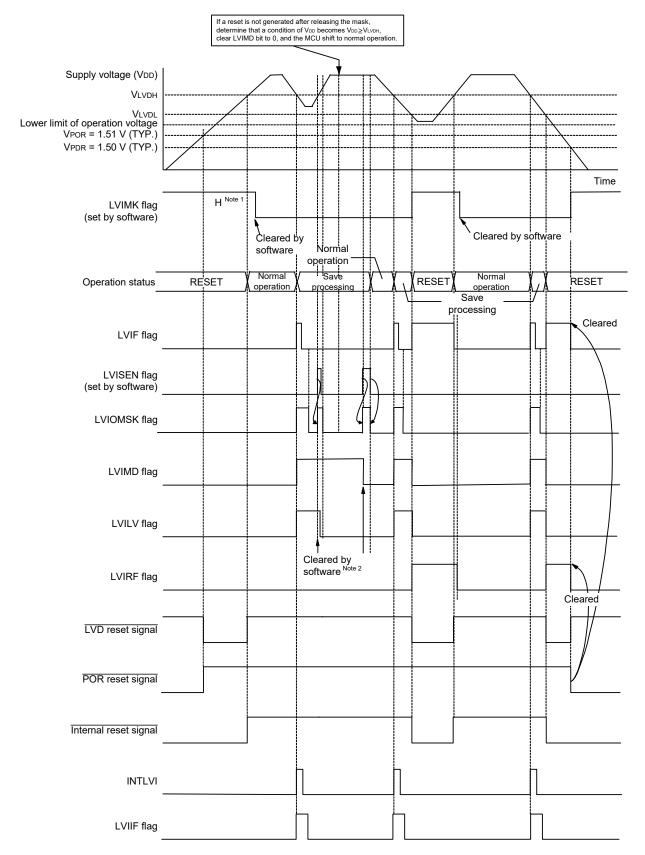

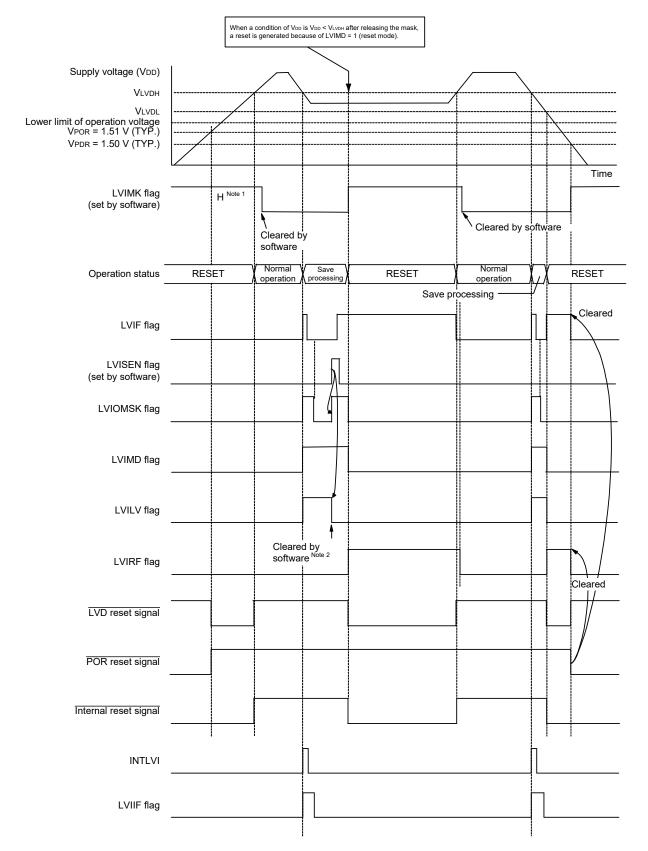

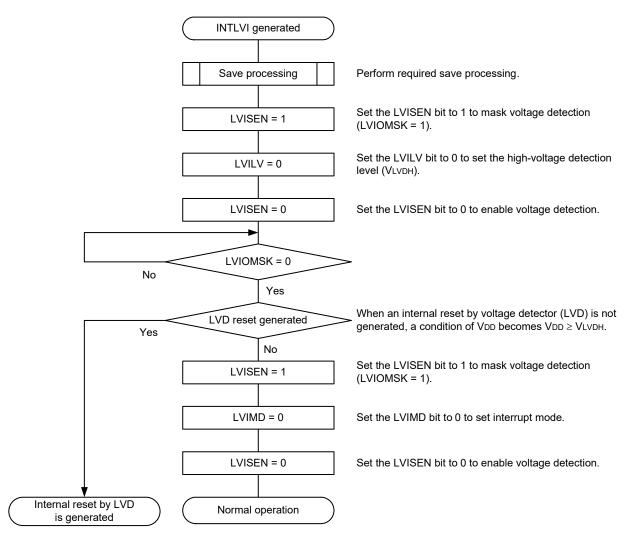

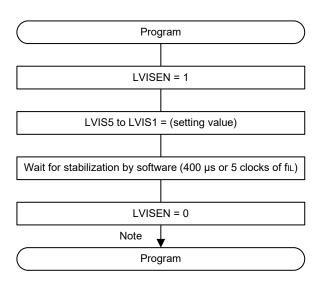

| 18.4 Operation of Voltage Detector                                                                                         |       |

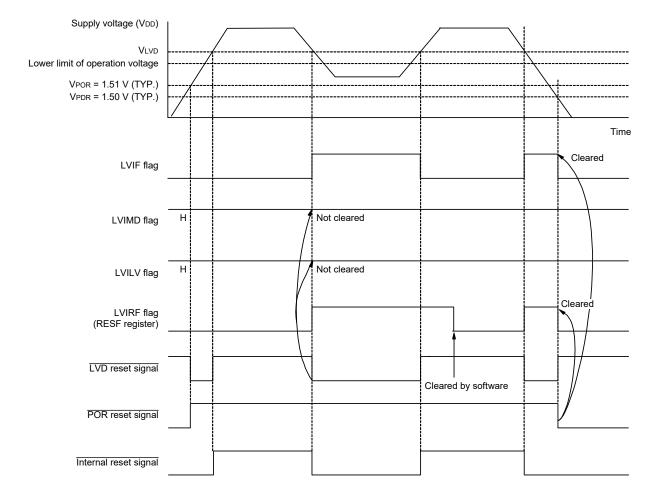

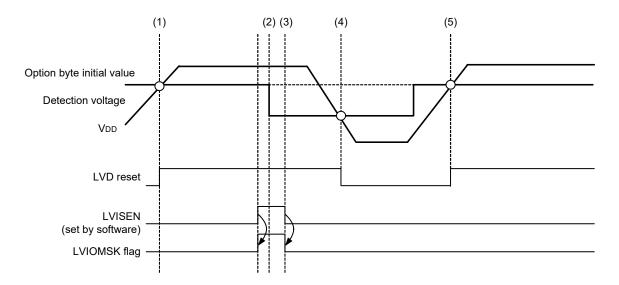

| 18.4.1 When used as reset mode                                                                                             |       |

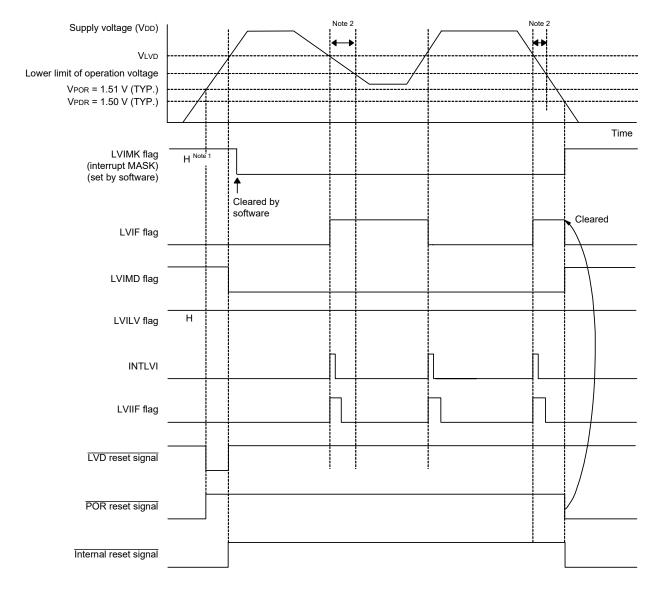

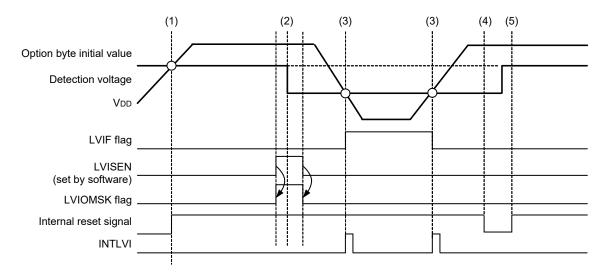

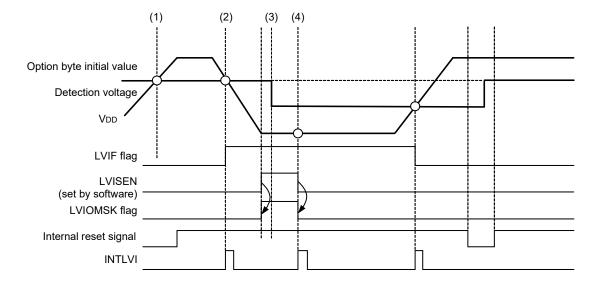

| 18.4.2 When used as interrupt mode                                                                                         |       |

|                                                                                                                            |       |

| 734   |

|-------|

| 739   |

| 740   |

| . 741 |

| 743   |

|       |

| 745   |

| 745   |

| 746   |

| 746   |

| 746   |

| 750   |

| 753   |

| 755   |

| 756   |

| 757   |

| 759   |

| 761   |

| 763   |

| 704   |

| 764   |

| 764   |

| 765   |

| 765   |

| 765   |

| 766   |

| 767   |

| 774   |

| 775   |

|       |

| 776   |

| 777   |

| 779   |

| 779   |

| 780   |

| 780   |

| 781   |

| 782   |

| 782   |

| 782   |

| 783   |

| 783   |

| 783   |

| 783   |

| 784   |

| 784   |

| 785   |

| 787   |

|       |

| 22.4.4      | Communication commands                                                | 788 |

|-------------|-----------------------------------------------------------------------|-----|

| 22.5 Pro    | cessing Time for Each Command When PG-FP6 Is in Use (Reference Value) | 790 |

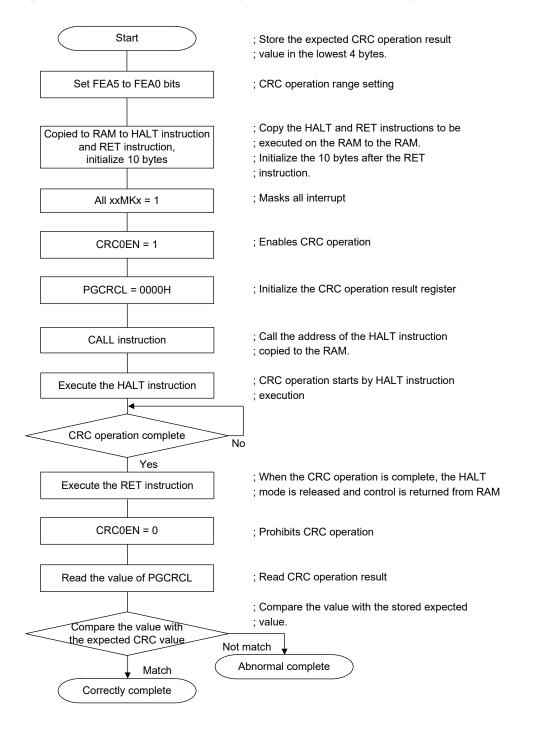

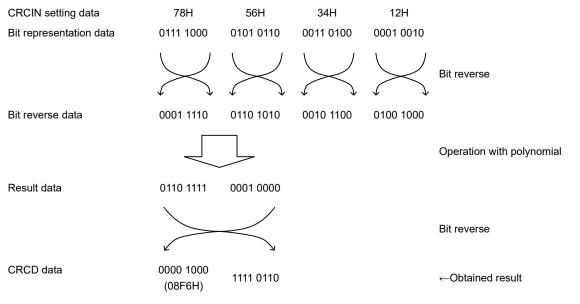

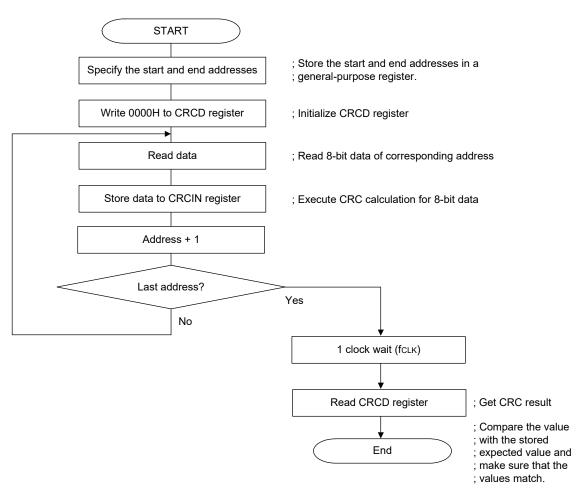

| 22.6 Self   | f-Programming                                                         | 791 |

| 22.6.1 S    | Self-programming procedure                                            | 792 |

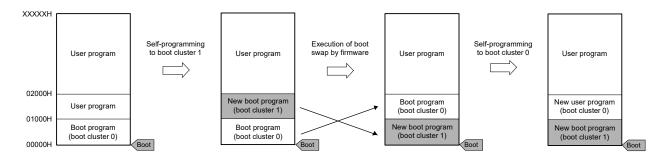

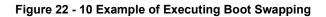

| 22.6.2 E    | Boot swap function                                                    | 793 |

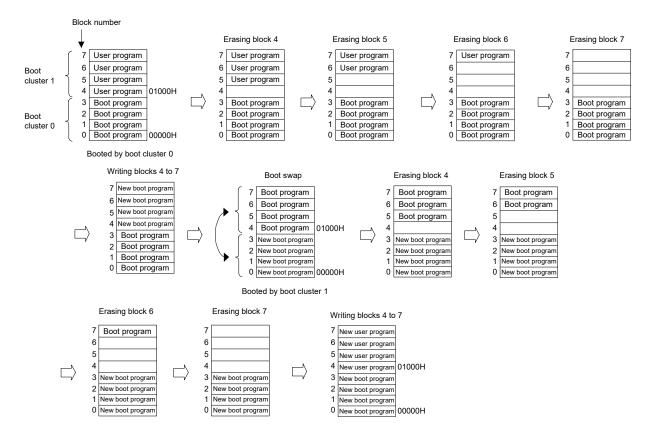

| 22.6.3 F    | -lash shield window function                                          | 795 |

| 22.7 Sec    | curity Settings                                                       | 796 |

| 22.8 Dat    | a Flash                                                               | 798 |

| 22.8.1 C    | Data flash overview                                                   | 798 |

| 22.8.2 F    | Register controlling data flash memory                                | 799 |

| 22.8.3 F    | Procedure for accessing data flash memory                             | 800 |

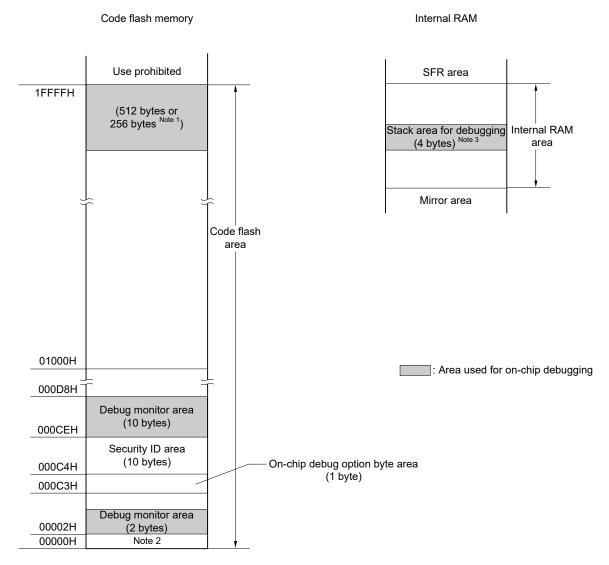

| 23. ON-CH   | IP DEBUG FUNCTION                                                     | 801 |

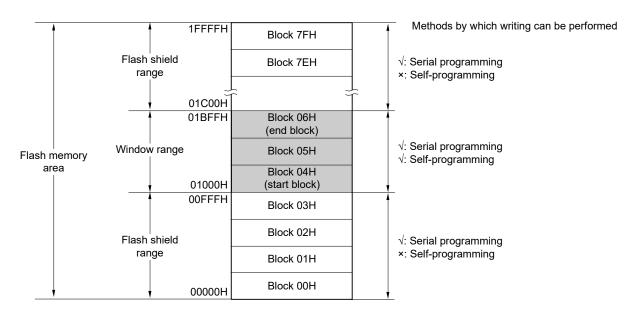

| 23.1 Cor    | nnecting E1 On-chip Debugging Emulator                                | 801 |

| 23.2 On-    | Chip Debug Security ID                                                | 802 |

| 23.3 Sec    | curing of User Resources                                              | 802 |

| 24. BCD C   | ORRECTION CIRCUIT                                                     | 804 |

| 24.1 BCI    | D Correction Circuit Function                                         | 804 |

| 24.2 Reg    | gisters Used by BCD Correction Circuit                                | 804 |

| 24.2.1 E    | BCD correction result register (BCDADJ)                               | 804 |

| 24.3 BCI    | D Correction Circuit Operation                                        | 805 |

| 25. INSTRI  | JCTION SET                                                            | 807 |

| 25.1 Cor    | nventions Used in Operation List                                      | 807 |

|             | Dperand identifiers and specification methods                         |     |

|             | Description of operation column                                       |     |

|             | Description of flag operation column                                  |     |

|             | PREFIX instruction                                                    |     |

|             | eration List                                                          |     |

| 26. ELECT   | RICAL SPECIFICATIONS                                                  | 823 |

| 27. PACKA   | GE DRAWINGS                                                           | 824 |

| REVISION HI | STORY                                                                 | 825 |

## RENESAS

## R9A02G015

ASSP (USB Power Delivery Controller)

R19UH0112EJ0100 Rev.1.00 Mar 29, 2019

## **CHAPTER 1 OUTLINE**

### 1.1 Features

Ultra-low power consumption technology

- VDD = single power supply voltage of 2.7 to 5.5 V

- HALT mode

- STOP mode

- SNOOZE mode

#### RL78 CPU core

- CISC architecture with 3-stage pipeline

- Minimum instruction execution time: 0.04167 µs: @ 24 MHz operation with high-speed on-chip oscillator

- Multiply/divide/multiply & accumulate instructions are supported.

- Address space: 1 MB

- General-purpose registers: (8-bit register × 8) × 4 banks

- On-chip RAM: 7 KB

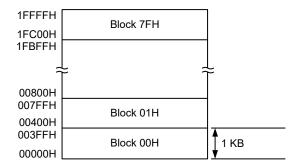

#### Code flash memory

- Code flash memory: 128 KB

- Block size: 1 KB

- Prohibition of block erase and rewriting (security function)

- On-chip debug function

- Self-programming (with boot swap function/flash shield window function)

#### Data flash memory

- Data flash memory: 2 KB

- Back ground operation (BGO): Instructions can be executed from the program memory while rewriting the data flash memory.

- Number of rewrites: 1,000,000 times (TYP.)

- Voltage of rewrites: VDD = 2.7 to 5.5 V

#### High-speed on-chip oscillator

- Select from 48 MHz, 24 MHz, 16 MHz, 12 MHz, 8 MHz, 6 MHz, 4 MHz, 3 MHz, 2 MHz, and 1 MHz

- High accuracy: ±1.0% (VDD = 2.7 to 5.5 V, TA = -20 to +85°C)

#### Operating ambient temperature

• TA = -40 to +85°C (A: Consumer applications)

Power management and reset function

- On-chip power-on-reset (POR) circuit

- On-chip voltage detector (LVD) (Select reset from 6 levels)

#### USB

- Complying with USB Specification Revision 2.0, incorporating host/function controller

- Corresponding to full-speed transfer (12 Mbps) and low-speed (1.5 Mbps)

- Complying with Battery Charging Specification Revision 1.2

- Compliant with the 2.1 A/1.0 A charging mode.

#### Serial interfaces

- CSI: 2 channels

- UART: 1 channel

- Simplified I<sup>2</sup>C: 2 channels

- I<sup>2</sup>C: 2 or 3 channels

#### Timers

- 16-bit timer: 8 channels

- 12-bit interval timer: 1 channel

- Watchdog timer: 1 channel

#### A/D converter

- 8/10-bit resolution A/D converter (VDD = 2.7 to 5.5 V)

- Analog input: 8 channels

- Internal reference voltage (1.45 V) and temperature sensor

#### I/O ports

- I/O port: 23 or 28 (N-ch open drain I/O [withstand voltage of 6 V]: 5, N-ch open drain I/O [VDD withstand voltage]: 8 or 13)

- Can be set to N-ch open drain, TTL input buffer, and on-chip pull-up resistor

- On-chip clock output/buzzer output controller

#### Others

• On-chip BCD (binary-coded decimal) correction circuit

**Remark** The functions mounted depend on the product. See **1.6 Outline of Functions**.

#### $\bigcirc$ ROM, RAM capacities

| Flash ROM | Data flash       | RAM       | R9A02              | 2G015                 |

|-----------|------------------|-----------|--------------------|-----------------------|

| Flash ROW | Data ilasin KAwi |           | 32 pins (with USB) | 32 pins (without USB) |

| 128 KB    | 2 KB             | 7 KB Note | R9A02G0150         | R9A02G0151            |

**Note** The flash library uses RAM in self-programming and rewriting of the data flash memory.

The target products and start address of the RAM areas used by the flash library are shown below.

R9A02G0150/R9A02G0151: Start address FE300H

## 1.2 Ordering Information

#### Figure 1 - 1 Part Number and Package of R9A02G015

| Pin count | Package                  | Ordering Part Number | Remarks                          |

|-----------|--------------------------|----------------------|----------------------------------|

| 32 pins   | 32-pin QFN               | R9A02G015020GNP#AC0  | Product with USB (R9A02G0150)    |

|           | (4 × 4 mm, 0.4 mm pitch) | R9A02G015120GNP#AC0  | Product without USB (R9A02G0151) |

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

### **1.3 Pin Configuration (Top View)**

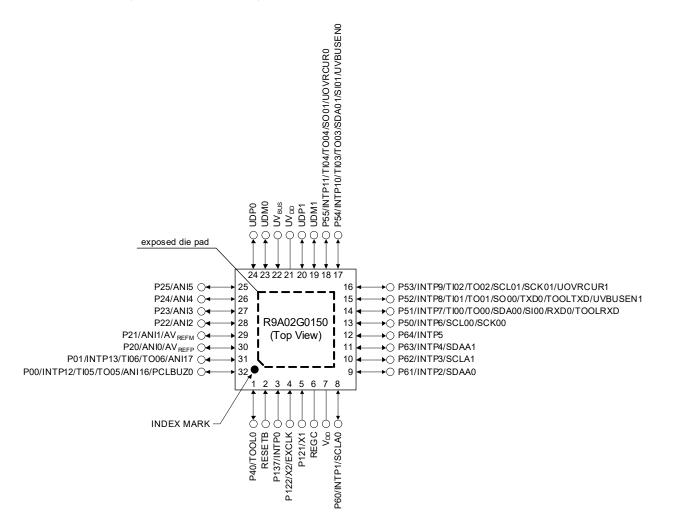

#### 1.3.1 32-pin product (with USB)

• 32-pin QFN (4 × 4 mm, 0.4 mm pitch)

Caution 1. Connect the exposed die pad (Vss) to ground.

Caution 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu F).$

Remark For pin identification, see 1.4 Pin Identification.

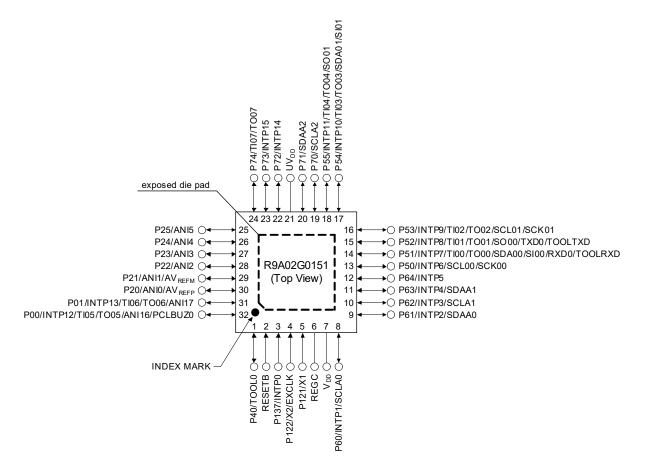

### 1.3.2 32-pin product (without USB)

• 32-pin QFN (4 × 4 mm, 0.4 mm pitch)

Caution 1. Connect the exposed die pad (Vss) to ground. Caution 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

Remark For pin identification, see 1.4 Pin Identification.

## 1.4 Pin Identification

| ANI0 to ANI5, ANI16, ANI17:   | Analog input                                     |

|-------------------------------|--------------------------------------------------|

| AVREFM:                       | A/D converter reference potential (- side) input |

| AVREFP:                       | A/D converter reference potential (+ side) input |

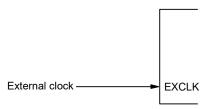

| EXCLK:                        | External clock input (main system clock)         |

| INTP0 to INTP15:              | External interrupt input                         |

| P00, P01:                     | Port 0                                           |

| P20 to P25:                   | Port 2                                           |

| P40:                          | Port 4                                           |

| P50 to P55:                   | Port 5                                           |

| P60 to P64:                   | Port 6                                           |

| P70 to P74:                   | Port 7                                           |

| P121, P122:                   | Port 12                                          |

| P137:                         | Port 13                                          |

| PCLBUZ0:                      | Programmable clock output/buzzer output          |

| REGC:                         | Regulator capacitance                            |

| RESETB:                       | Reset                                            |

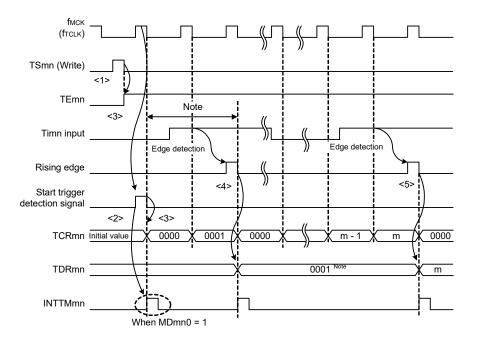

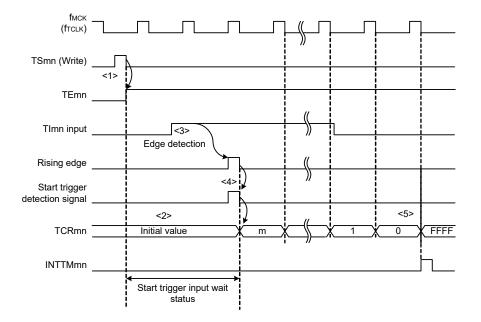

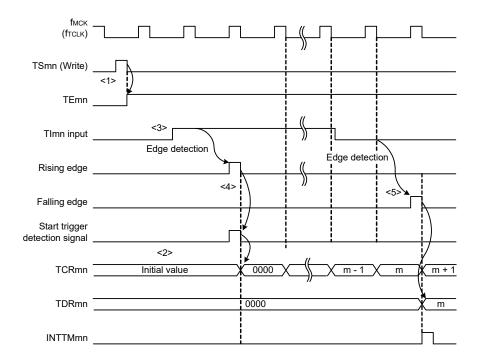

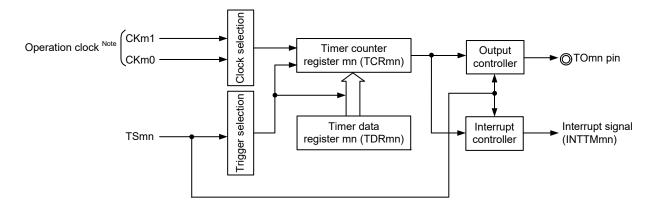

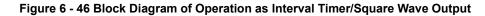

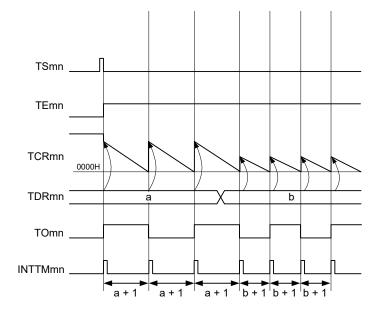

| RxD0:                         | Receive data                                     |