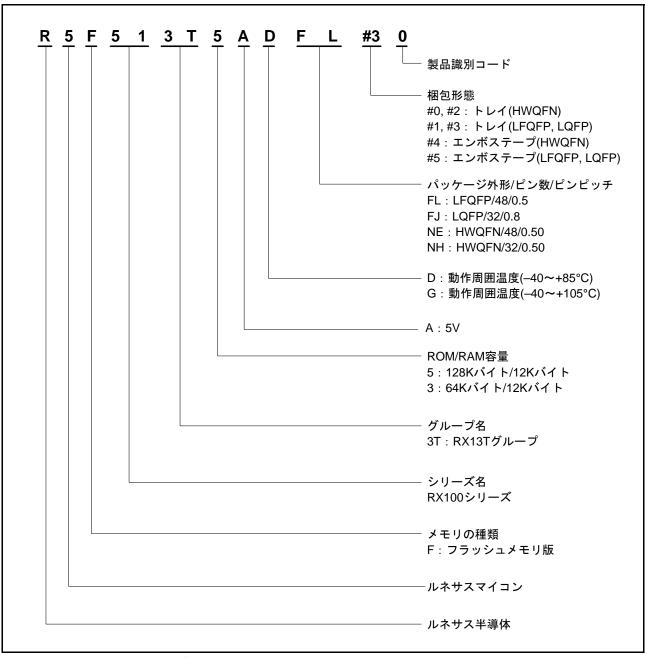

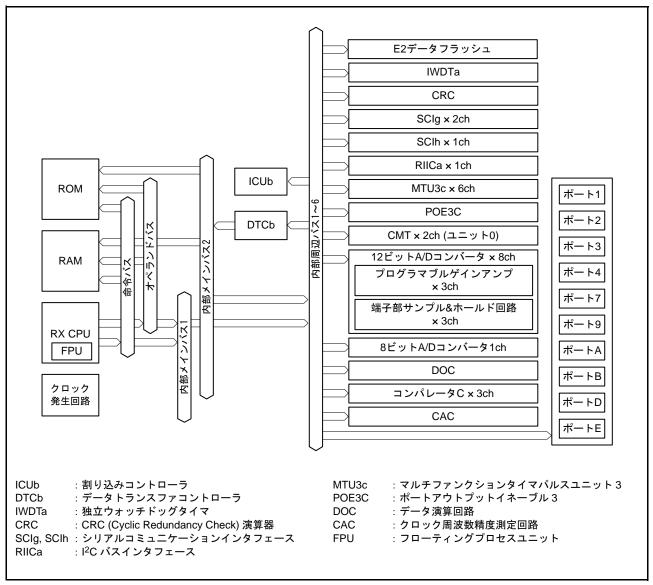

# RX13Tグループ

ユーザーズマニュアル ハードウェア編

ルネサス32ビットマイクロコンピュータ RXファミリ/RX100シリーズ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサスエレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサスエレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、 著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではありません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、 複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等

当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ 対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。)から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。)によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的に 支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

#### 本社所在地

〒 135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

## 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属し ます。

#### お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。

#### 5. クロックについて

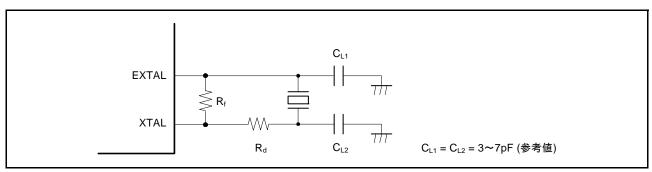

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

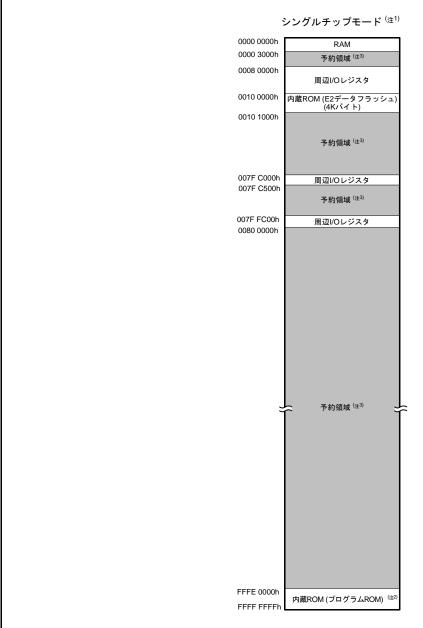

#### 7. リザーブアドレス (予約領域) のアクセス禁止

リザーブアドレス (予約領域) のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス (予約領域) があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

## このマニュアルの使い方

## 1. 目的と対象者

このマニュアルは、本マイコンのハードウェア機能と電気的特性をユーザに理解していただくためのマニュアルです。本マイコンを用いた応用システムを設計するユーザを対象にしています。このマニュアルを使用するには、電気回路、論理回路、マイクロコンピュータに関する基本的な知識が必要です。

このマニュアルは、大きく分類すると、製品の概要、CPU、システム制御機能、周辺機能、電気的特性、 使用上の注意で構成されています。

本マイコンは、注意事項を十分確認の上、使用してください。注意事項は、各章の本文中、各章の最後、 注意事項の章に記載しています。

改訂記録は旧版の記載内容に対して訂正または追加した主な箇所をまとめたものです。改訂内容すべて を記録したものではありません。詳細は、このマニュアルの本文でご確認ください。

RX13Tグループでは次のドキュメントを用意しています。ドキュメントは最新版を使用してください。 最新版はルネサスエレクトロニクスのホームページに掲載されています。

| ドキュメントの種類                   | 記載内容                                                        | 資料名                                                 | 資料番号        |

|-----------------------------|-------------------------------------------------------------|-----------------------------------------------------|-------------|

| データシート                      | ハードウェアの概要と電気的特性                                             | RX13Tグループ<br>データシート                                 | R01DS0341JJ |

| ユーザーズマニュアル<br>ハードウェア編       | ハードウェアの仕様(ピン配置、<br>メモリマップ、周辺機能の仕様、<br>電気的特性、タイミング)と動作<br>説明 | RX13Tグループ<br>ユーザーズマニュアル<br>ハードウェア編                  | 本ユーザーズマニュアル |

| ユーザーズマニュアル<br>ソフトウェア編       | CPU・命令セットの説明                                                | RXファミリ<br>RXv1命令セットアーキテクチャ<br>ユーザーズマニュアル<br>ソフトウェア編 | R01US0032JJ |

| アプリケーションノート                 | 基板設計上の注意事項                                                  | RX ファミリ<br>ハードウェアデザインガイド                            | R01AN1411JJ |

|                             | レジスタ初期設定例                                                   | RX13T グループ<br>初期設定例                                 | _           |

|                             | 応用例参考プログラムなど                                                | _                                                   | _           |

| RENESAS TECHNICAL<br>UPDATE | 製品の仕様、ドキュメント等に<br>関する速報                                     | _                                                   | _           |

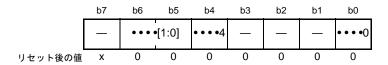

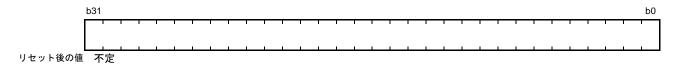

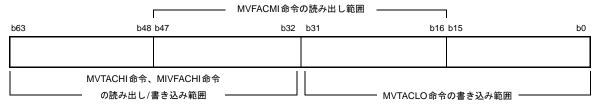

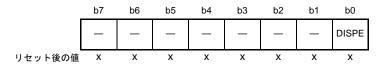

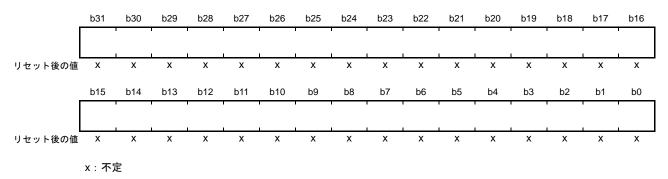

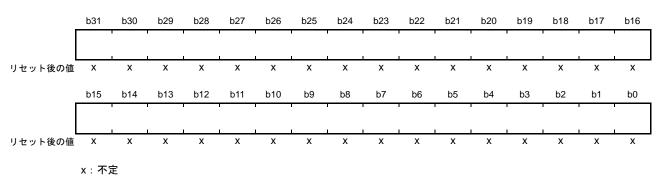

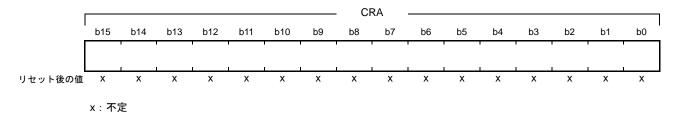

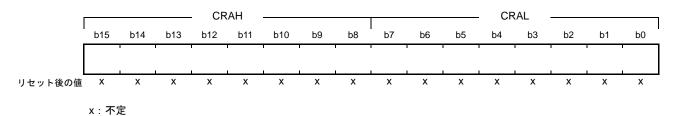

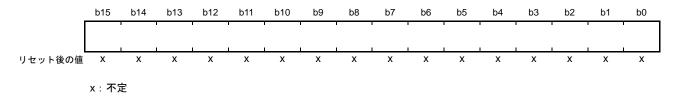

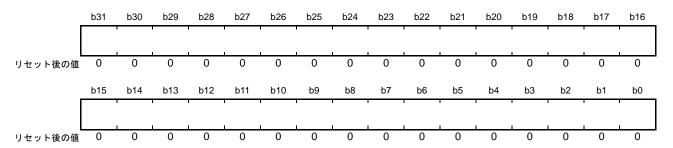

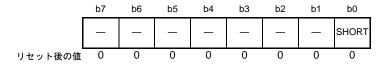

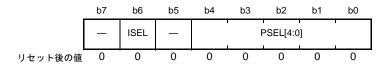

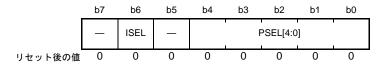

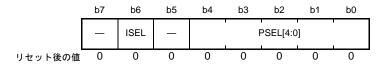

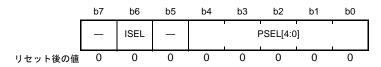

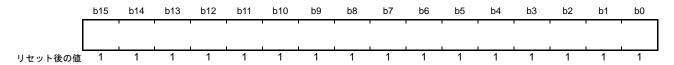

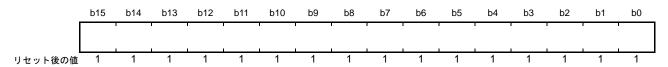

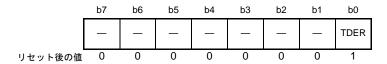

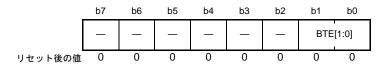

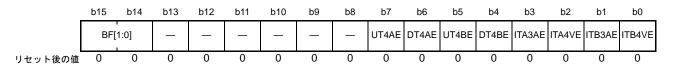

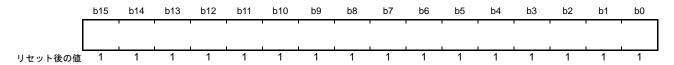

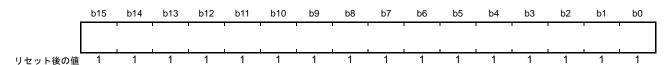

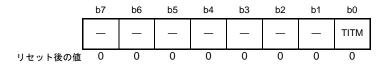

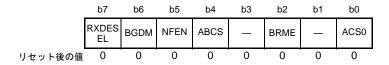

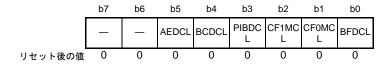

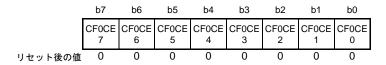

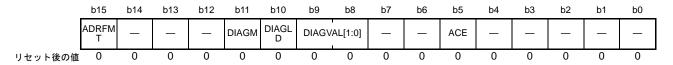

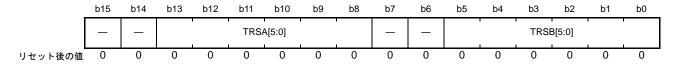

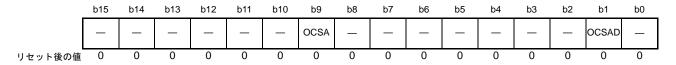

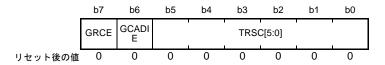

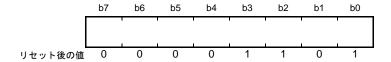

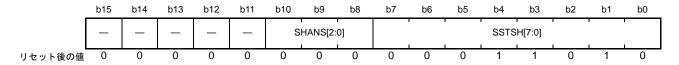

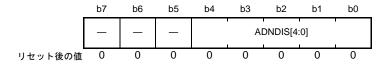

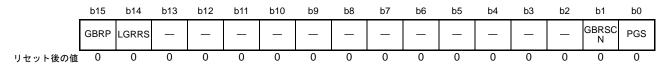

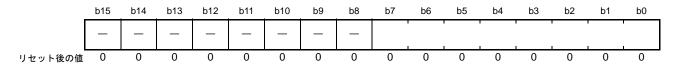

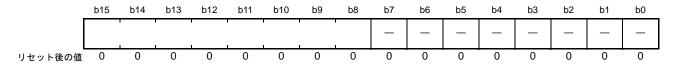

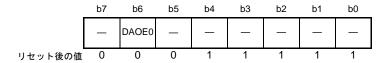

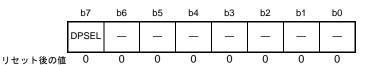

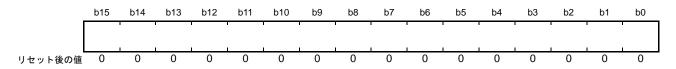

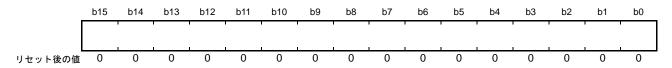

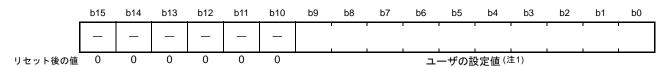

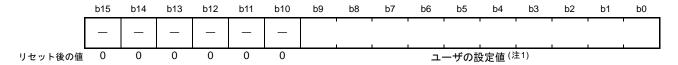

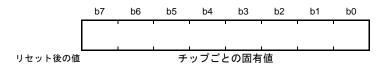

## 2. レジスタの表記

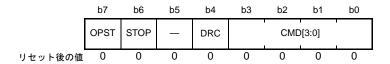

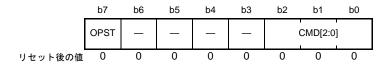

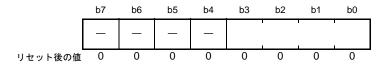

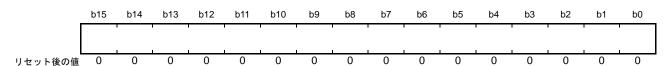

各章において「レジスタの説明」には、ビットの並びを示すビット配置図とビットに設定する内容を 説明するビット機能表があります。使用する記号、用語を以下に説明します。

### X.X.X •••• レジスタ

アドレス xxxx xxxxh

x:不定

| ビット   | シンボル      | ビット名           | 機能                                              | R/W           |

|-------|-----------|----------------|-------------------------------------------------|---------------|

| b0    | ••••0     | ・・・・ビット<br>(2) | 0: ······<br>1 <b>(</b> 設定しないでください <b>)</b> (3) | (R/W)         |

| b3-b1 | _         | (予約ビット)        | 読むと"0"が読めます。書く場合、"0"としてください                     | R/W           |

| b4    | ••••4     | ・・・・ビット        | 0: • • • • • 1: • • • •                         | R             |

| b6-b5 | ••••[1:0] | ・・・・ビット        | 00:・・・・・<br>01:・・・・・<br>上記以外は設定しないでください         | R/(W)<br>(注1) |

| b7    | _         | 予約ビット          | 読んだ場合、その値は不定。書き込みは無効になります                       | R             |

(1) R/W : 読み出し/書き込みともに有効です。

R/(W) : 読み出し/書き込みともに有効ですが、書き込みには制限があります。

制限の内容については、各レジスタの説明や注記を参照ください。

R: 読み出しのみ有効です。書き込みは無効になります。

(2) 予約ビットです。書き込みを行う場合には、指定された値を書き込んでください。指定外の値を書き込んだ場合の動作は保証されません。

(3) 設定しないでください。設定した場合の動作は保証されません。

## 3. 略語および略称の説明

| 略語/略称 | フルスペル                                         | 備考                          |

|-------|-----------------------------------------------|-----------------------------|

| ACIA  | Asynchronous Communications Interface Adapter | 調歩同期式通信アダプタ                 |

| bps   | bits per second                               | 転送速度を表す単位、ビット/秒             |

| CRC   | Cyclic Redundancy Check                       | 巡回冗長検査                      |

| DMA   | Direct Memory Access                          | CPUの命令を介さずに直接データ転送を<br>行う方式 |

| DMAC  | Direct Memory Access Controller               | DMA を行うコントローラ               |

| GSM   | Global System for Mobile Communications       | FDD-TDMAの第二世代携帯電話の方式        |

| Hi-Z  | High Impedance                                | 回路が電気的に接続されていない状態           |

| IEBus | Inter Equipment Bus                           | _                           |

| I/O   | Input / Output                                | 入出力                         |

| IrDA  | Infrared Data Association                     | 赤外線通信の業界団体または規格             |

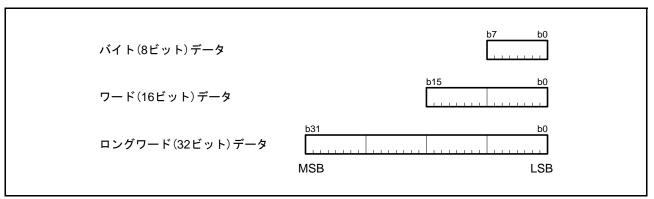

| LSB   | Least Significant Bit                         | 最下位ビット                      |

| MSB   | Most Significant Bit                          | 最上位ビット                      |

| NC    | Non-Connect                                   | 非接続                         |

| PLL   | Phase Locked Loop                             | 位相同期回路                      |

| PWM   | Pulse Width Modulation                        | パルス幅変調                      |

| SIM   | Subscriber Identity Module                    | ISO/IEC 7816規格の接触型ICカード     |

| UART  | Universal Asynchronous Receiver / Transmitter | 調歩同期式シリアルインタフェース            |

| VCO   | Voltage Controlled Oscillator                 | 電圧制御発振器                     |

すべての商標および登録商標は、それぞれの所有者に帰属します。 SuperFlash®は、米国Silicon Storage Technology, Inc.の米国、日本などの国における登録商標です。

注意:本製品はSilicon Storage Technology, Inc. からライセンスを受けたSuperFlash®を使用しています。

## 目次

| 特  | 長      |                                          | 32 |

|----|--------|------------------------------------------|----|

| 1. | 概要     |                                          | 33 |

|    | 1.1 仕  | 様概要                                      | 33 |

|    | 1.2 製  | 品一覧                                      | 37 |

|    | 1.3 ブ  | ロック図                                     | 39 |

|    | 1.4 端  | 子機能                                      | 40 |

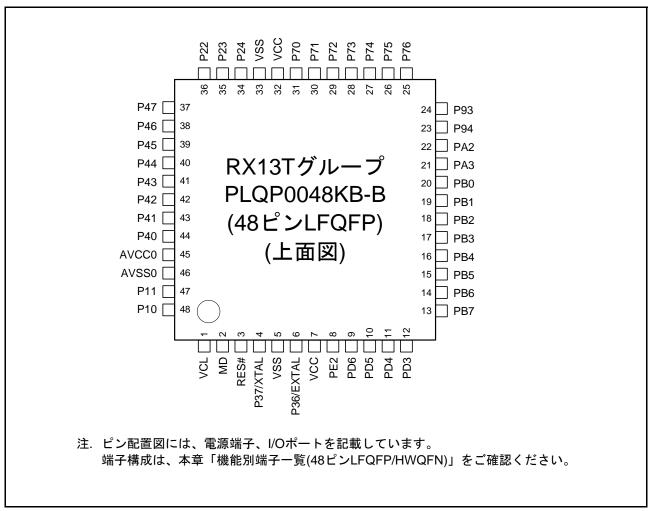

|    | 1.5 Ľ  | ン配置図                                     | 43 |

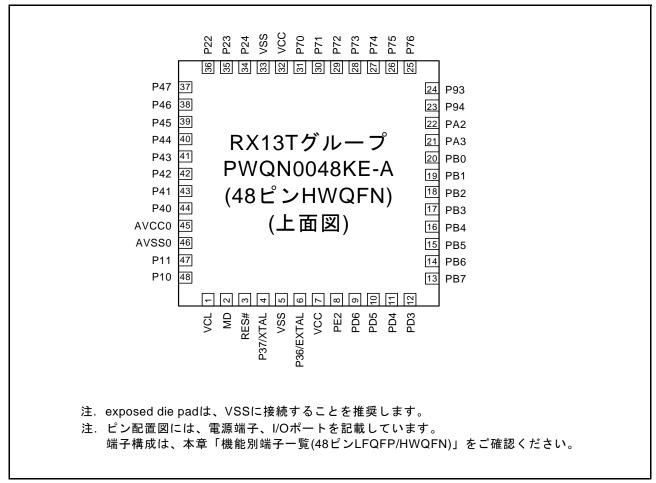

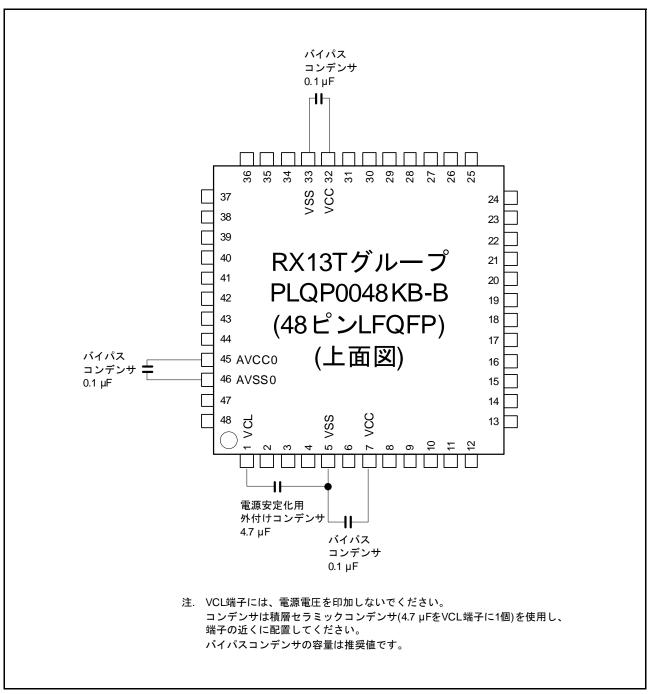

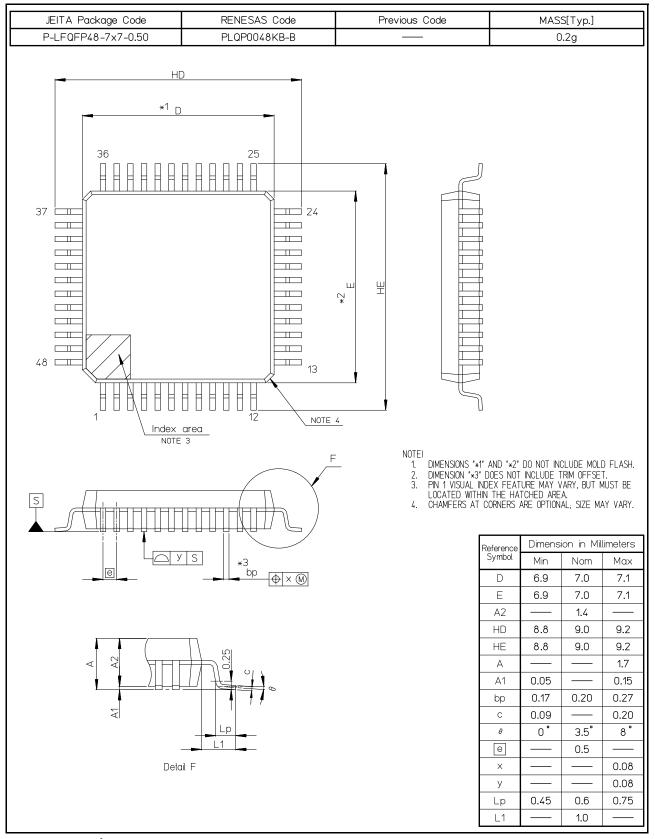

|    | 1.5.1  | 48 ピン LFQFP                              | 43 |

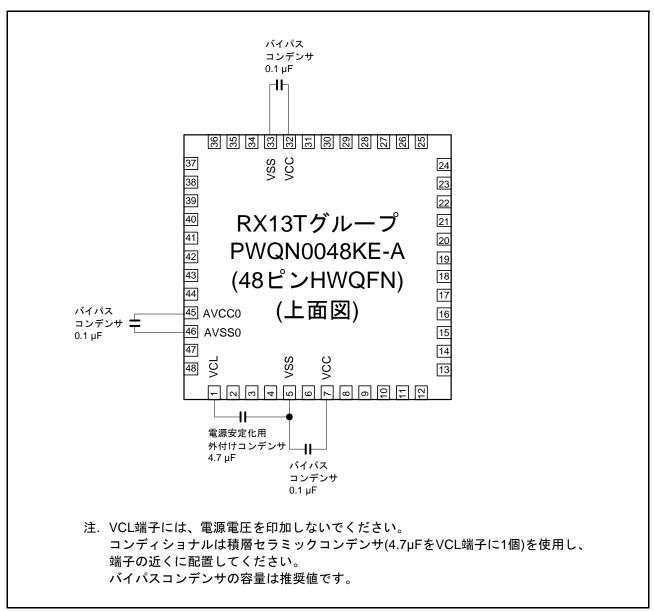

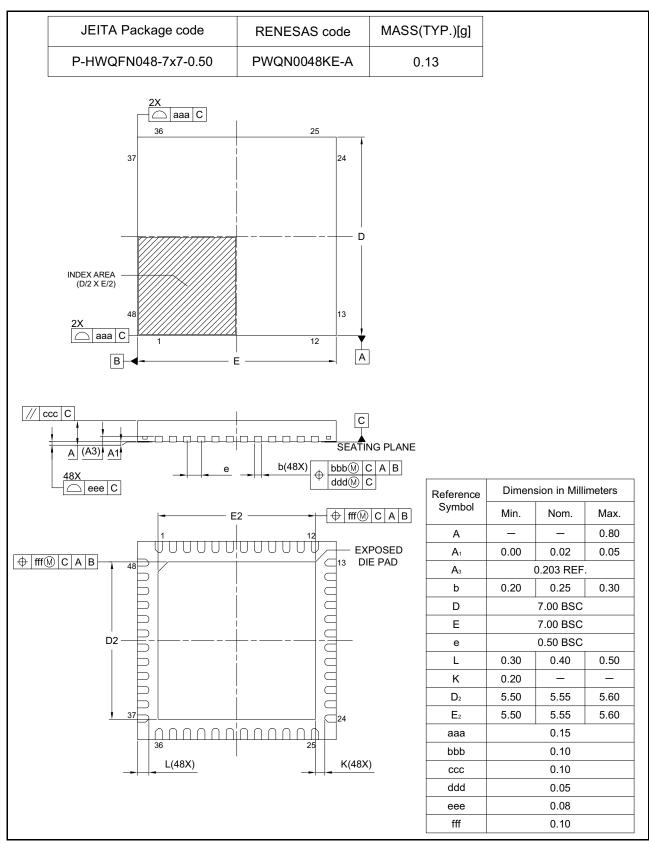

|    | 1.5.2  | 48 ピン HWQFN                              | 44 |

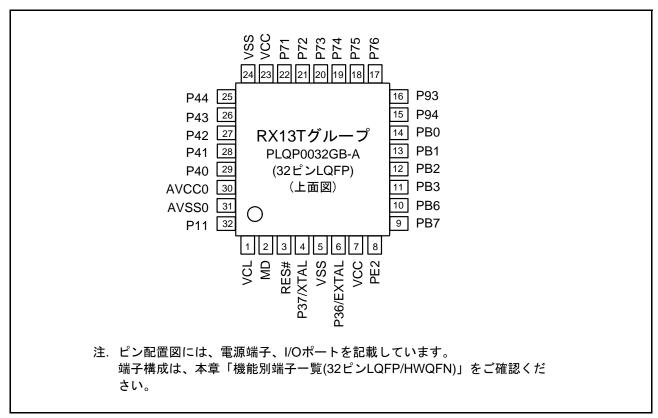

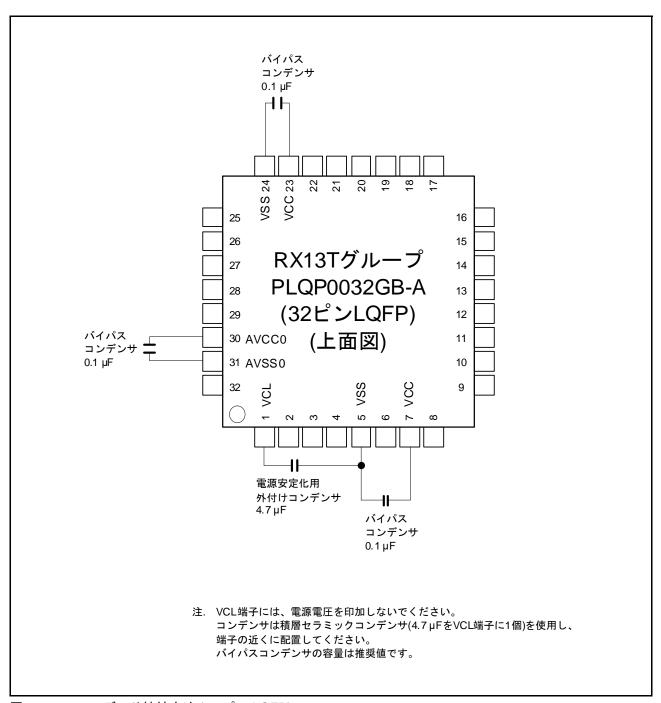

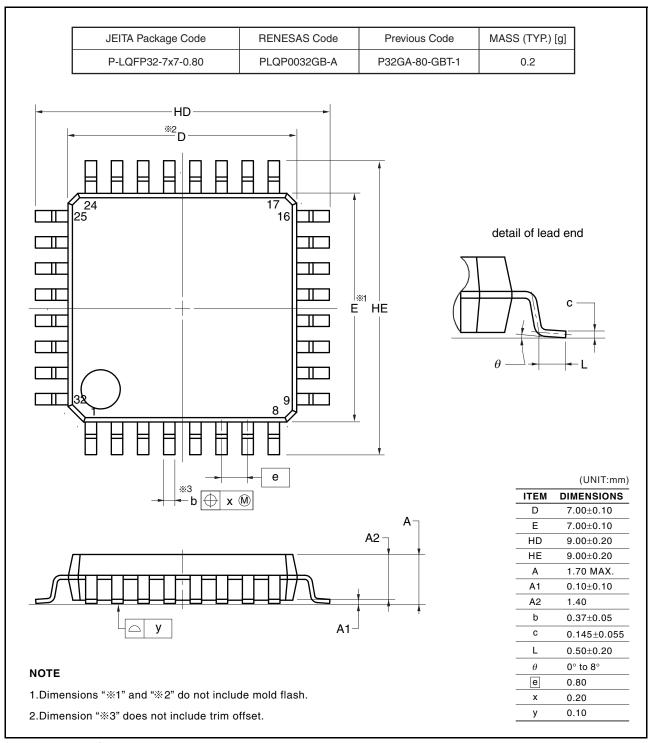

|    | 1.5.3  | 32 ピン LQFP                               | 45 |

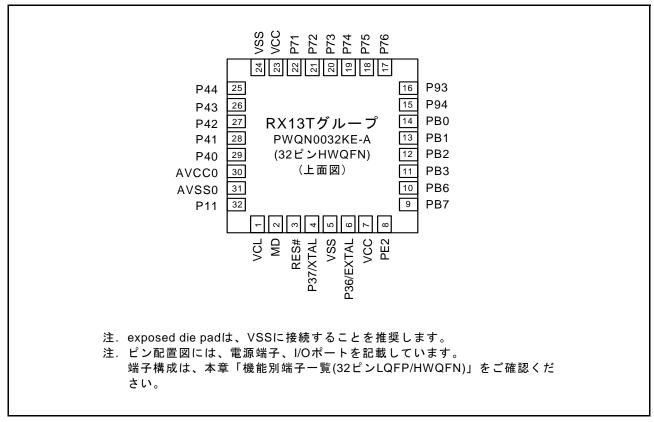

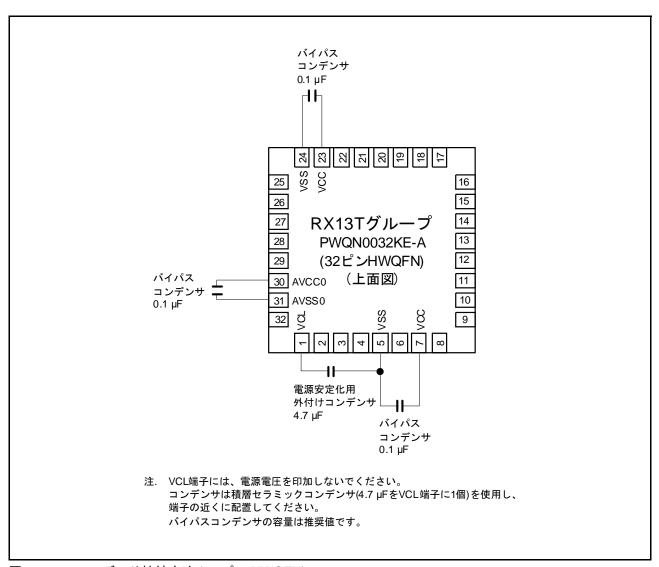

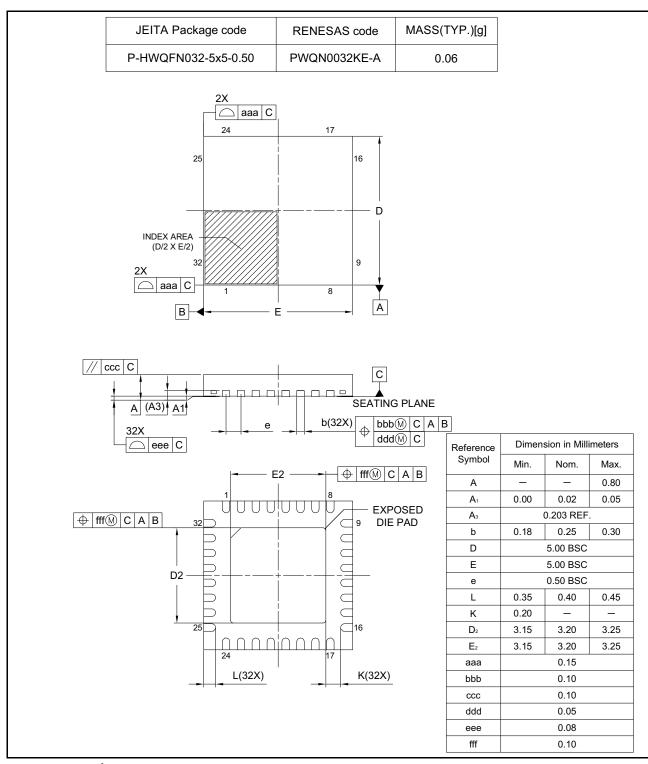

|    | 1.5.4  | 32 ピン HWQFN                              | 46 |

|    | 1.6 機  | 能別端子一覧                                   | 47 |

|    | 1.6.1  | 48 ピン LFQFP/HWQFN                        | 47 |

|    | 1.6.2  | 32 ピン LQFP/HWQFN                         | 49 |

| 2. | CPU    |                                          | 50 |

|    | 2.1 特  | 長                                        | 50 |

|    | 2.2 CI | PU レジスタセット                               | 51 |

|    | 2.2.1  | 汎用レジスタ (R0 $\sim$ R15)                   | 52 |

|    | 2.2.2  | 制御レジスタ                                   | 52 |

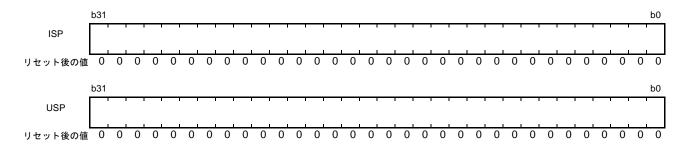

|    | 2.2.2  | .1 割り込みスタックポインタ (ISP)/ ユーザスタックポインタ (USP) | 53 |

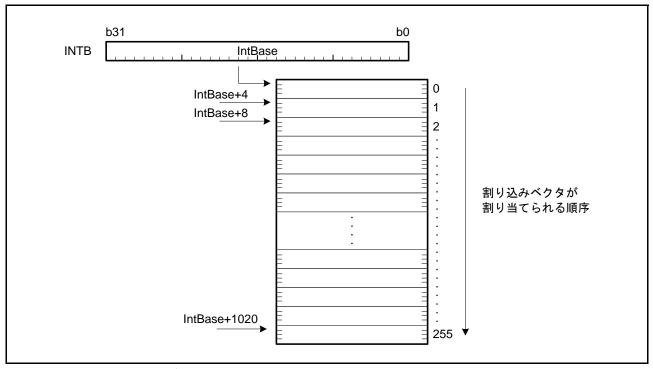

|    | 2.2.2  | .2 割り込みテーブルレジスタ (INTB)                   | 53 |

|    | 2.2.2  |                                          |    |

|    | 2.2.2  | .4 プロセッサステータスワード (PSW)                   | 54 |

|    | 2.2.2  |                                          |    |

|    | 2.2.2  |                                          |    |

|    | 2.2.2  | ,                                        |    |

|    | 2.2.2  |                                          |    |

|    | 2.2.3  | <b>DSP</b> 機能命令関連レジスタ                    |    |

|    | 2.2.3  |                                          |    |

|    |        | ロセッサモード                                  |    |

|    | 2.3.1  | スーパバイザモード                                |    |

|    | 2.3.2  | ユーザモード                                   |    |

|    | 2.3.3  | 特権命令                                     |    |

|    | 2.3.4  | プロセッサモード間の移行                             |    |

|    |        | ータタイプ                                    |    |

|    |        | ンディアン                                    |    |

|    | 2.5.1  | エンディアンの設定                                |    |

|    | 2.5.2  | I/O レジスタアクセス                             |    |

|    | 2.5.3  | I/O レジスタアクセスの注意事項                        |    |

|    | 2.5.4  | データ配置                                    | 65 |

|    | 2.5.4.1 | レジスタのデータ配置                              | 65  |

|----|---------|-----------------------------------------|-----|

|    | 2.5.4.2 | メモリ上のデータ配置                              | 66  |

|    | 2.5.5   | 命令コード配置の注意事項                            | 66  |

|    | 2.6 ベク  | タテーブル                                   | 67  |

|    | 2.6.1   | 固定ベクタテーブル                               | 67  |

|    | 2.6.2   | 可変ベクタテーブル                               | 68  |

|    | 2.7 命令  | 動作                                      | 69  |

|    | 2.7.1   | RMPA 命令、ストリング操作命令のデータプリフェッチ             | 69  |

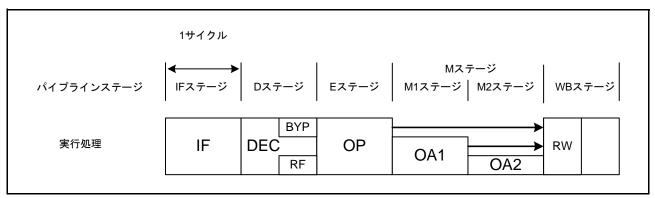

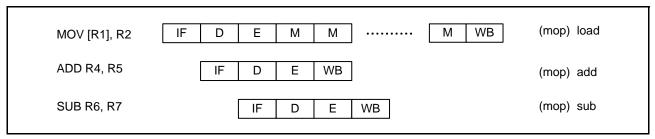

|    | 2.8 パイ  | プライン                                    | 69  |

|    | 2.8.1   | 概要                                      | 69  |

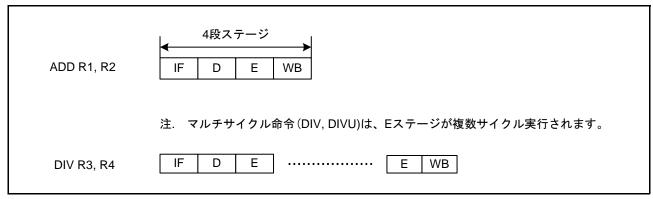

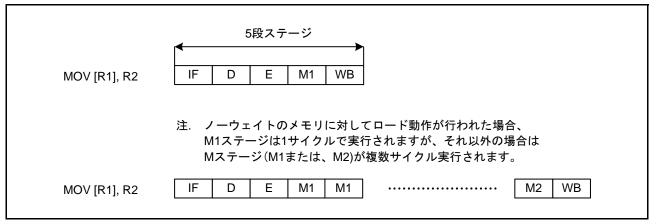

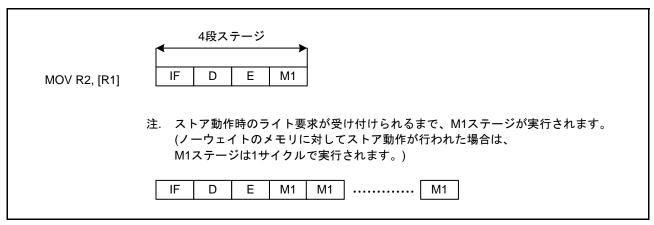

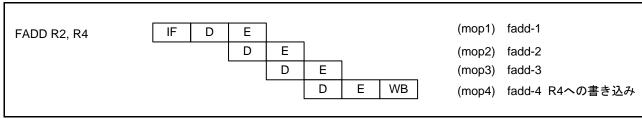

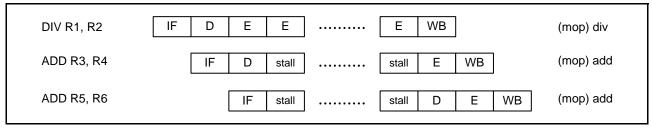

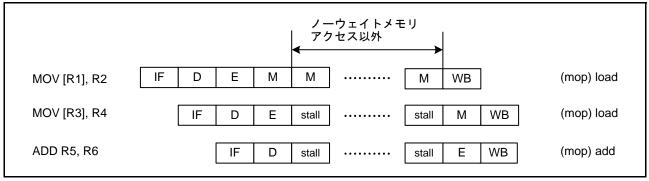

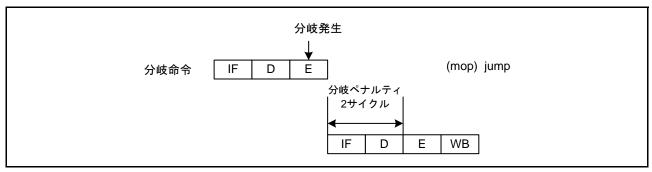

|    | 2.8.2   | 命令とパイプライン処理                             |     |

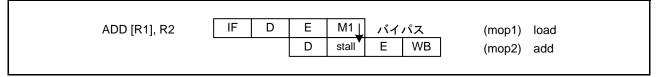

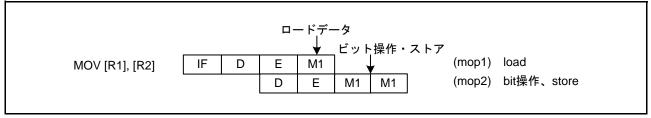

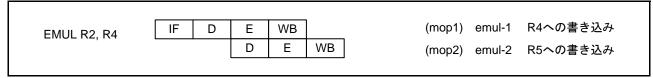

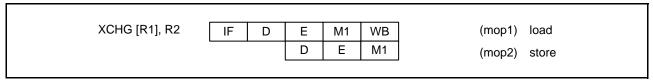

|    | 2.8.2.1 | , , , , , , , , , , , , , , , , , , , , |     |

|    | 2.8.2.2 | 複数のマイクロオペレーションに変換される命令とパイプライン処理         | 73  |

|    | 2.8.2.3 |                                         |     |

|    | 2.8.3   | 命令処理時間の計算方法                             | 78  |

|    | 2.8.4   | 割り込み応答サイクル数                             | 79  |

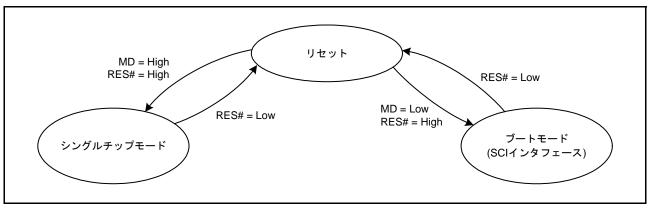

| 3. | 動作モート   | 9                                       | 80  |

|    | 3.1 動作  | モードの種類と選択                               | 80  |

|    | 3.2 レジ  | シスタの説明                                  | 81  |

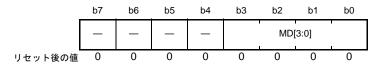

|    | 3.2.1   | モードモニタレジスタ (MDMONR)                     | 81  |

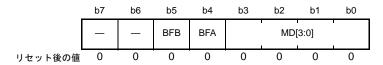

|    | 3.2.2   | システムコントロールレジスタ 1 (SYSCR1)               |     |

|    | 3.3 動作  | モードの説明                                  |     |

|    | 3.3.1   | シングルチップモード                              |     |

|    | 3.3.2   | ブートモード                                  |     |

|    | 3.3.2.1 |                                         |     |

|    |         | モード遷移                                   |     |

|    | 3.4.1   | モード設定端子による動作モード遷移                       | 83  |

| 4. | アドレス空   | 2間                                      | 84  |

|    | 4.1 アド  | `レス空間                                   | 84  |

| 5. |         | タ                                       |     |

|    | 5.1 I/O | レジスタアドレス一覧(アドレス順)                       | 88  |

| 6. | リセット.   |                                         | 99  |

|    | 6.1 概要  | ·                                       | 99  |

|    | 6.2 レジ  | スタの説明                                   | 101 |

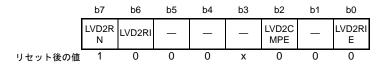

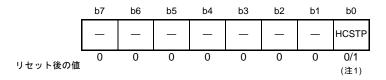

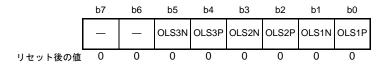

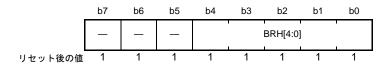

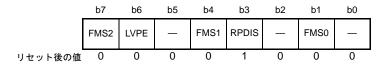

|    | 6.2.1   | リセットステータスレジスタ 0 (RSTSR0)                | 101 |

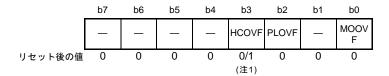

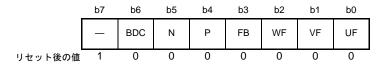

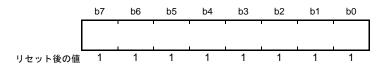

|    | 6.2.2   | リセットステータスレジスタ 1 (RSTSR1)                | 102 |

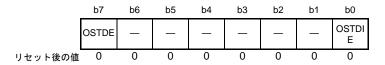

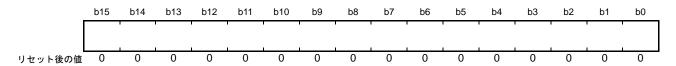

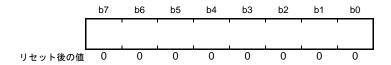

|    | 6.2.3   | リセットステータスレジスタ 2 (RSTSR2)                | 103 |

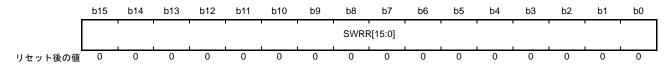

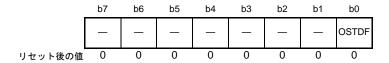

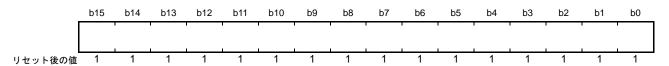

|    | 6.2.4   | ソフトウェアリセットレジスタ (SWRR)                   | 104 |

|    | 6.3 動作  | 説明                                      | 105 |

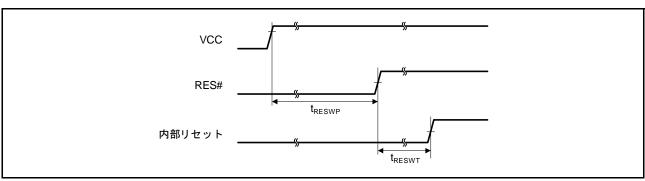

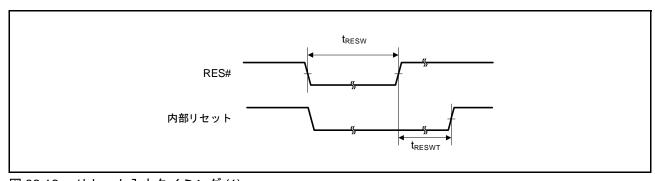

|    | 6.3.1   | RES# 端子リセット                             | 105 |

|    |         |                                         |     |

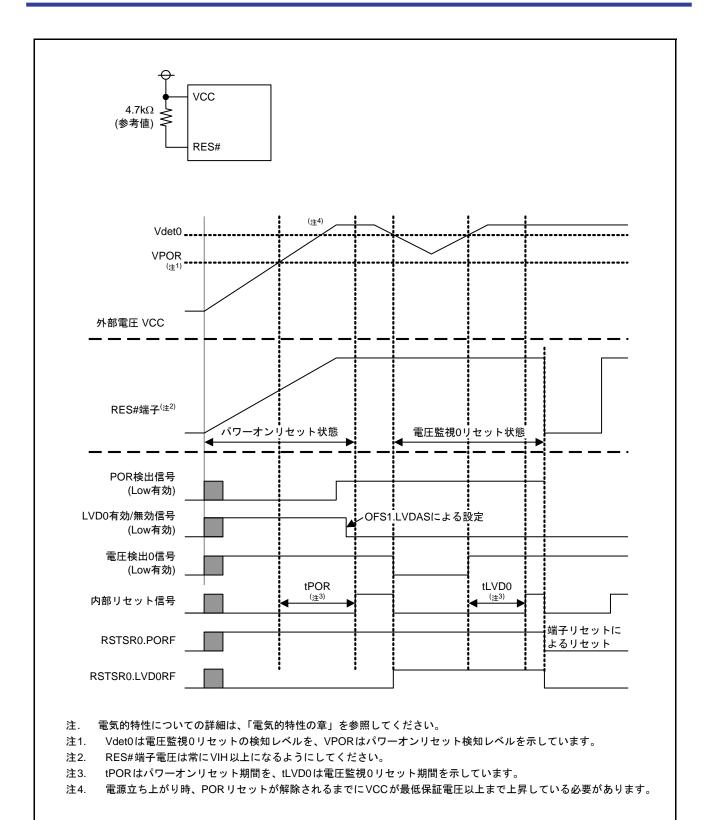

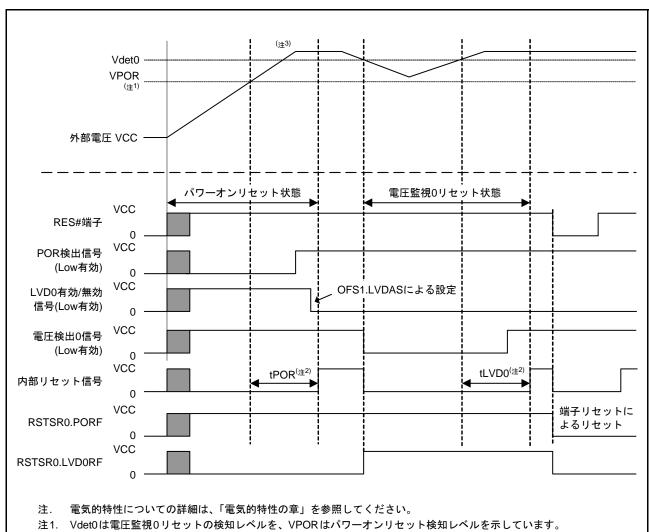

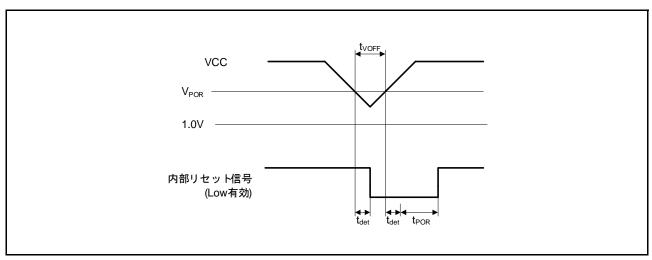

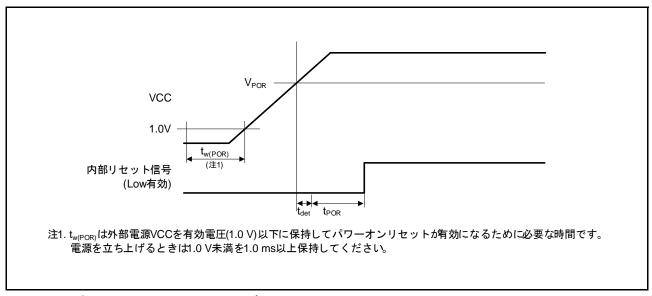

|    | 6.3.2 | パワーオンリセット、電圧監視 0 リセット         | 105 |

|----|-------|-------------------------------|-----|

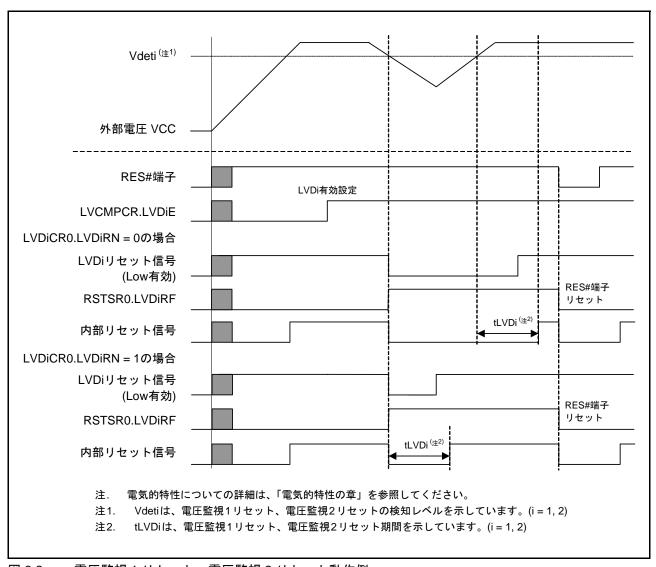

|    | 6.3.3 | 電圧監視1リセット、電圧監視2リセット           | 107 |

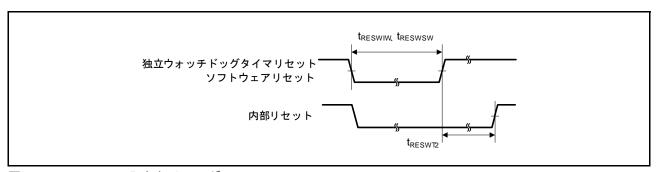

|    | 6.3.4 | 独立ウォッチドッグタイマリセット              | 109 |

|    | 6.3.5 | ソフトウェアリセット                    | 109 |

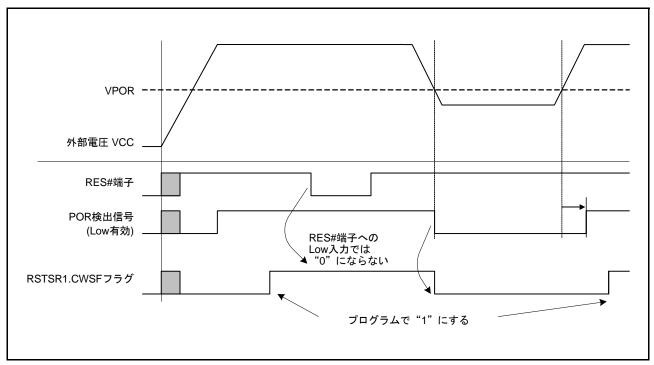

|    | 6.3.6 | コールドスタート / ウォームスタート判定機能       | 110 |

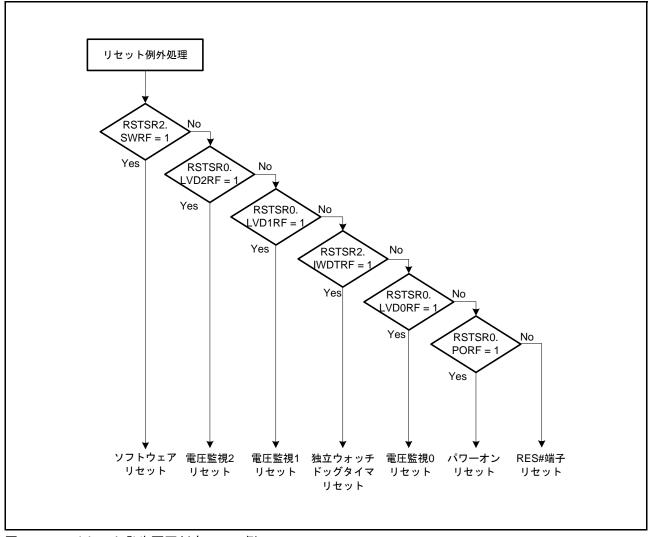

|    | 6.3.7 | リセット発生要因の判定                   | 111 |

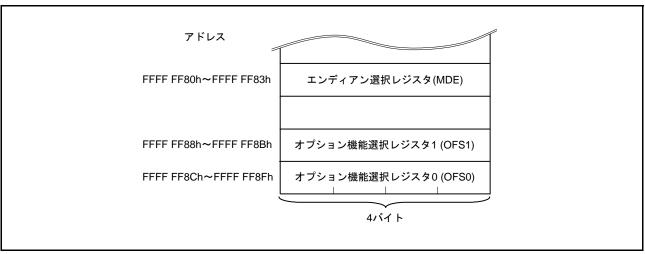

| 7. | オプシ   | vョン設定メモリ (OFSM)               | 112 |

|    | 7.1   | 概要                            | 112 |

|    | 7.2   | レジスタの説明                       | 113 |

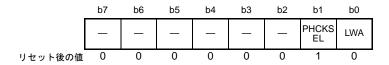

|    | 7.2.1 | オプション機能選択レジスタ 0 (OFS0)        | 113 |

|    | 7.2.2 | オプション機能選択レジスタ 1 (OFS1)        | 115 |

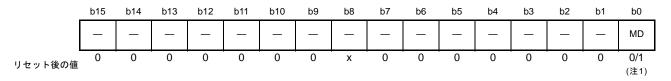

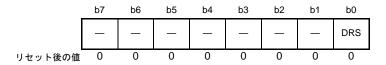

|    | 7.2.3 | エンディアン選択レジスタ (MDE)            | 116 |

|    | 7.3   | 使用上の注意事項                      | 117 |

|    | 7.3.1 | オプション設定メモリの設定例                | 117 |

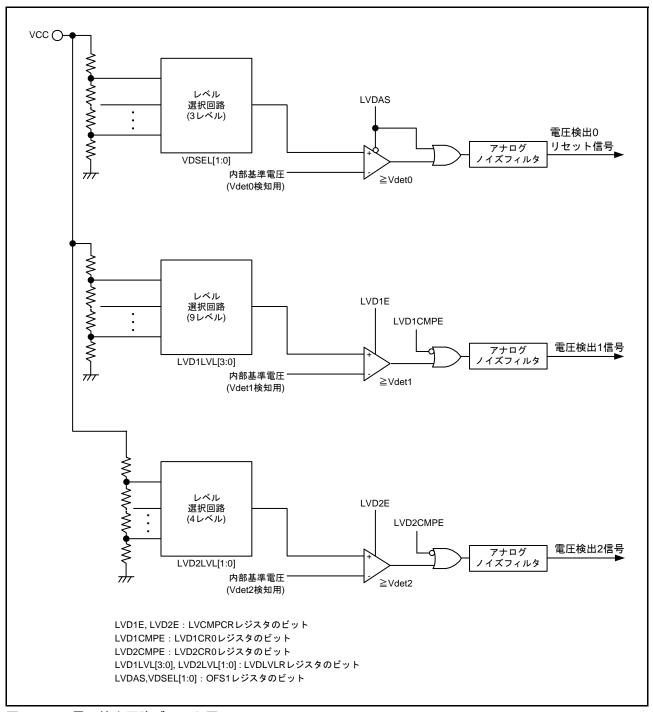

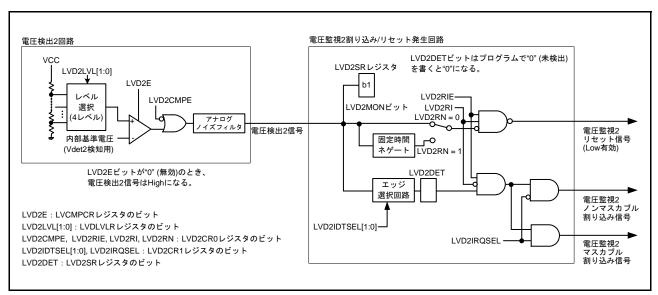

| 8. | 電圧板   | 食出回路 (LVDAb)                  | 118 |

|    | 8.1   | 概要                            | 118 |

|    | 8.2   | レジスタの説明                       | 121 |

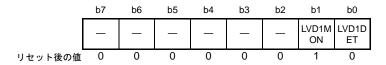

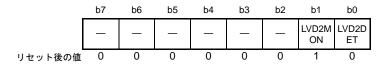

|    | 8.2.1 | 電圧監視 1 回路制御レジスタ 1 (LVD1CR1)   | 121 |

|    | 8.2.2 | 電圧監視 1 回路ステータスレジスタ (LVD1SR)   | 122 |

|    | 8.2.3 | 電圧監視 2 回路制御レジスタ 1 (LVD2CR1)   | 123 |

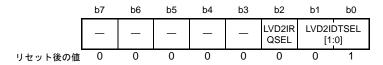

|    | 8.2.4 | 電圧監視 2 回路ステータスレジスタ (LVD2SR)   | 124 |

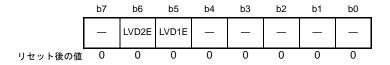

|    | 8.2.5 | 電圧監視回路制御レジスタ (LVCMPCR)        | 125 |

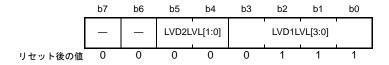

|    | 8.2.6 | 電圧検出レベル選択レジスタ (LVDLVLR)       | 126 |

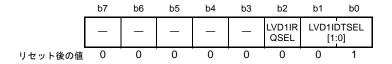

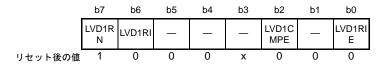

|    | 8.2.7 | 電圧監視 1 回路制御レジスタ 0 (LVD1CR0)   | 127 |

|    | 8.2.8 | 電圧監視 2 回路制御レジスタ 0 (LVD2CR0)   | 128 |

|    | 8.3   | VCC 入力電圧のモニタ                  | 129 |

|    | 8.3.1 | Vdet0 のモニタ                    | 129 |

|    | 8.3.2 | Vdet1 のモニタ                    | 129 |

|    | 8.3.3 | Vdet2 のモニタ                    | 129 |

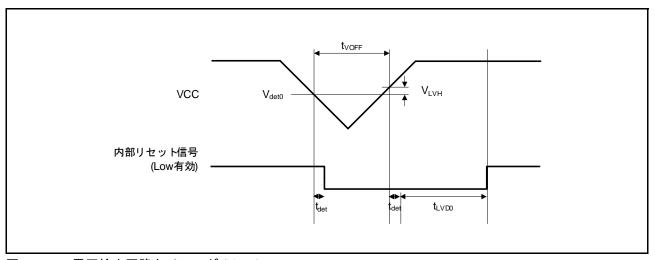

|    | 8.4   | 電圧監視 0 リセット                   | 130 |

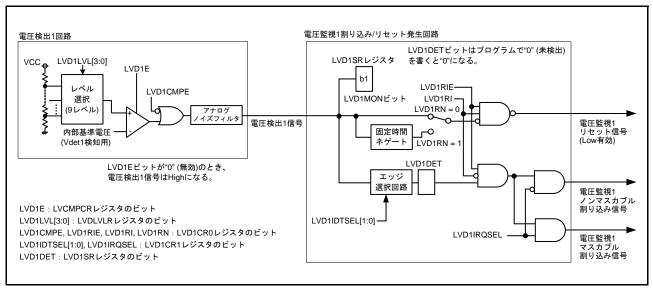

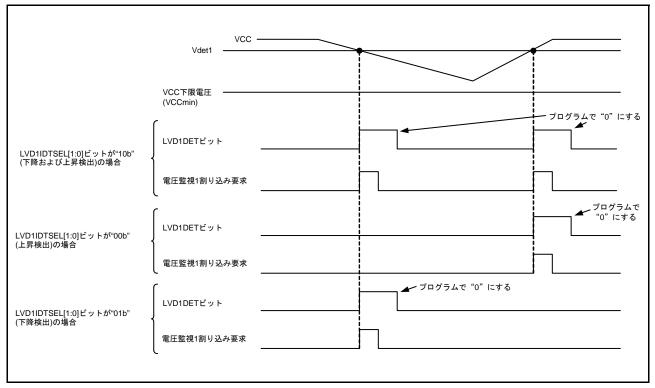

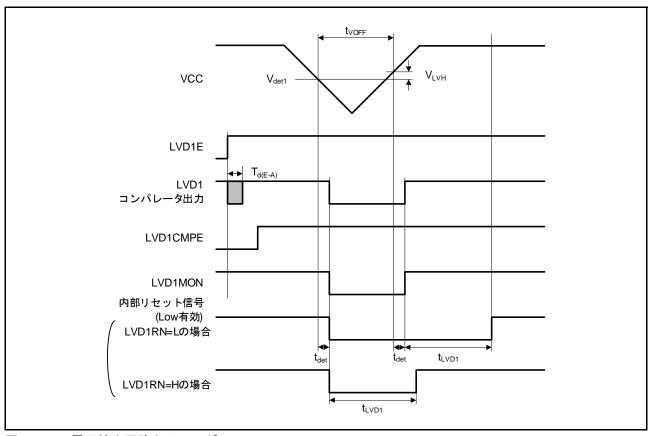

|    | 8.5   | 電圧監視1割り込み、電圧監視1リセット           | 131 |

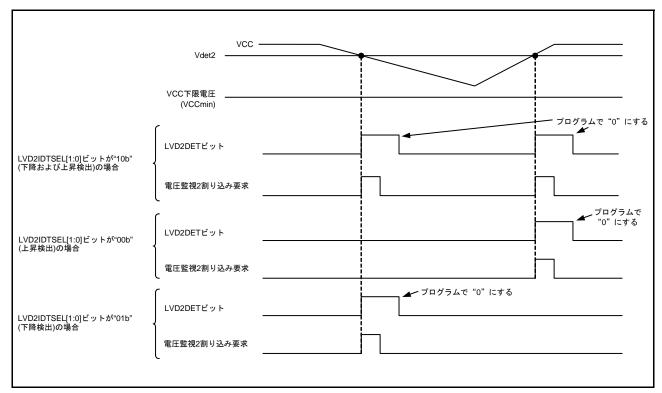

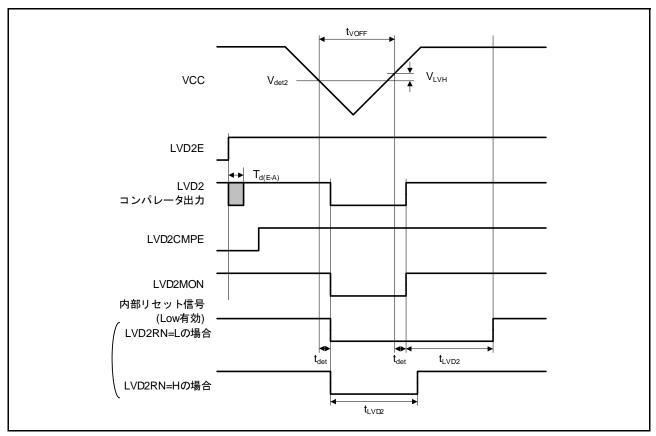

|    | 8.6   | 電圧監視2割り込み、電圧監視2リセット           | 133 |

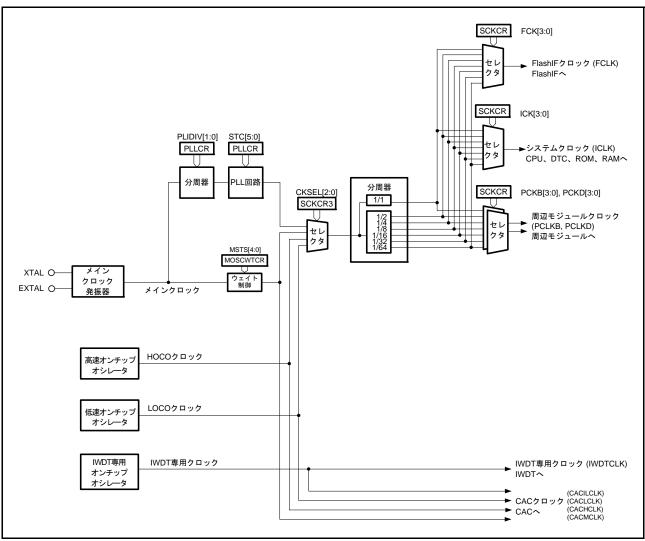

| 9. | クロッ   | ック発生回路                        | 135 |

|    | 9.1   | 概要                            | 135 |

|    | 9.2   | レジスタの説明                       |     |

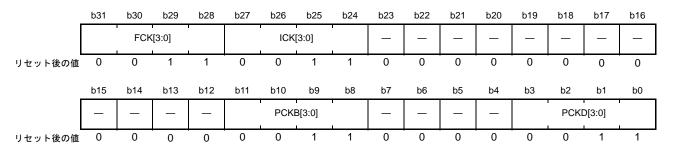

|    | 9.2.1 | システムクロックコントロールレジスタ (SCKCR)    |     |

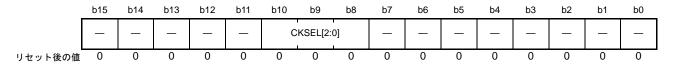

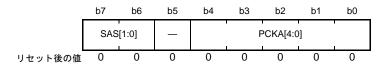

|    | 9.2.2 | システムクロックコントロールレジスタ 3 (SCKCR3) | 139 |

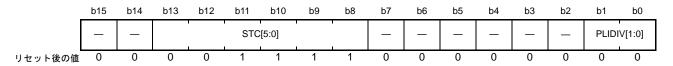

|    | 9.2.3 | PLL コントロールレジスタ (PLLCR)        |     |

|    | 9.2.4 | PLL コントロールレジスタ 2 (PLLCR2)     |     |

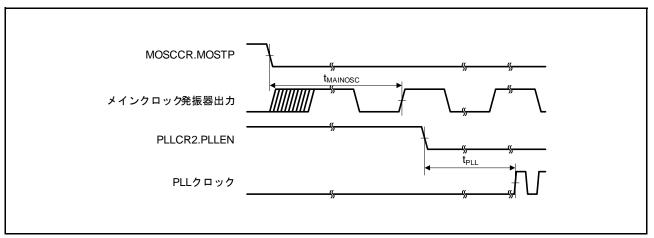

|    | 9.2.5 | メインクロック発振器コントロールレジスタ (MOSCCR) | 142 |

|    | 9.2.6  | 低速オンチップオシレータコントロールレジスタ (LOCOCR)            | 143   |

|----|--------|--------------------------------------------|-------|

|    | 9.2.7  | IWDT 専用オンチップオシレータコントロールレジスタ (ILOCOCR)      | 144   |

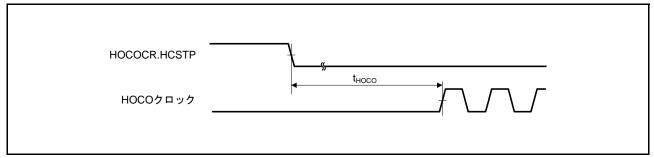

|    | 9.2.8  | 高速オンチップオシレータコントロールレジスタ (HOCOCR)            | 145   |

|    | 9.2.9  | 発振安定フラグレジスタ (OSCOVFSR)                     | 146   |

|    | 9.2.10 | 発振停止検出コントロールレジスタ (OSTDCR)                  | 148   |

|    | 9.2.11 | 発振停止検出ステータスレジスタ (OSTDSR)                   | 149   |

|    | 9.2.12 | メインクロック発振器ウェイトコントロールレジスタ (MOSCWTCR)        | 150   |

|    | 9.2.13 | メインクロック発振器強制発振コントロールレジスタ (MOFCR)           | 151   |

|    | 9.2.14 | 低速オンチップオシレータトリミングレジスタ (LOCOTRR)            | 152   |

|    | 9.2.15 | IWDT 専用オンチップオシレータトリミングレジスタ (ILOCOTRR)      | 152   |

|    | 9.2.16 | 高速オンチップオシレータトリミングレジスタ n (HOCOTRRn) (n = 0) | 153   |

|    | 9.3    | メインクロック発振器                                 | 154   |

|    | 9.3.1  | 発振子を接続する方法                                 | 154   |

|    | 9.3.2  | 外部クロックを入力する方法                              | 155   |

|    | 9.3.3  | 外部クロック入力に関する注意事項                           | 155   |

|    | 9.4    | 発振停止検出機能                                   | 156   |

|    | 9.4.1  | 発振停止検出と検出後の動作                              | 156   |

|    | 9.4.2  | 発振停止検出割り込み                                 | 157   |

|    | 9.5    | PLL 回路                                     | 158   |

|    | 9.6    | 内部クロック                                     | 158   |

|    | 9.6.1  | システムクロック                                   | 158   |

|    | 9.6.2  | 周辺モジュールクロック                                | 158   |

|    | 9.6.3  | FlashIF クロック                               | 158   |

|    | 9.6.4  | CAC クロック                                   | 158   |

|    | 9.6.5  | IWDT 専用クロック                                | 159   |

|    | 9.7    | 使用上の注意事項                                   | 160   |

|    | 9.7.1  | クロック発生回路に関する注意事項                           | 160   |

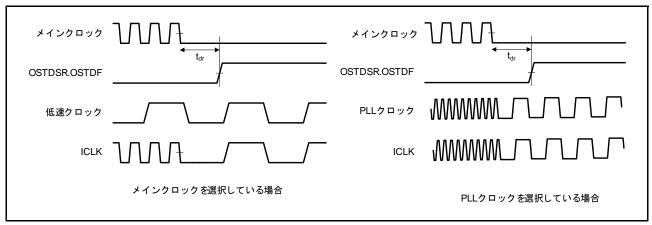

|    | 9.7.2  | SCKCR3 レジスタ書き換え時の注意事項                      | 160   |

|    | 9.7.3  | 発振子に関する注意事項                                | 160   |

|    | 9.7.4  | ボード設計上の注意                                  | 160   |

|    | 9.7.5  | 発振子接続端子に関する注意事項                            | 162   |

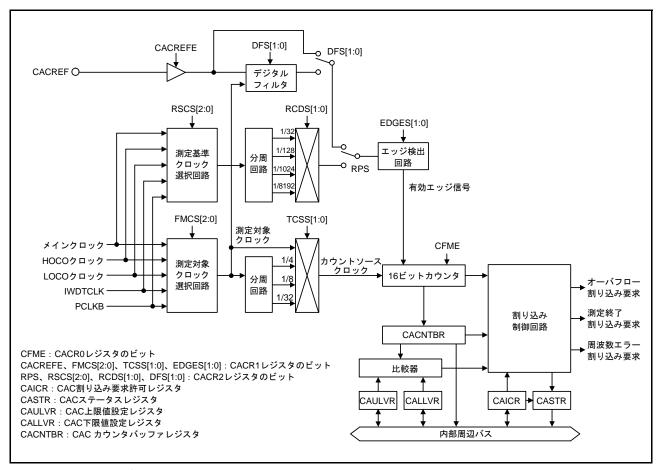

| 0. | クロぃ    | ・<br>ク周波数精度測定回路 (CAC)                      | 163   |

| ٠. | 10.1   | 概要                                         |       |

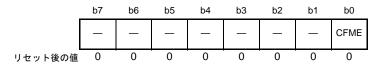

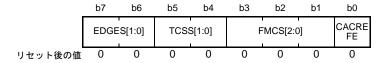

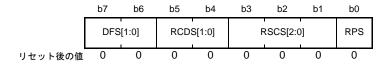

|    | 10.2   | レジスタの説明                                    |       |

|    | 10.2.1 |                                            |       |

|    | 10.2.2 |                                            |       |

|    | 10.2.3 |                                            |       |

|    | 10.2.4 |                                            |       |

|    | 10.2.5 |                                            |       |

|    | 10.2.6 |                                            |       |

|    | 10.2.0 |                                            | 1 / 0 |

|     | 10.2.7 | CAC 下限値設定レジスタ (CALLVR)                | 170 |

|-----|--------|---------------------------------------|-----|

|     | 10.2.8 | CAC カウンタバッファレジスタ (CACNTBR)            | 170 |

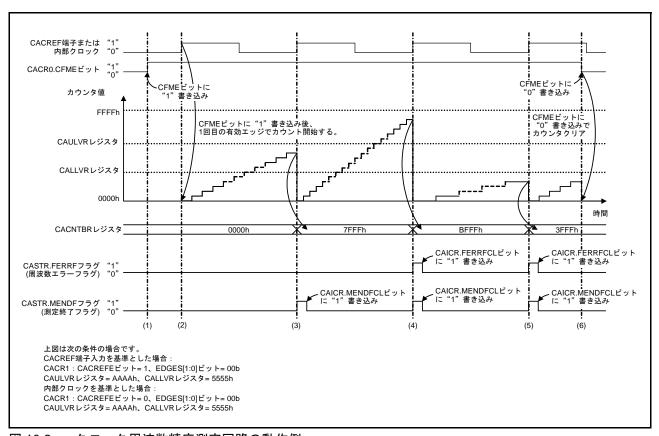

|     | 10.3 動 | 作説明                                   | 171 |

|     | 10.3.1 | クロック周波数測定                             | 171 |

|     | 10.3.2 | CACREF 端子のデジタルフィルタ機能                  | 172 |

|     | 10.4 害 | り込み要求                                 | 172 |

|     | 10.5 使 | 三用上の注意事項                              | 173 |

|     | 10.5.1 | モジュールストップ機能の設定                        | 173 |

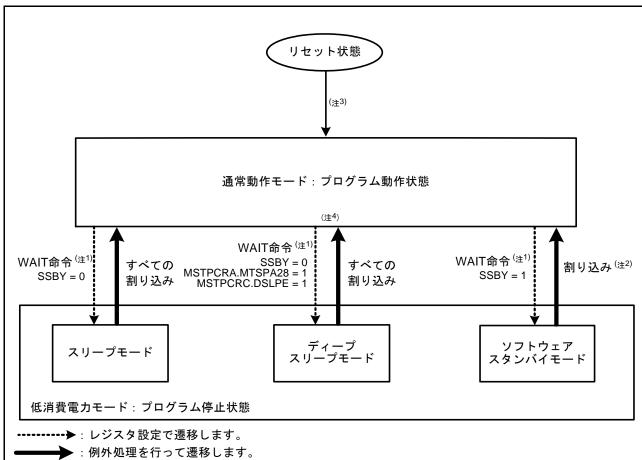

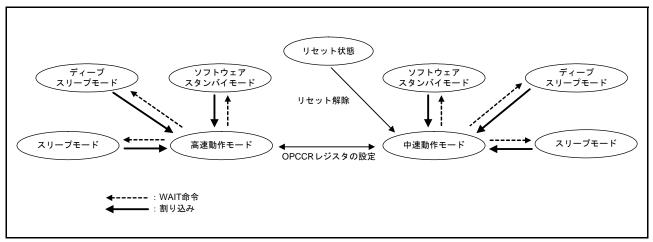

| 11. | 消費電力   | ]低減機能                                 | 174 |

|     | 11.1 櫻 | 要                                     | 174 |

|     | 11.2 レ | ジスタの説明                                | 178 |

|     | 11.2.1 | スタンバイコントロールレジスタ (SBYCR)               | 178 |

|     | 11.2.2 | モジュールストップコントロールレジスタ A (MSTPCRA)       | 179 |

|     | 11.2.3 | モジュールストップコントロールレジスタ B (MSTPCRB)       | 180 |

|     | 11.2.4 | モジュールストップコントロールレジスタ C (MSTPCRC)       | 181 |

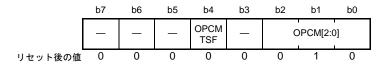

|     | 11.2.5 | 動作電力コントロールレジスタ (OPCCR)                | 182 |

|     | 11.3 ク | ロックの切り替えによる消費電力の低減                    | 184 |

|     | 11.4 ₹ | ジュールストップ機能                            | 184 |

|     | 11.5 動 | 作電力低減機能                               | 185 |

|     | 11.5.1 | 動作電力制御モード設定方法                         | 185 |

|     | 11.6 但 | 消費電力状態                                |     |

|     | 11.6.1 | スリープモード                               |     |

|     | 11.6   | 1.1 スリープモードへの移行                       | 186 |

|     | 11.6   | 1.2 スリープモードの解除                        |     |

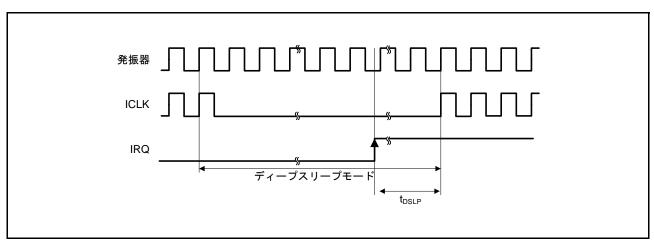

|     | 11.6.2 | ディープスリープモード                           |     |

|     | 11.6   | · · · · · · · · · · · · · · · · · · · |     |

|     | 11.6   | / / / / / / / / / / / / / / / / / /   |     |

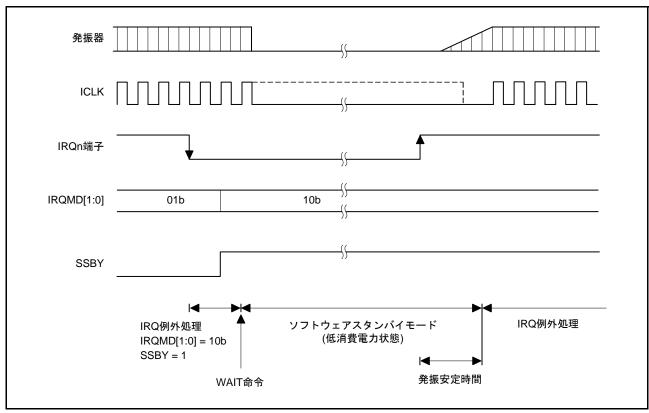

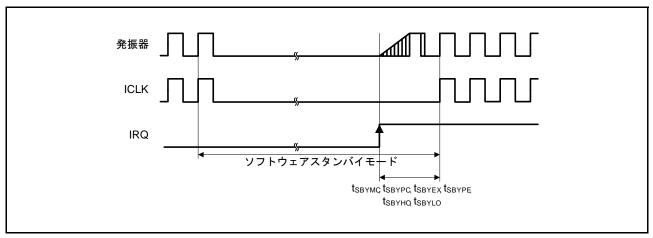

|     | 11.6.3 | ソフトウェアスタンバイモード                        |     |

|     | 11.6   |                                       |     |

|     | 11.6   |                                       |     |

|     | 11.6   | 3.3 ソフトウェアスタンバイモードの応用例                | 192 |

|     | 11.7 使 | [用上の注意事項                              |     |

|     | 11.7.1 | I/O ポートの状態                            |     |

|     | 11.7.2 | DTC のモジュールストップ                        |     |

|     | 11.7.3 | 内蔵周辺モジュールの割り込み                        |     |

|     | 11.7.4 | MSTPCRA、MSTPCRB、MSTPCRC レジスタの書き込み     |     |

|     | 11.7.5 | <b>WAIT</b> 命令の実行タイミング                |     |

|     | 11.7.6 | スリープモード中の DTC によるレジスタの書き換えについて        |     |

| 12. |        | ワライトプロテクション機能                         |     |

|     | 12.1 V | ジスタの説明                                | 195 |

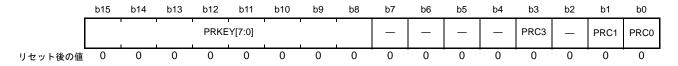

|     | 12.1.1  | プロテクトレジスタ (PRCR)                           | 195 |

|-----|---------|--------------------------------------------|-----|

| 13. | 例外処     | 理                                          | 196 |

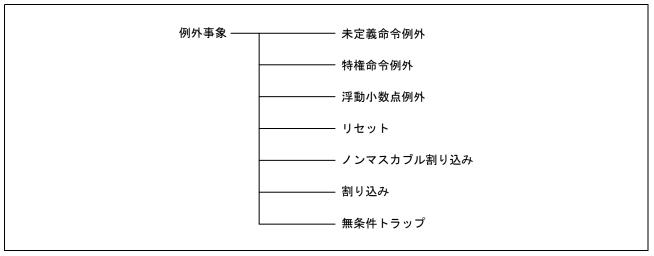

| 1   | 13.1    | 列外事象                                       | 196 |

|     | 13.1.1  | 未定義命令例外                                    | 197 |

|     | 13.1.2  | 特権命令例外                                     | 197 |

|     | 13.1.3  | 浮動小数点例外                                    | 197 |

|     | 13.1.4  | リセット                                       | 197 |

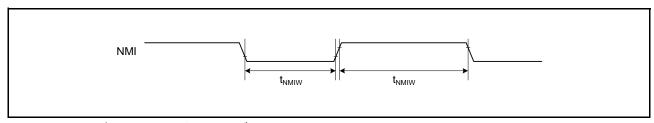

|     | 13.1.5  | ノンマスカブル割り込み                                | 197 |

|     | 13.1.6  | 割り込み                                       | 197 |

|     | 13.1.7  | 無条件トラップ                                    | 197 |

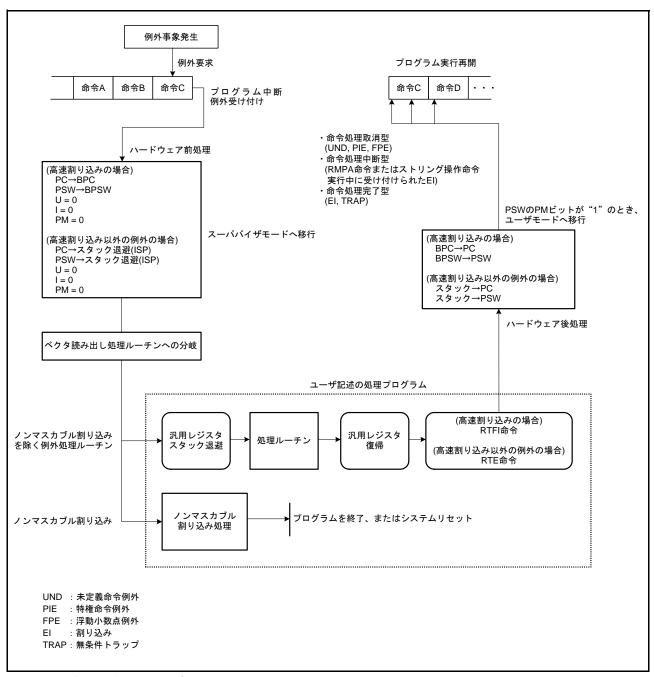

| 1   | 13.2    | 列外の処理手順                                    | 198 |

| 1   | 13.3    | 列外事象の受け付け                                  | 200 |

|     | 13.3.1  | 受け付けタイミングと退避される PC 値                       | 200 |

|     | 13.3.2  | ベクタと PC、PSW の退避場所                          | 200 |

| 1   | 13.4    | 列外の受け付け / 復帰時のハードウェア処理                     | 201 |

| 1   | 13.5    | ハードウェア前処理                                  | 202 |

|     | 13.5.1  | 未定義命令例外                                    | 202 |

|     | 13.5.2  | 特権命令例外                                     | 202 |

|     | 13.5.3  | 浮動小数点例外                                    | 202 |

|     | 13.5.4  | リセット                                       | 202 |

|     | 13.5.5  | ノンマスカブル割り込み                                | 203 |

|     | 13.5.6  | 割り込み                                       | 203 |

|     | 13.5.7  | 無条件トラップ                                    | 203 |

| 1   | 13.6    | 列外処理ルーチンからの復帰                              | 204 |

| 1   | 13.7    | 列外事象の優先順位                                  | 204 |

| 14. | 割り込     | みコントローラ (ICUb)                             | 205 |

| 1   | 14.1    | 既要                                         | 205 |

| 1   | 14.2    | レジスタの説明                                    | 207 |

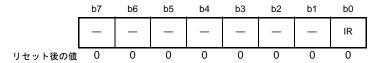

|     | 14.2.1  | 割り込み要求レジスタ n (IRn) (n = 割り込みベクタ番号 )        | 207 |

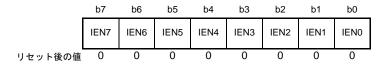

|     | 14.2.2  | 割り込み要求許可レジスタ m (IERm) (m = $02h\sim1$ Fh)  | 208 |

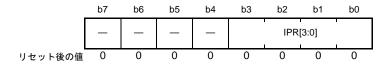

|     | 14.2.3  | 割り込み要因プライオリティレジスタ n (IPRn) (n = 割り込みベクタ番号) | 209 |

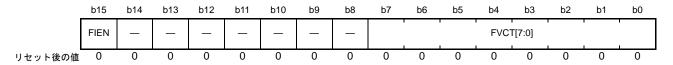

|     | 14.2.4  | 高速割り込み設定レジスタ (FIR)                         | 210 |

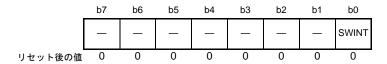

|     | 14.2.5  | ソフトウェア割り込み起動レジスタ (SWINTR)                  | 211 |

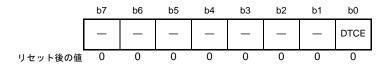

|     | 14.2.6  | DTC 転送要求許可レジスタ n (DTCERn) (n = 割り込みベクタ番号)  | 212 |

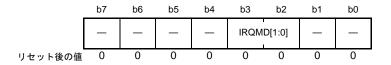

|     | 14.2.7  | IRQ コントロールレジスタ i (IRQCRi) (i = 0 $\sim$ 5) | 213 |

|     | 14.2.8  | IRQ 端子デジタルフィルタ許可レジスタ 0 (IRQFLTE0)          | 214 |

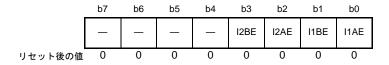

|     | 14.2.9  | IRQ 端子デジタルフィルタ設定レジスタ 0 (IRQFLTC0)          | 215 |

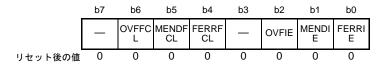

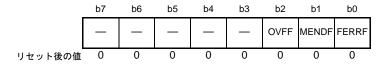

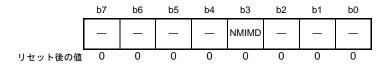

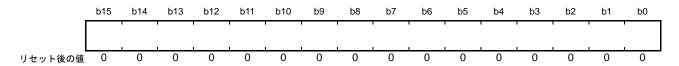

|     | 14.2.10 | ) ノンマスカブル割り込みステータスレジスタ (NMISR)             | 216 |

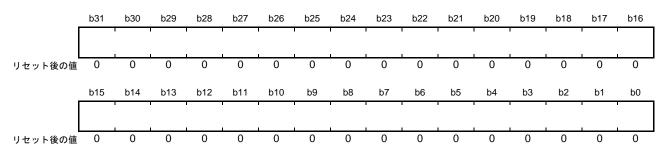

|     | 14.2.11 | ノンマスカブル割り込み許可レジスタ (NMIER)                  | 218 |

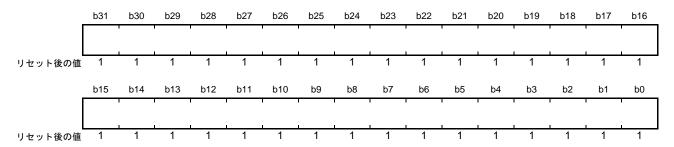

|     | 14.2.12 | 2 ノンマスカブル割り込みステータスクリアレジスタ (NMICLR)         | 219 |

|     | 14.2.13 | NMI 端子割り込みコントロールレジスタ (NMICR)   | 220 |

|-----|---------|--------------------------------|-----|

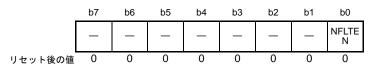

|     | 14.2.14 | NMI 端子デジタルフィルタ許可レジスタ (NMIFLTE) | 220 |

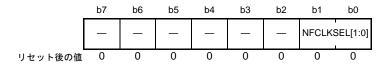

|     | 14.2.15 | NMI 端子デジタルフィルタ設定レジスタ (NMIFLTC) | 221 |

|     | 14.3 べク | カタテーブル                         | 222 |

|     | 14.3.1  | 割り込みのベクタテーブル                   | 222 |

|     | 14.3.2  | 高速割り込みのベクタテーブル                 | 228 |

|     | 14.3.3  | ノンマスカブル割り込みのベクタテーブル            | 228 |

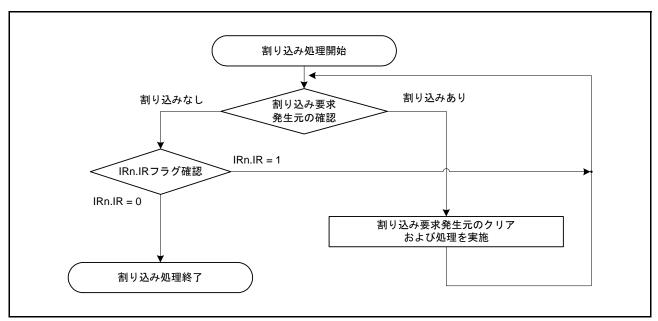

|     | 14.4 割り | ) 込みの動作説明                      | 229 |

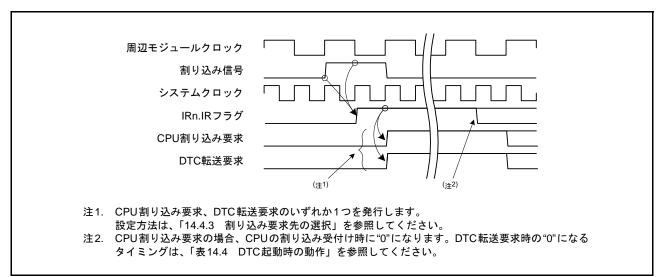

|     | 14.4.1  | 割り込み検出                         | 229 |

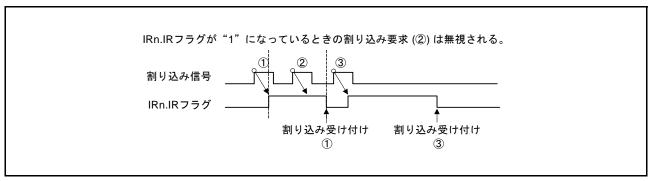

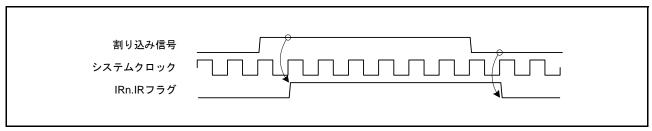

|     | 14.4.1  | .1 エッジ検出の割り込みステータスフラグ          | 229 |

|     | 14.4.1  | .2 レベル検出の割り込みステータスフラグ          | 231 |

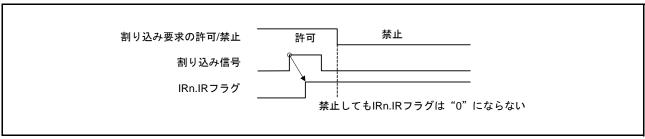

|     | 14.4.2  | 割り込み要求の許可 / 禁止                 | 232 |

|     | 14.4.3  | 割り込み要求先の選択                     | 233 |

|     | 14.4.4  | 優先順位の判定                        | 234 |

|     | 14.4.5  | 多重割り込み                         | 234 |

|     | 14.4.6  | 高速割り込み                         | 234 |

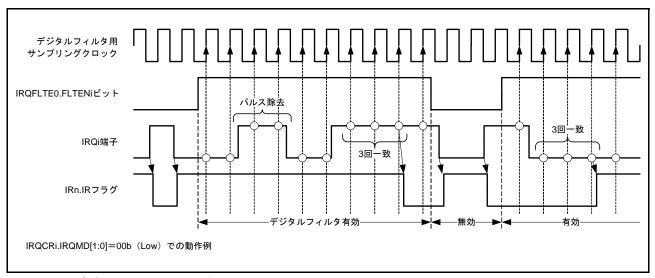

|     | 14.4.7  | デジタルフィルタ                       | 235 |

|     | 14.4.8  | 外部端子割り込み                       | 236 |

|     | 14.5    | /マスカブル割り込みの動作説明                | 237 |

|     | 14.6 低剂 | 肖費電力状態からの復帰                    | 238 |

|     | 14.6.1  | スリープモードおよびディープスリープモードからの復帰     | 238 |

|     | 14.6.2  | ソフトウェアスタンバイモードからの復帰            | 238 |

|     | 14.7 使月 | 用上の注意事項                        | 239 |

|     | 14.7.1  | ノンマスカブル割り込み使用時の WAIT 命令の注意事項   | 239 |

| 15. | バス      |                                | 240 |

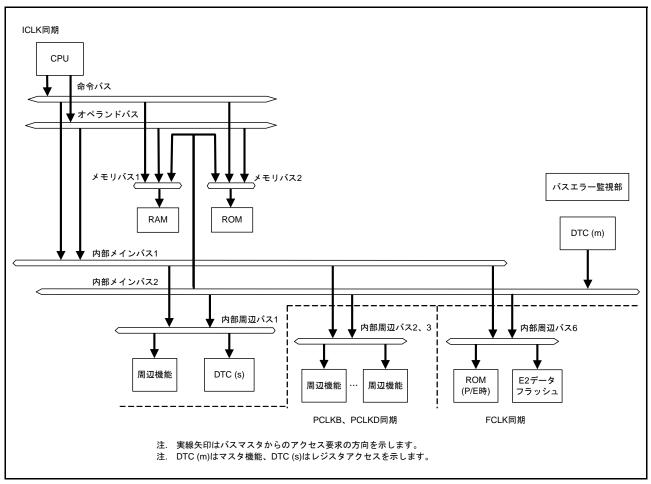

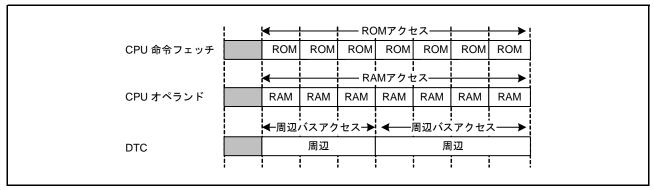

|     | 15.1 概要 | 要                              | 240 |

|     | 15.2 バン | スの説明                           | 242 |

|     | 15.2.1  | CPU バス                         | 242 |

|     | 15.2.2  | メモリバス                          | 242 |

|     | 15.2.3  | 内部メインバス                        | 242 |

|     | 15.2.4  | 内部周辺バス                         | 243 |

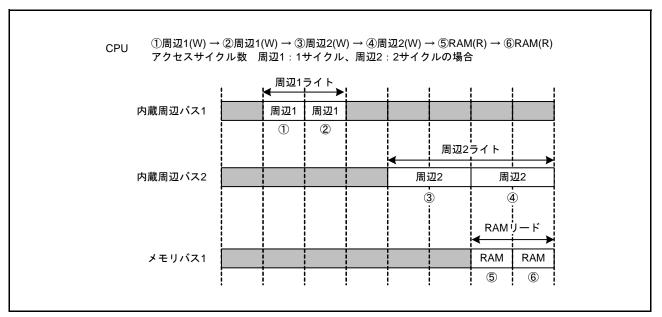

|     | 15.2.5  | ライトバッファ機能 (内部周辺バス)             | 244 |

|     | 15.2.6  | 並列動作                           | 245 |

|     | 15.2.7  | 制約事項                           | 245 |

|     | 15.3 レミ | ブスタの説明                         | 246 |

|     | 15.3.1  | バスエラーステータスクリアレジスタ (BERCLR)     | 246 |

|     | 15.3.2  | バスエラー監視許可レジスタ (BEREN)          | 246 |

|     | 15.3.3  | バスエラーステータスレジスタ 1 (BERSR1)      | 247 |

|     | 15.3.4  | バスエラーステータスレジスタ 2 (BERSR2)      | 247 |

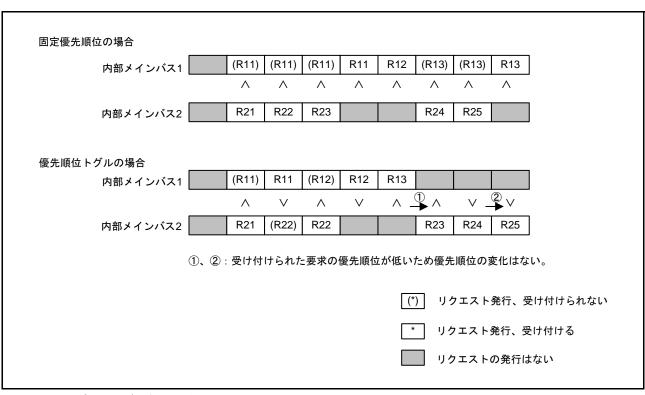

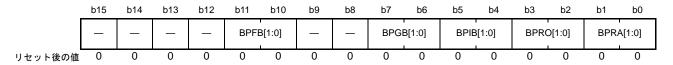

|     | 15.3.5  | バスプライオリティ制御レジスタ (BUSPRI)       | 248 |

|     |         |                                |     |

| 15.4    | ヾスエラー監視部                         | 250 |

|---------|----------------------------------|-----|

| 15.4.1  | バスエラーの種類                         | 250 |

| 15.4    | .1.1 不正アドレスアクセス                  | 250 |

| 15.4    | -1.2 タイムアウト                      | 250 |

| 15.4.2  | バスエラー発生時の動作                      | 250 |

| 15.4.3  | バスエラーの発生条件                       | 251 |

| 15.5 售  | 削り込み                             | 252 |

| 15.5.1  | 割り込み要因                           | 252 |

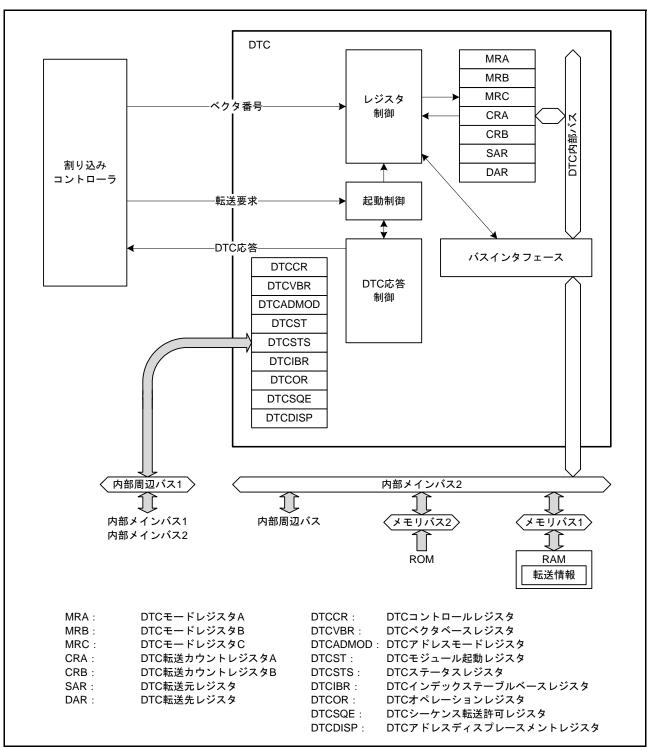

| 16. データ | トランスファコントローラ (DTCb)              | 253 |

| 16.1 相  | 既要                               | 253 |

| 16.2    | /ジスタの説明                          | 255 |

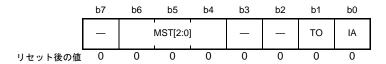

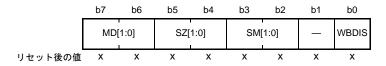

| 16.2.1  | DTC モードレジスタ A (MRA)              | 255 |

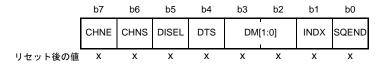

| 16.2.2  | DTC モードレジスタ B (MRB)              | 257 |

| 16.2.3  | DTC モードレジスタ C (MRC)              | 259 |

| 16.2.4  | DTC 転送元レジスタ (SAR)                | 260 |

| 16.2.5  | DTC 転送先レジスタ (DAR)                | 260 |

| 16.2.6  | DTC 転送カウントレジスタ A (CRA)           | 261 |

| 16.2.7  | DTC 転送カウントレジスタ B (CRB)           | 262 |

| 16.2.8  | DTC コントロールレジスタ (DTCCR)           | 262 |

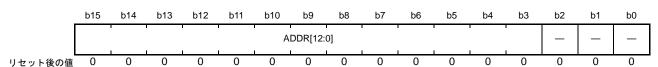

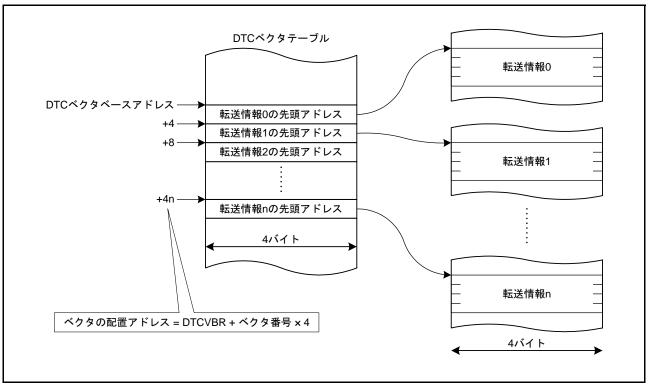

| 16.2.9  | DTC ベクタベースレジスタ (DTCVBR)          | 263 |

| 16.2.10 | DTC アドレスモードレジスタ (DTCADMOD)       | 263 |

| 16.2.11 | DTC モジュール起動レジスタ (DTCST)          | 264 |

| 16.2.12 | DTC ステータスレジスタ (DTCSTS)           | 265 |

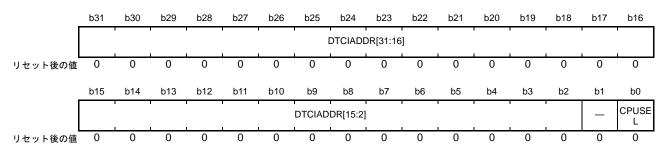

| 16.2.13 | DTC インデックステーブルベースレジスタ (DTCIBR)   | 266 |

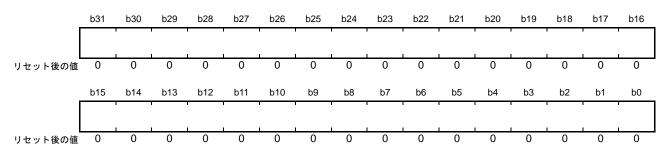

| 16.2.14 | DTC オペレーションレジスタ (DTCOR)          | 267 |

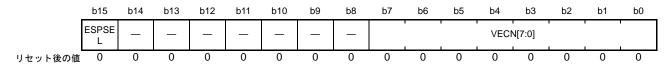

| 16.2.15 | DTC シーケンス転送許可レジスタ (DTCSQE)       | 268 |

| 16.2.16 | DTC アドレスディスプレースメントレジスタ (DTCDISP) | 268 |

| 16.3 走  | 💵 要因                             | 269 |

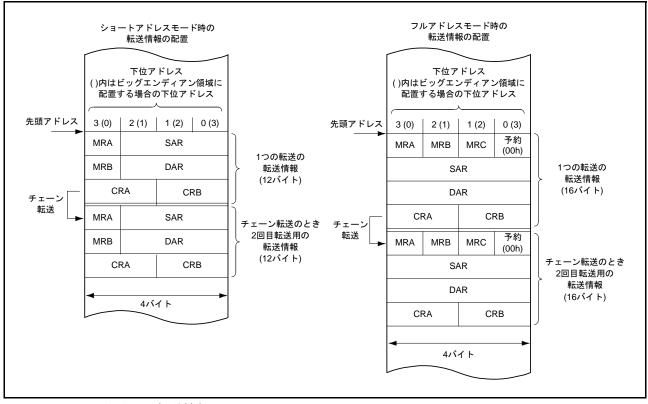

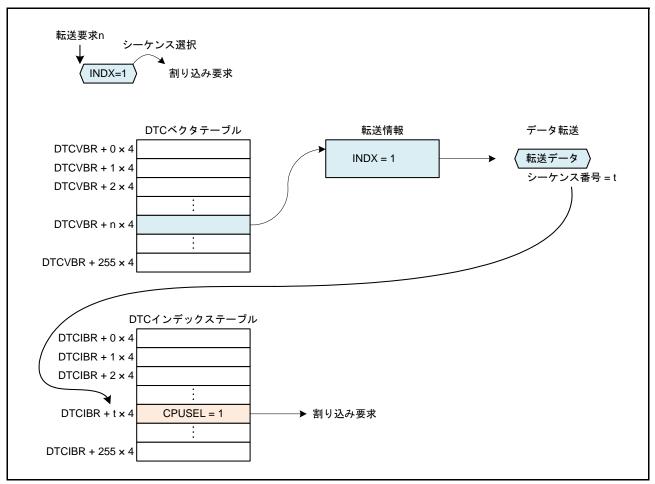

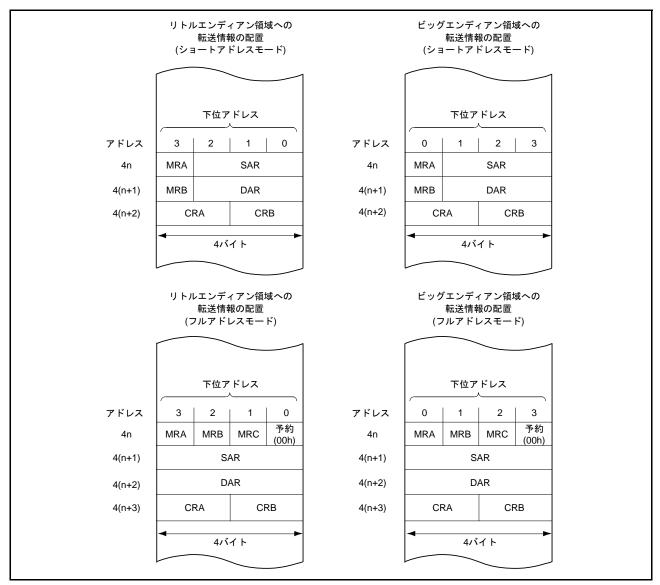

| 16.3.1  | 転送情報の配置と DTC ベクタテーブル             | 269 |

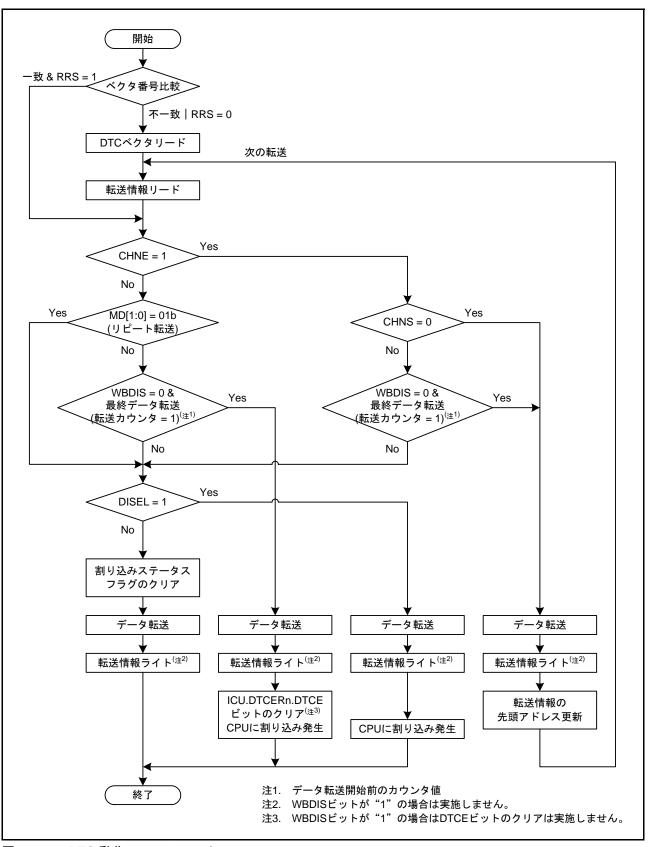

| 16.4 重  | 协作説明                             | 271 |

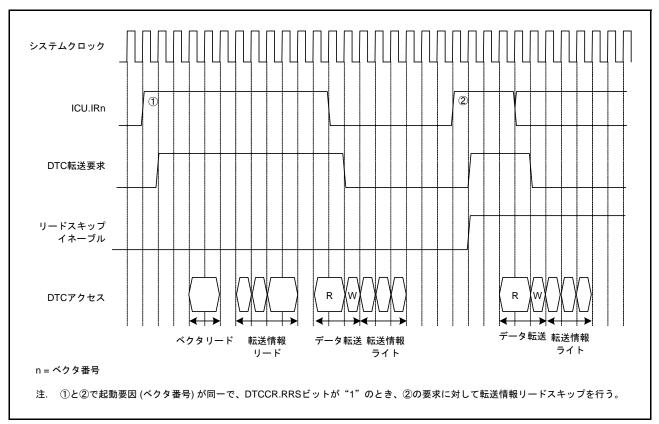

| 16.4.1  | 転送情報リードスキップ機能                    | 273 |

| 16.4.2  | 転送情報ライトバックスキップ機能                 |     |

| 16.4    |                                  |     |

| 16.4    |                                  |     |

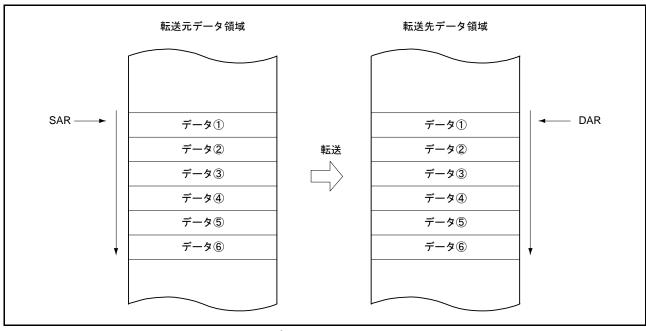

| 16.4.3  | ノーマル転送モード                        | 275 |

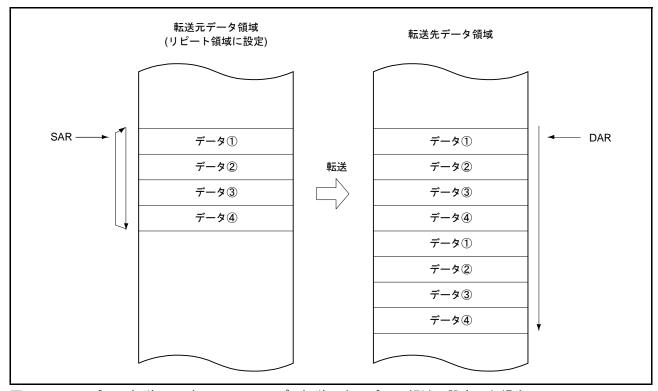

| 16.4.4  | リピート転送モード                        | 276 |

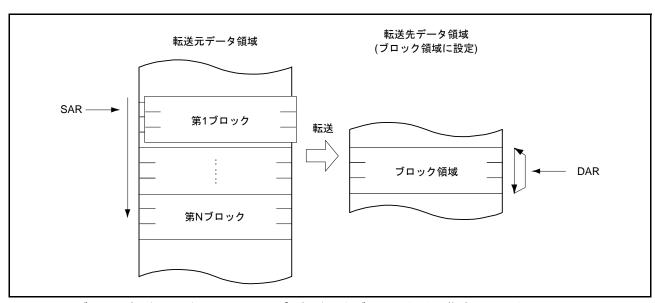

| 16.4.5  | ブロック転送モード                        | 277 |

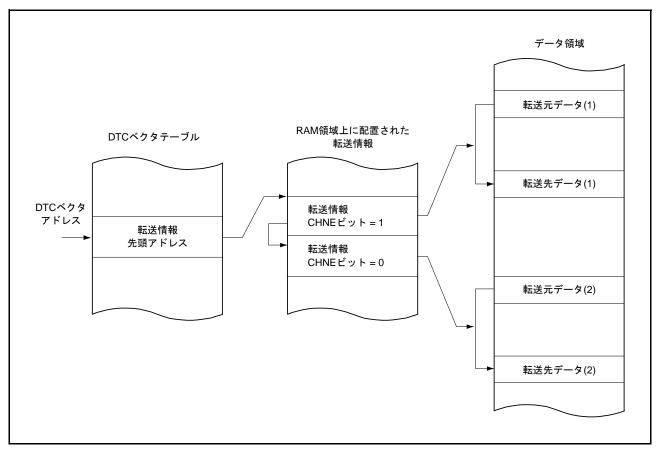

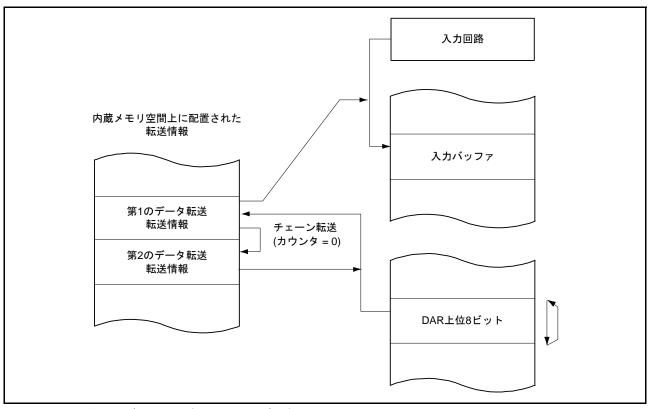

| 16.4.6  | チェーン転送                           | 278 |

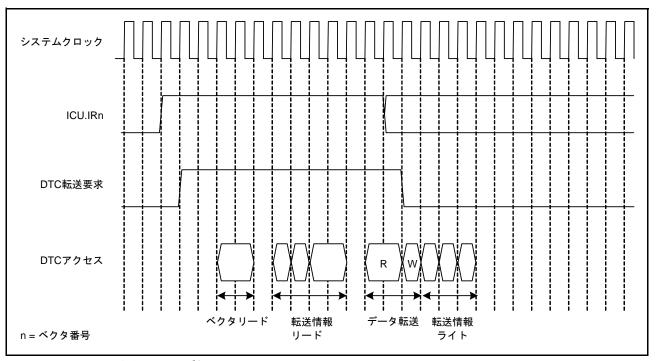

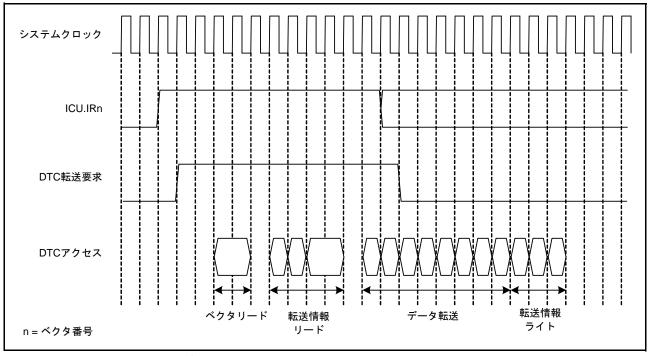

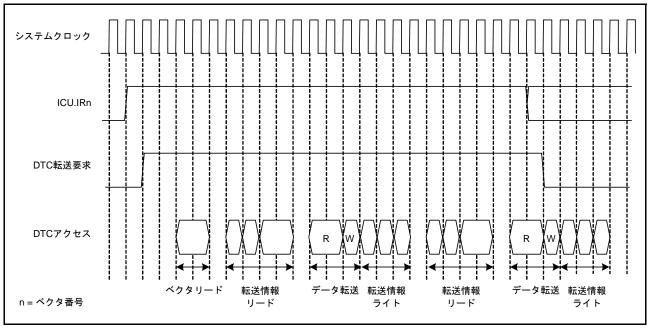

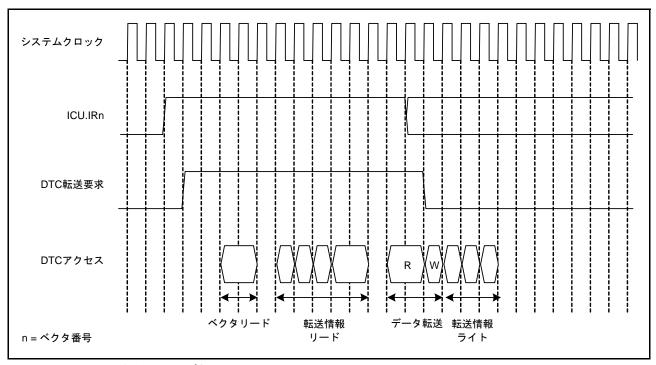

| 16.4.7  | 動作タイミング                          | 279 |

| 16.4.8  | DTC の実行サイクル                      | 282 |

|     | 16.4.9 | )        | DTC のバス権解放タイミング                     | 282 |

|-----|--------|----------|-------------------------------------|-----|

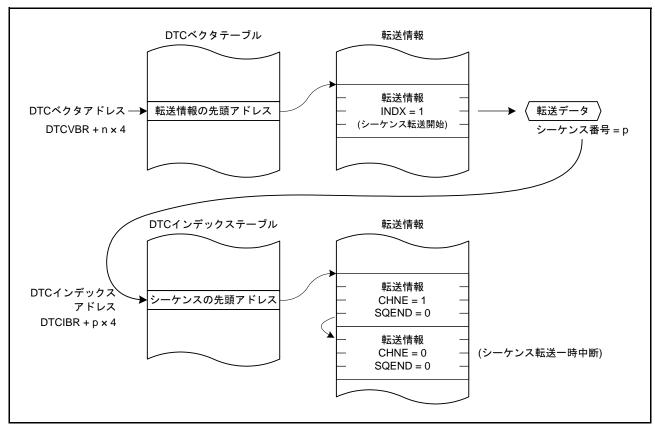

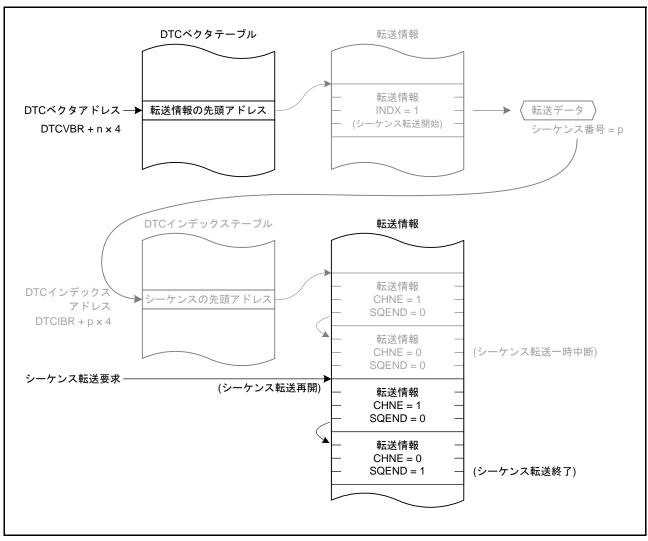

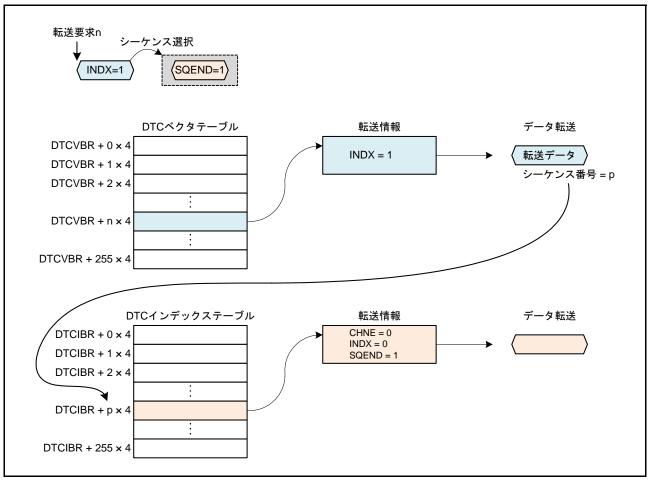

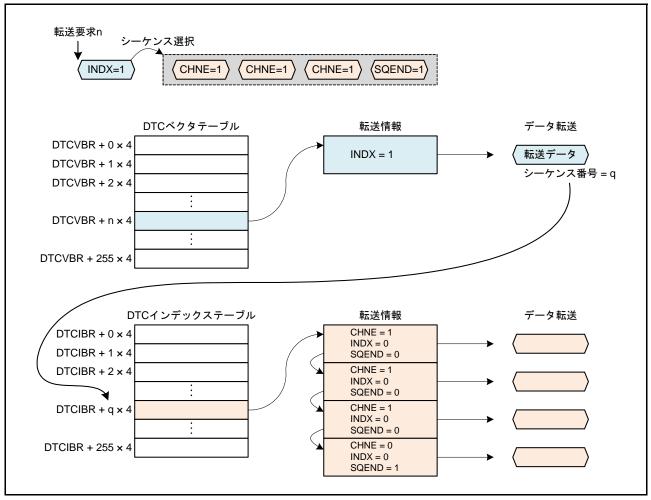

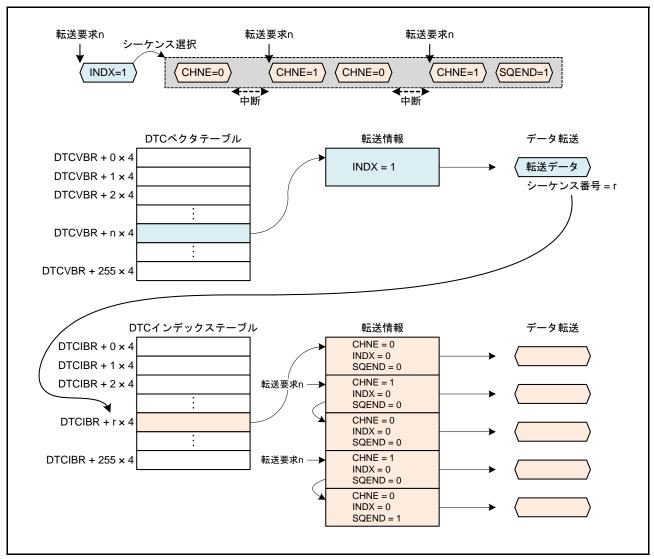

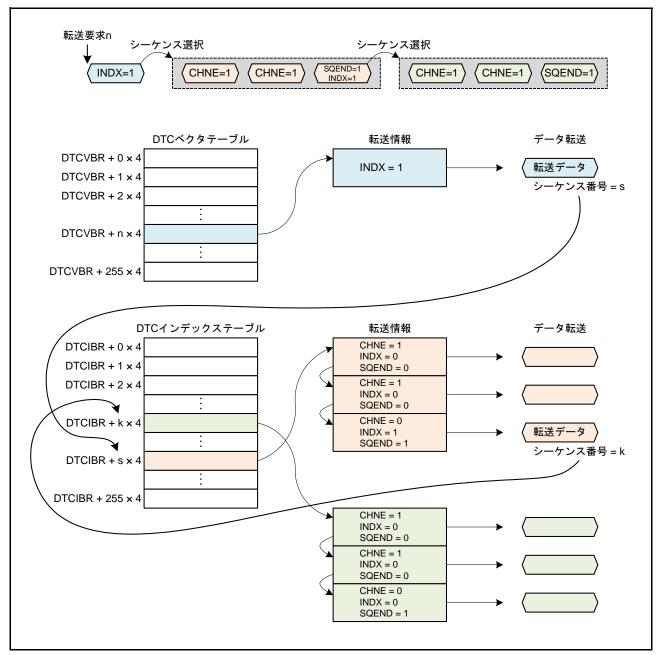

|     | 16.4.1 | 0        | シーケンス転送                             | 283 |

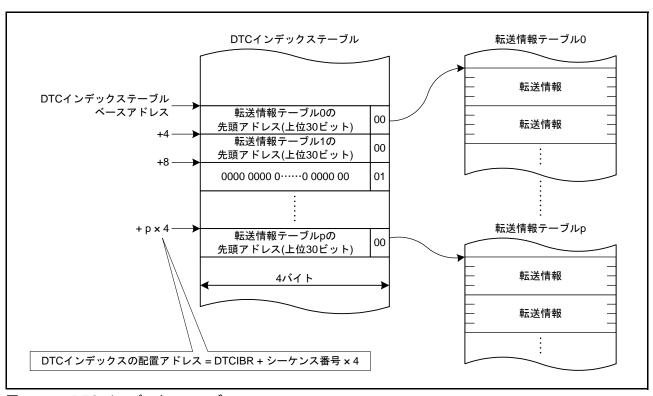

|     | 16.4.1 | 1        | DTC インデックステーブル                      | 285 |

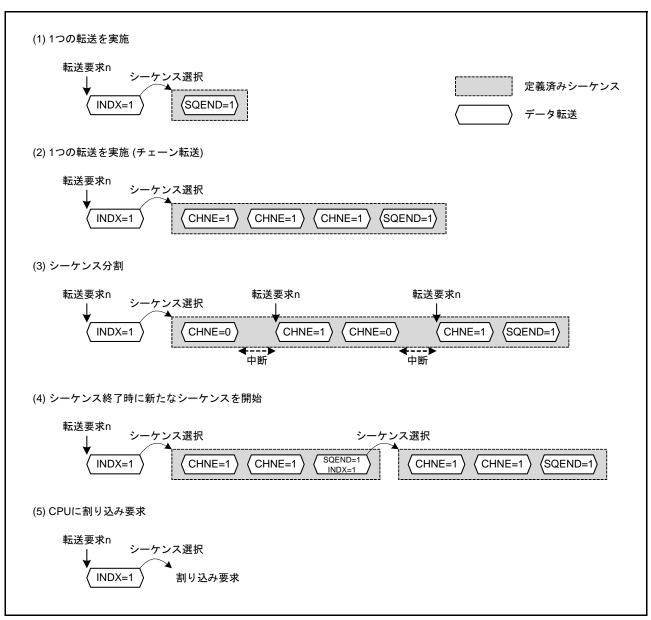

|     | 16.4.1 | 2        | シーケンス転送の動作例                         | 287 |

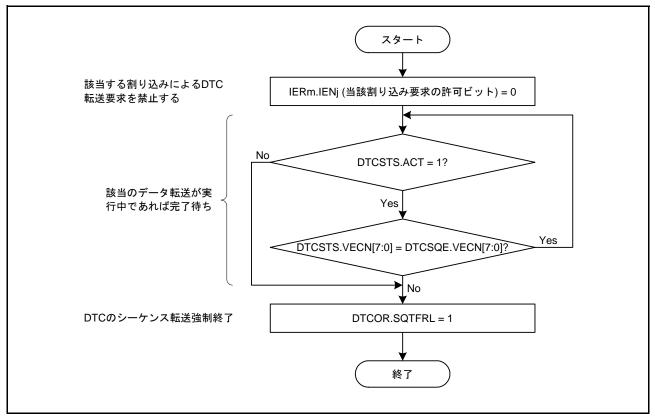

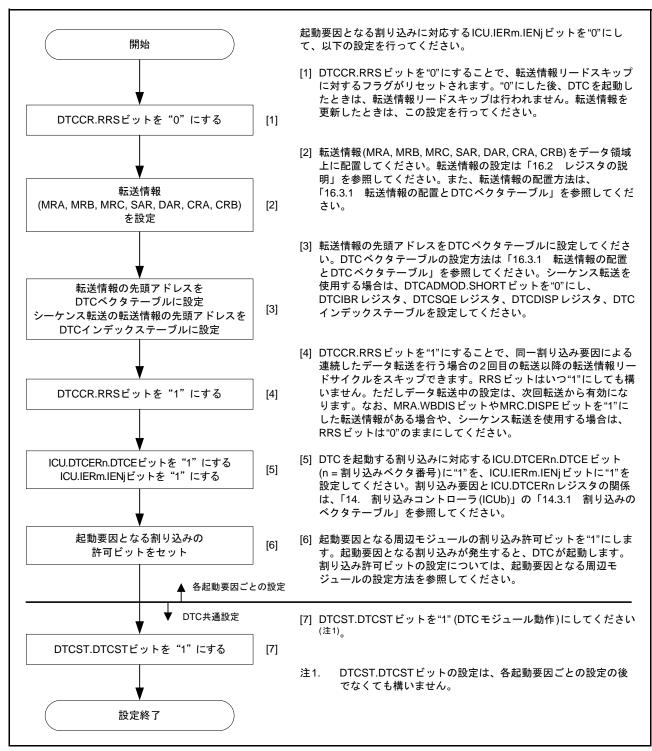

|     | 16.5   | DTC      | の設定手順                               | 293 |

|     | 16.6   | DTC      | 使用例                                 | 294 |

|     | 16.6.1 |          | ノーマル転送                              | 294 |

|     | 16.6.2 |          | カウンタが "0" のときのチェーン転送                | 295 |

|     | 16.6.3 | ;        | シーケンス転送                             | 296 |

|     | 16.7   | 割り       | 込み要因                                | 297 |

|     | 16.8   | 消費       | 電力低減機能                              | 298 |

|     | 16.9   | 使用       | 上の注意事項                              | 299 |

|     | 16.9.1 |          | 転送情報先頭アドレス                          | 299 |

|     | 16.9.2 |          | 転送情報の配置                             | 299 |

|     | 16.9.3 | ;        | シーケンス転送使用時の注意事項                     | 300 |

| 17. | I/O ポ· | <b>-</b> |                                     | 301 |

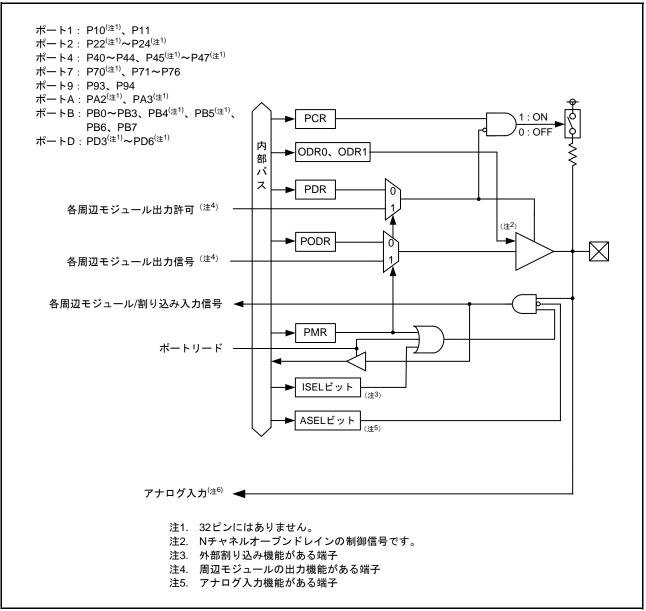

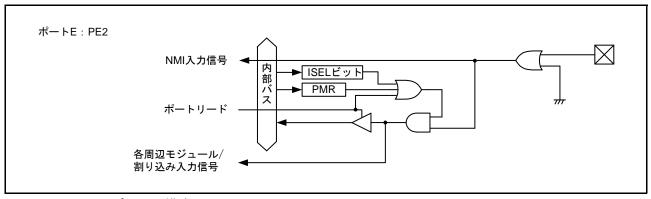

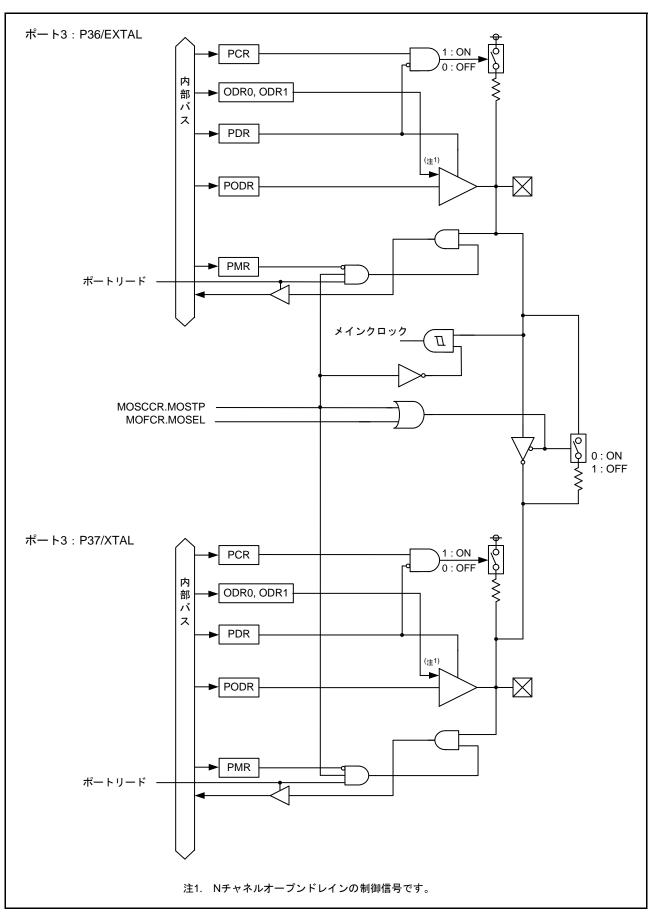

|     | 17.1   | 概要       |                                     | 301 |

|     | 17.2   | 入出       | カポートの構成                             | 303 |

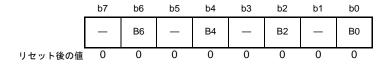

|     | 17.3   | レジ       | スタの説明                               | 305 |

|     | 17.3.1 |          | ポート方向レジスタ (PDR)                     | 305 |

|     | 17.3.2 |          | ポート出力データレジスタ (PODR)                 | 306 |

|     | 17.3.3 | ;        | ポート入力データレジスタ (PIDR)                 | 307 |

|     | 17.3.4 | Ļ        | ポートモードレジスタ (PMR)                    | 308 |

|     | 17.3.5 | ;        | オープンドレイン制御レジスタ 0 (ODR0)             | 309 |

|     | 17.3.6 |          | オープンドレイン制御レジスタ 1 (ODR1)             | 310 |

|     | 17.3.7 |          | プルアップ制御レジスタ (PCR)                   | 311 |

|     | 17.3.8 | ;        | 駆動能力制御レジスタ (DSCR)                   | 312 |

|     | 17.4   | ポー       | ト方向レジスタ (PDR) の初期化                  | 313 |

|     | 17.5   | 未使       | 用端子の処理                              | 314 |

| 18. | マルチ    | ・ファ      | ·<br>ンクションピンコントローラ (MPC)            | 315 |

|     |        |          |                                     |     |

|     | 18.2   | レジ       | スタの説明                               | 318 |

|     | 18.2.1 |          | 書き込みプロテクトレジスタ (PWPR)                | 318 |

|     | 18.2.2 |          | Pln 端子機能制御レジスタ (PlnPFS) (n = 0, 1)  | 319 |

|     | 18.2.3 | ;        | P2n 端子機能制御レジスタ (P2nPFS) (n = 2 ~ 4) | 320 |

|     | 18.2.4 | ļ        | P4n 端子機能制御レジスタ (P4nPFS) (n = 0 ~ 7) |     |

|     | 18.2.5 | ;        | P7n 端子機能制御レジスタ (P7nPFS) (n = 0 ~ 6) |     |

|     | 18.2.6 | <u>,</u> | P9n 端子機能制御レジスタ (P9nPFS) (n = 3, 4)  | 323 |

|     | 18.2.7 | ,        | PAn 端子機能制御レジスタ (PAnPFS) (n = 2, 3)  |     |

|     | 18.2.8 | ;        | PBn 端子機能制御レジスタ (PBnPFS) (n = 0 ~ 7) | 325 |

|     |        |          |                                     |     |

|     | 18.2.9  | PDn 端子機能制御レジスタ (PDnPFS) (n = 3 $\sim$ 6) | 326 |

|-----|---------|------------------------------------------|-----|

|     | 18.2.10 | PEn 端子機能制御レジスタ (PE2PFS)                  | 327 |

|     | 18.3 使月 | 月上の注意事項                                  | 328 |

|     | 18.3.1  | 端子入出力機能設定手順                              | 328 |

|     | 18.3.2  | MPC レジスタ設定する場合の注意事項                      | 328 |

|     | 18.3.3  | アナログ機能を使う場合の注意事項                         | 329 |

|     | 18.3.4  | PB1 端子の入力レベルについての注意事項                    | 329 |

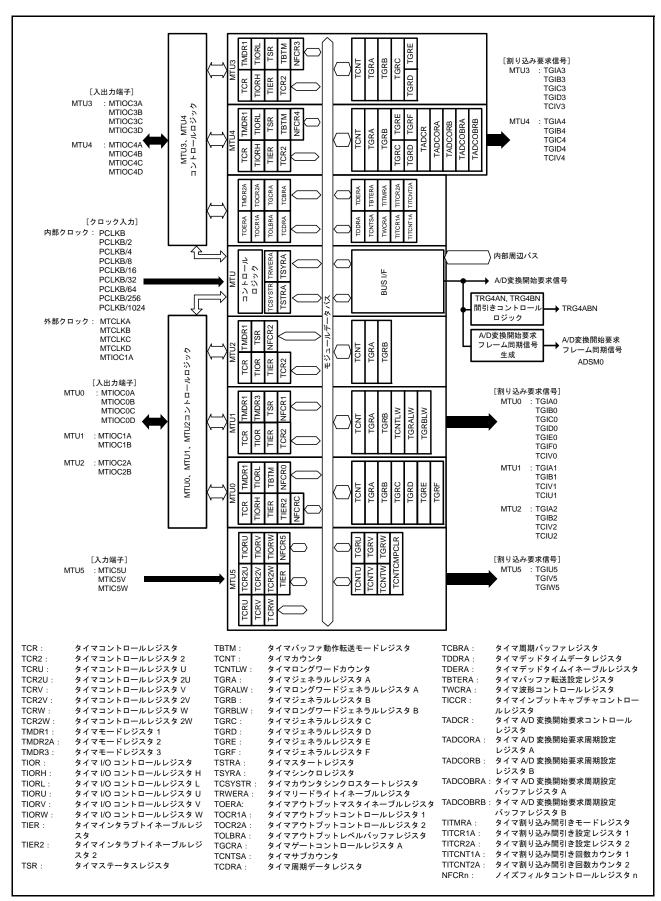

| 19. | マルチフラ   | ァンクションタイマパルスユニット 3 (MTU3c)               | 330 |

|     | 19.1 概要 | Ŧ                                        | 330 |

|     | 19.2 レミ | ブスタの説明                                   | 335 |

|     | 19.2.1  | タイマコントロールレジスタ (TCR)                      | 335 |

|     | 19.2.2  | タイマコントロールレジスタ 2 (TCR2)                   | 337 |

|     | 19.2.3  | タイマモードレジスタ 1 (TMDR1)                     | 341 |

|     | 19.2.4  | タイマモードレジスタ 2 (TMDR2A)                    | 343 |

|     | 19.2.5  | タイマモードレジスタ 3 (TMDR3)                     | 344 |

|     | 19.2.6  | タイマ I/O コントロールレジスタ (TIOR)                | 346 |

|     | 19.2.7  | タイマコンペアマッチクリアレジスタ (TCNTCMPCLR)           | 357 |

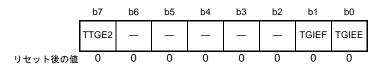

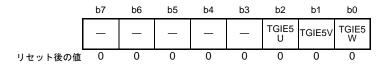

|     | 19.2.8  | タイマインタラプトイネーブルレジスタ (TIER)                | 358 |

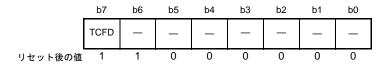

|     | 19.2.9  | タイマステータスレジスタ (TSR)                       | 361 |

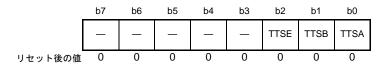

|     | 19.2.10 | タイマバッファ動作転送モードレジスタ (TBTM)                | 362 |

|     | 19.2.11 | タイマインプットキャプチャコントロールレジスタ (TICCR)          | 363 |

|     | 19.2.12 | タイマカウンタ (TCNT)                           | 364 |

|     | 19.2.13 | タイマロングワードカウンタ (TCNTLW)                   | 364 |

|     | 19.2.14 | タイマジェネラルレジスタ (TGR)                       | 365 |

|     | 19.2.15 | タイマロングワードジェネラルレジスタ (TGRALW, TGRBLW)      | 366 |

|     | 19.2.16 | タイマスタートレジスタ (TSTRA, TSTR)                | 367 |

|     | 19.2.17 | タイマシンクロレジスタ (TSYRA)                      | 369 |

|     | 19.2.18 | タイマカウンタシンクロスタートレジスタ (TCSYSTR)            | 370 |

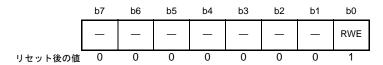

|     | 19.2.19 | タイマリードライトイネーブルレジスタ (TRWERA)              | 371 |

|     | 19.2.20 | タイマアウトプットマスタイネーブルレジスタ (TOERA)            | 372 |

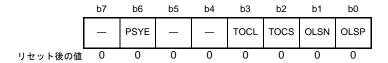

|     | 19.2.21 | タイマアウトプットコントロールレジスタ 1 (TOCR1A)           | 373 |

|     | 19.2.22 | タイマアウトプットコントロールレジスタ 2 (TOCR2A)           | 375 |

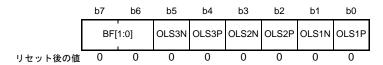

|     | 19.2.23 | タイマアウトプットレベルバッファレジスタ (TOLBRA)            | 378 |

|     | 19.2.24 | タイマゲートコントロールレジスタ A (TGCRA)               | 379 |

|     | 19.2.25 | タイマサブカウンタ (TCNTSA)                       | 381 |

|     | 19.2.26 | タイマ周期データレジスタ (TCDRA)                     | 381 |

|     | 19.2.27 | タイマ周期バッファレジスタ (TCBRA)                    | 382 |

|     | 19.2.28 | タイマデッドタイムデータレジスタ (TDDRA)                 | 382 |

|     | 19.2.29 | タイマデッドタイムイネーブルレジスタ (TDERA)               | 383 |

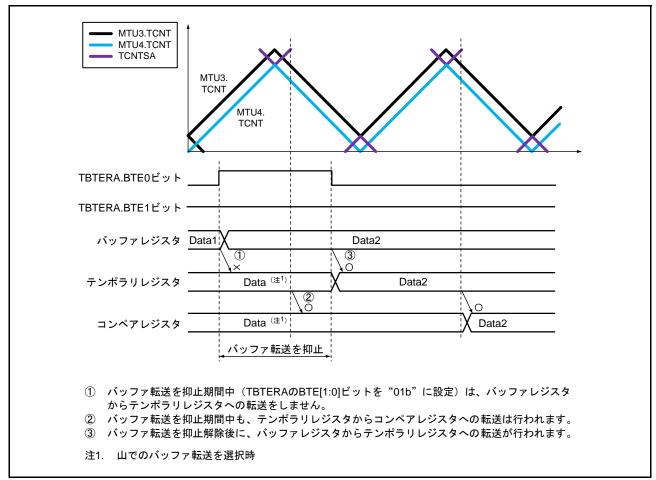

|     | 19.2.30 | タイマバッファ転送設定レジスタ (TBTERA)                 |     |

|     |         |                                          |     |

|     | 19.2.31  | タイマ波形コントロールレジスタ (TWCRA)                          | 385 |

|-----|----------|--------------------------------------------------|-----|

|     | 19.2.32  | ノイズフィルタコントロールレジスタ n (NFCRn) (n = 0 $\sim$ 4, C)  | 386 |

|     | 19.2.33  | ノイズフィルタコントロールレジスタ 5 (NFCR5)                      | 389 |

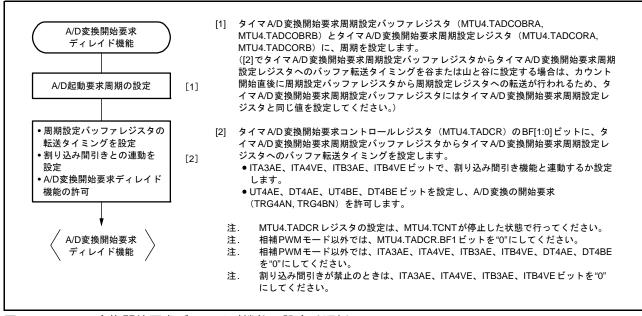

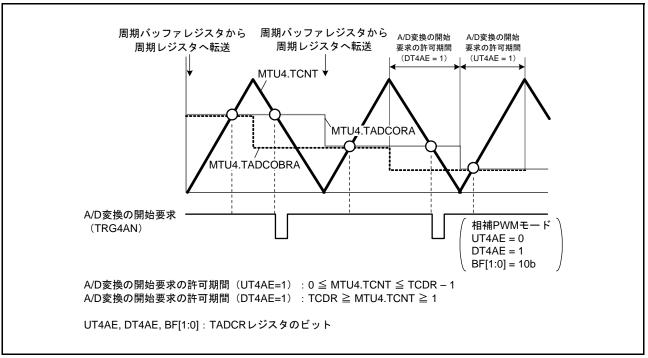

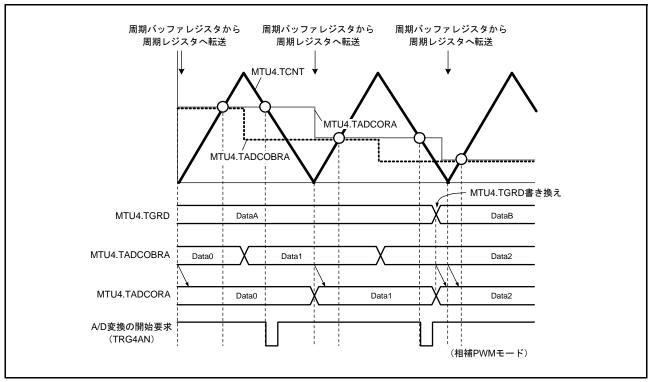

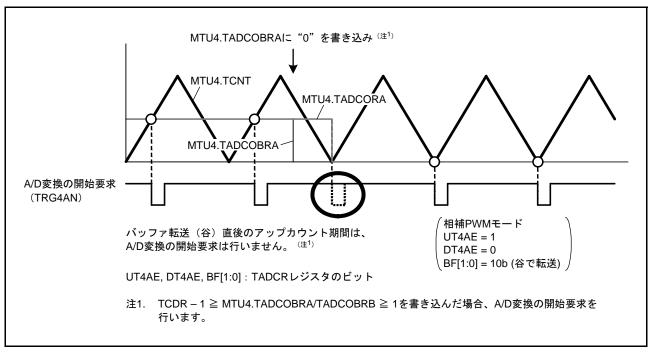

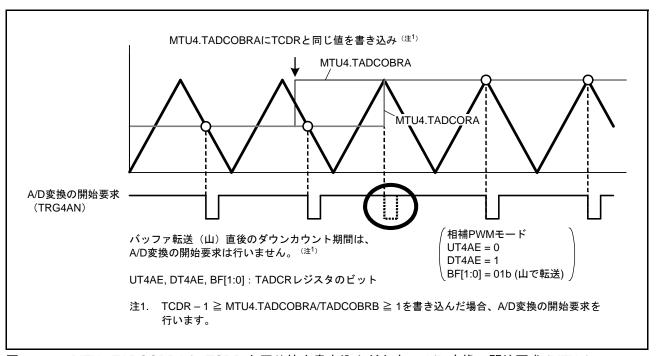

|     | 19.2.34  | タイマ A/D 変換開始要求コントロールレジスタ (TADCR)                 | 390 |

|     | 19.2.35  | タイマ A/D 変換開始要求周期設定レジスタ (TADCORA, TADCORB)        | 392 |

|     | 19.2.36  | タイマ A/D 変換開始要求周期設定バッファレジスタ (TADCOBRA, TADCOBRB). | 392 |

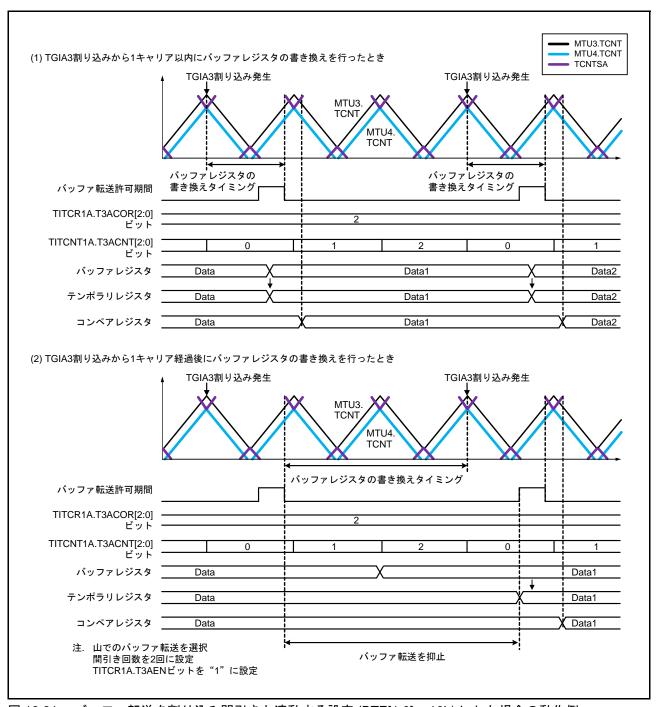

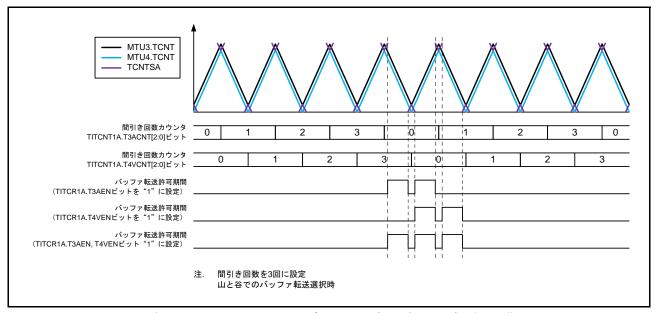

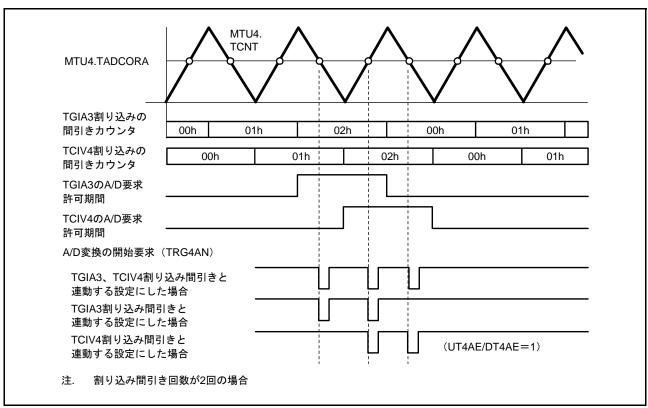

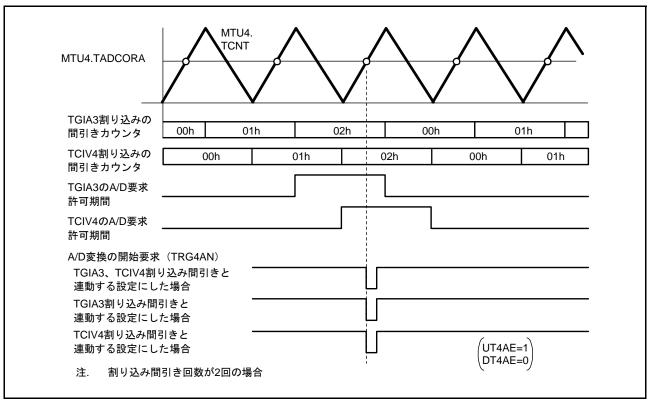

|     | 19.2.37  | タイマ割り込み間引きモードレジスタ (TITMRA)                       | 393 |

|     | 19.2.38  | タイマ割り込み間引き設定レジスタ 1 (TITCR1A)                     | 394 |

|     | 19.2.39  | タイマ割り込み間引き回数カウンタ 1 (TITCNT1A)                    | 395 |

|     | 19.2.40  | タイマ割り込み間引き設定レジスタ 2 (TITCR2A)                     | 396 |

|     | 19.2.41  | タイマ割り込み間引き回数カウンタ 2 (TITCNT2A)                    | 397 |

|     | 19.2.42  | A/D 変換開始要求選択レジスタ 0 (TADSTRGR0)                   | 398 |

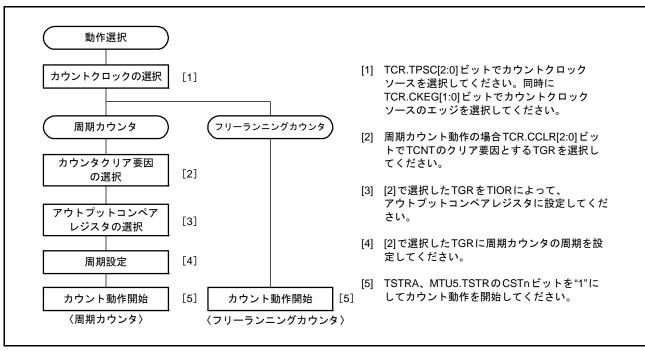

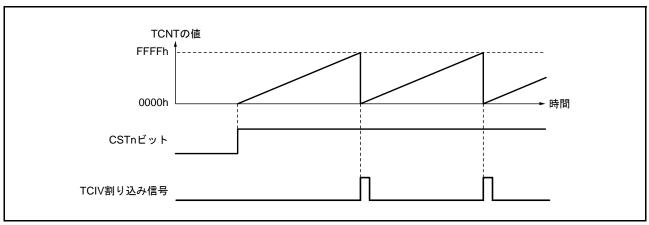

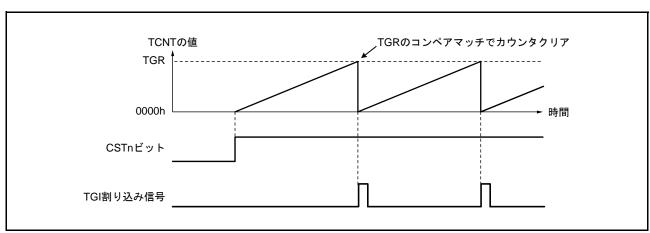

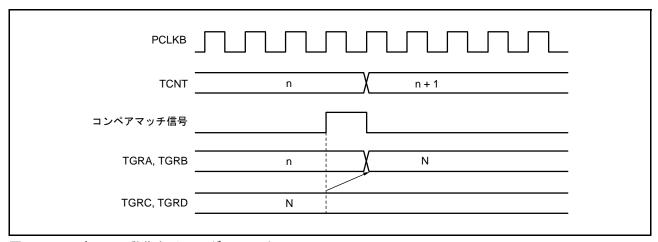

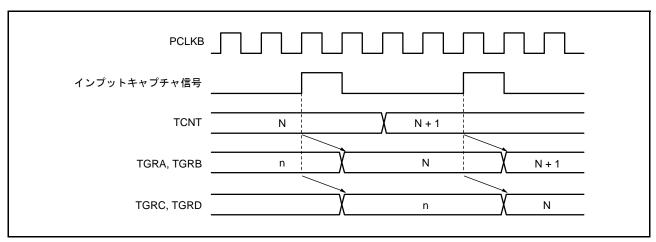

| 19. | 3 動作     | 説明                                               | 399 |

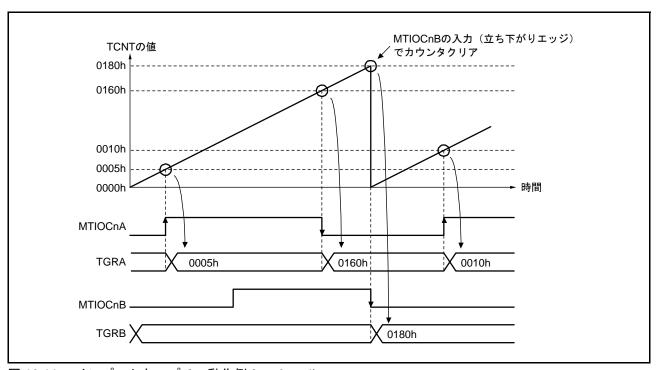

|     | 19.3.1   | 基本動作                                             | 399 |

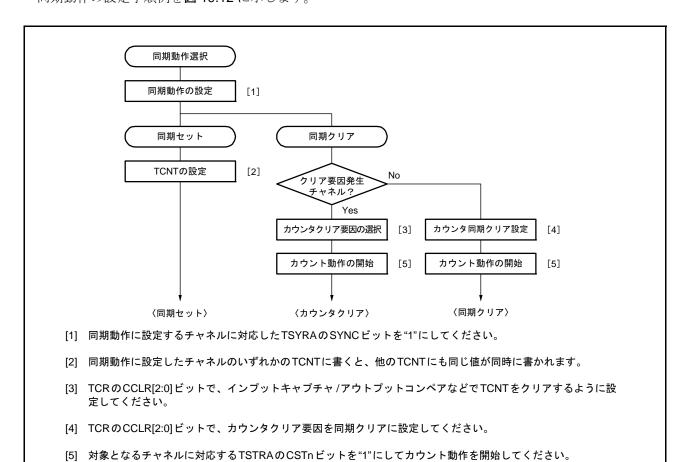

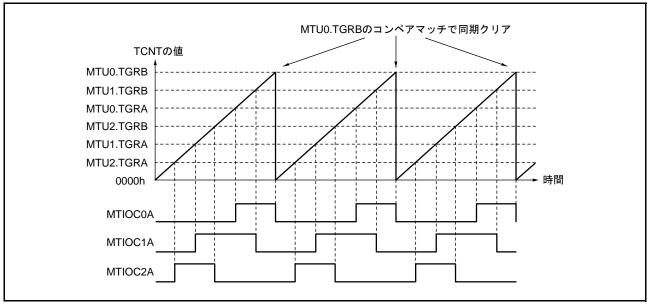

|     | 19.3.2   | 同期動作                                             | 405 |

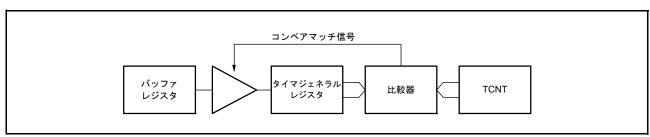

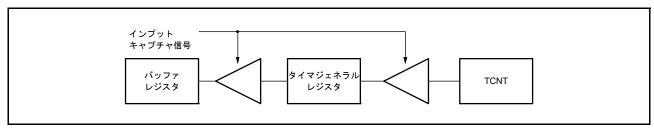

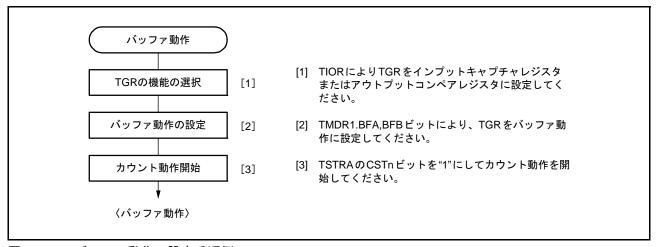

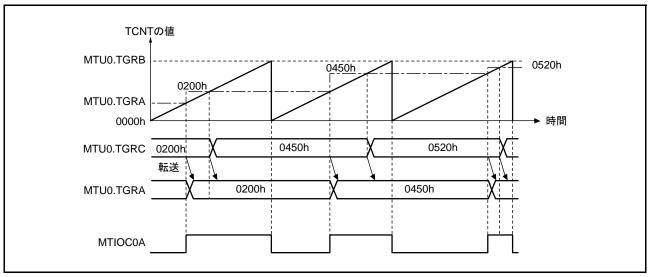

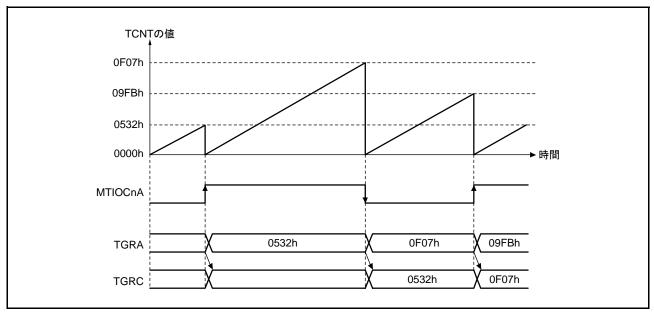

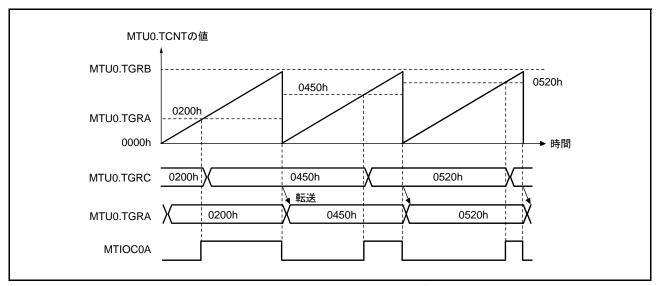

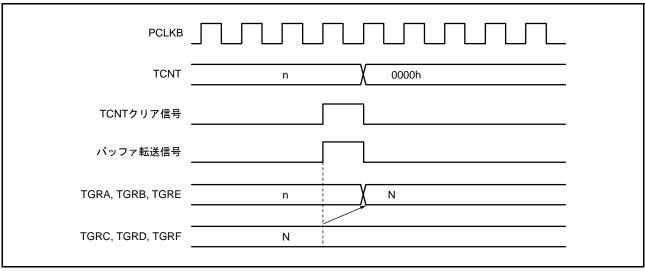

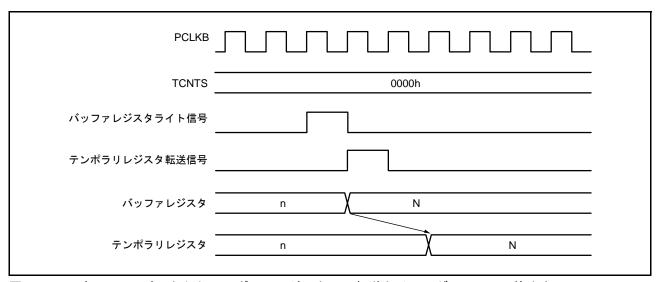

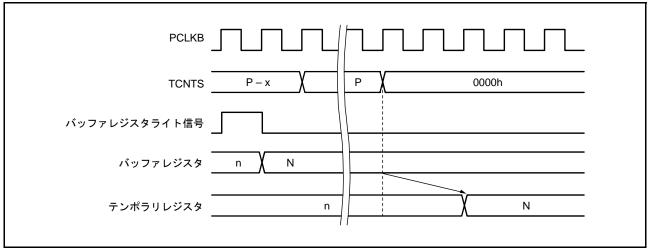

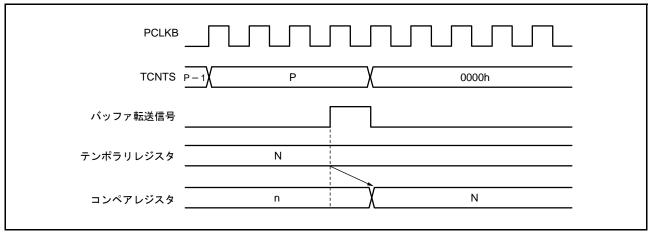

|     | 19.3.3   | バッファ動作                                           | 407 |

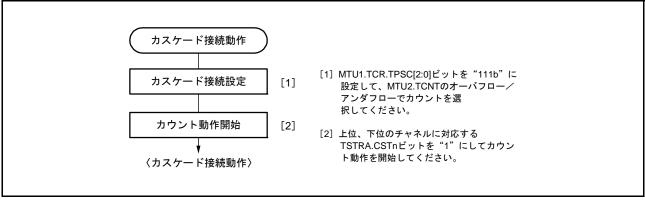

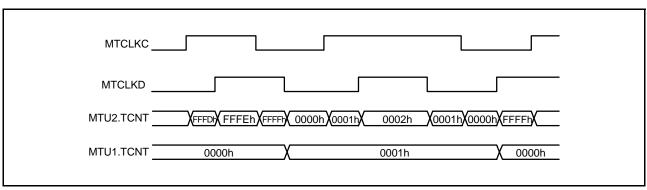

|     | 19.3.4   | カスケード接続動作                                        | 412 |

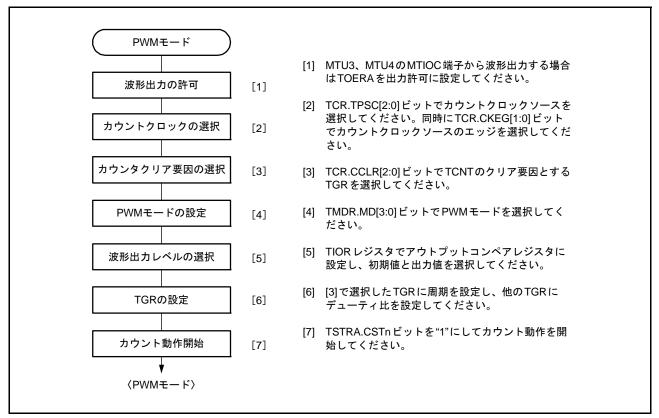

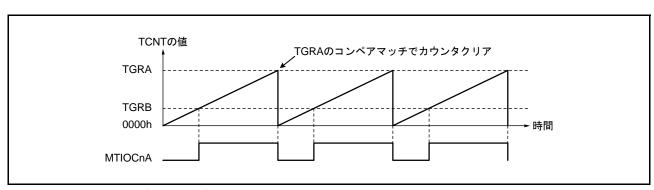

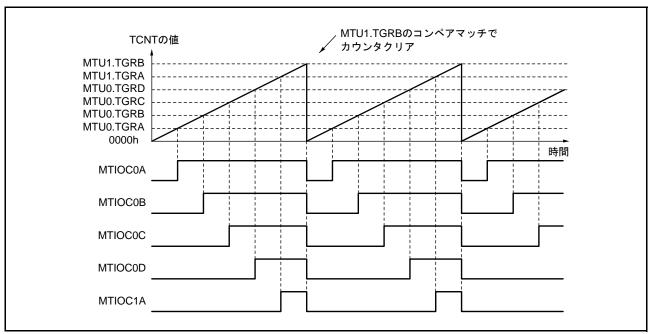

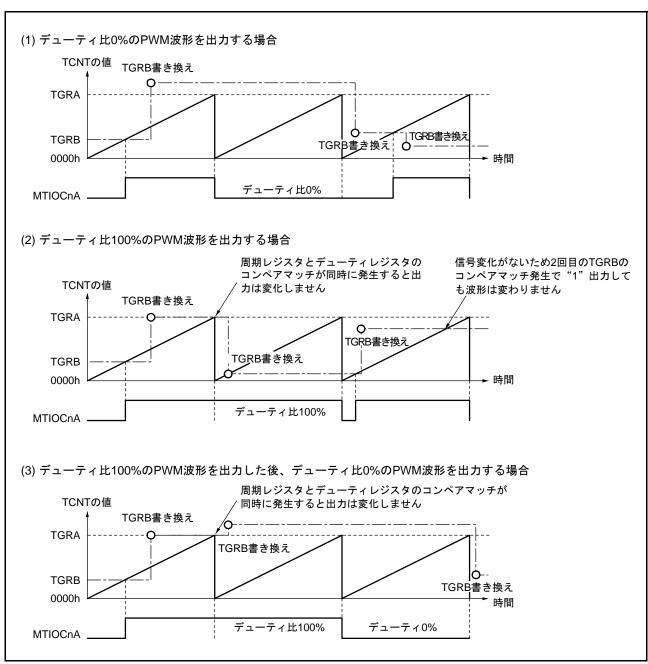

|     | 19.3.5   | PWM モード                                          | 417 |

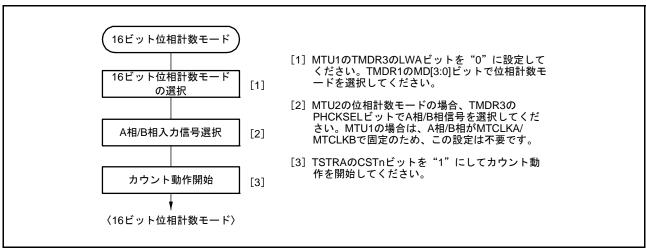

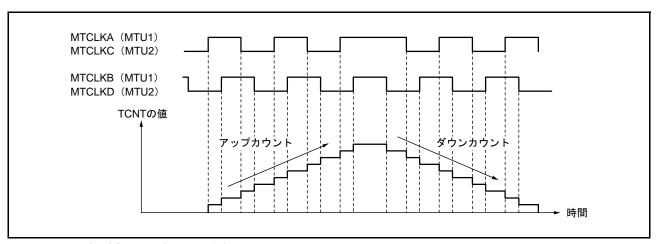

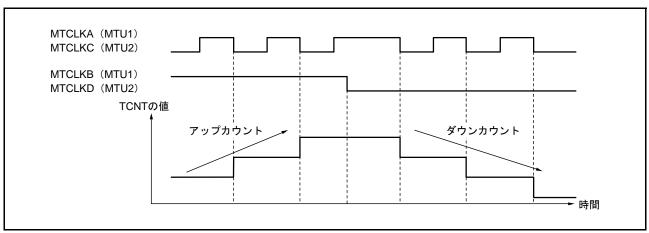

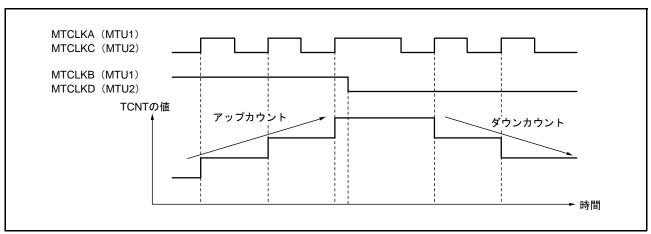

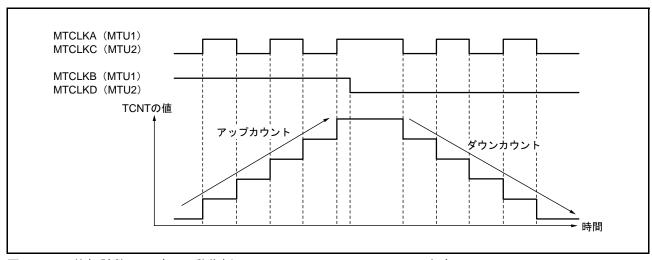

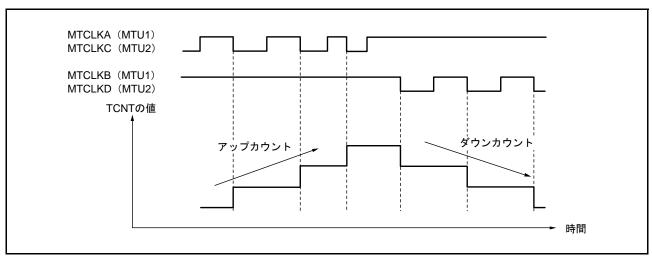

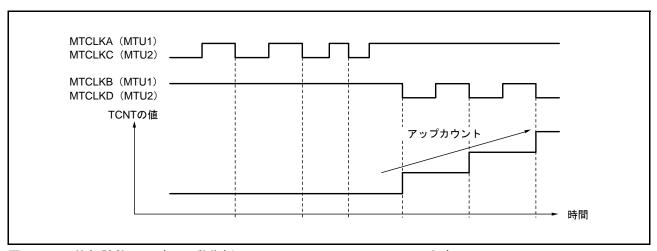

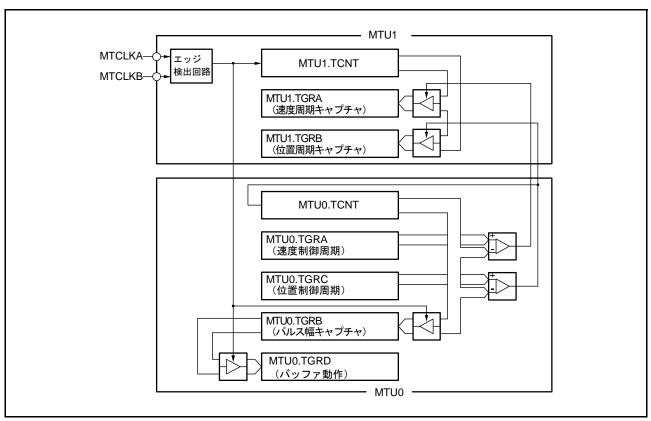

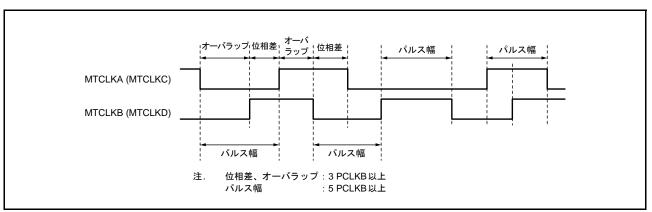

|     | 19.3.6   | 位相計数モード                                          | 422 |

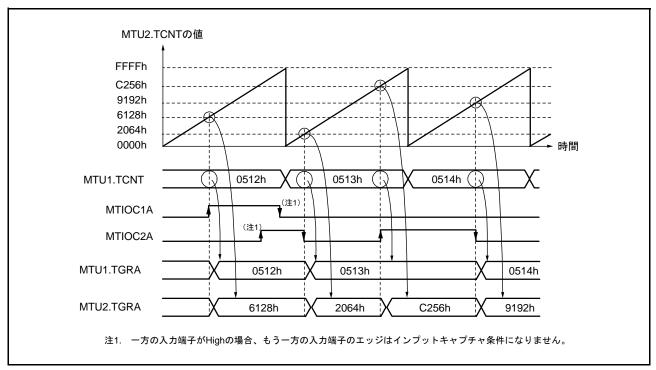

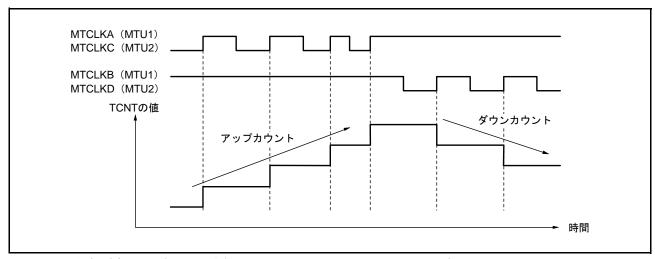

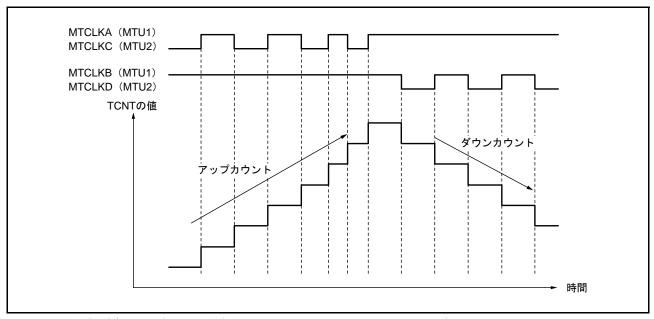

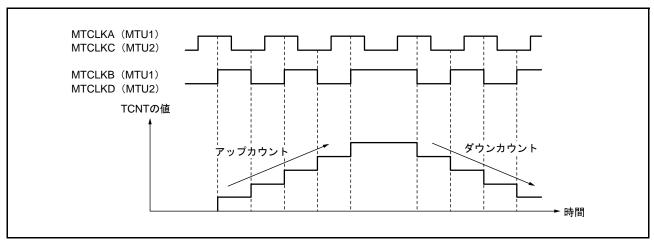

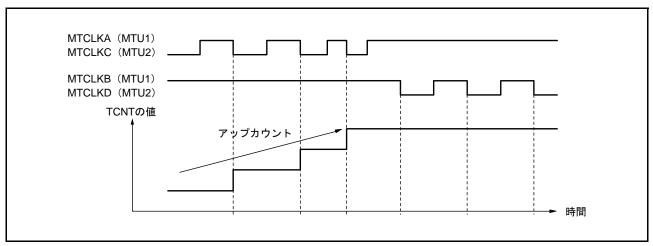

|     | 19.3.6.1 | 16 ビット位相計数モード                                    | 422 |

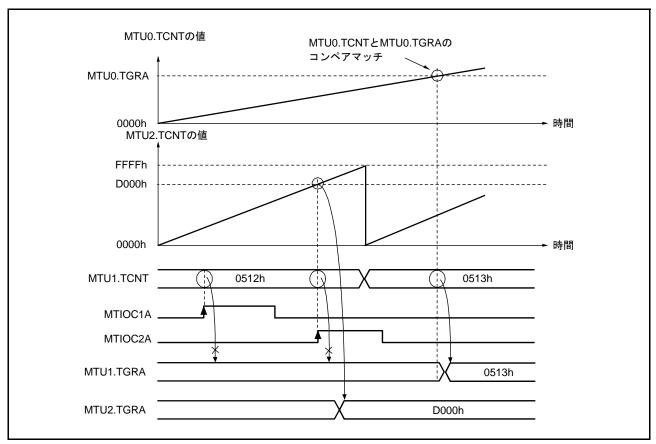

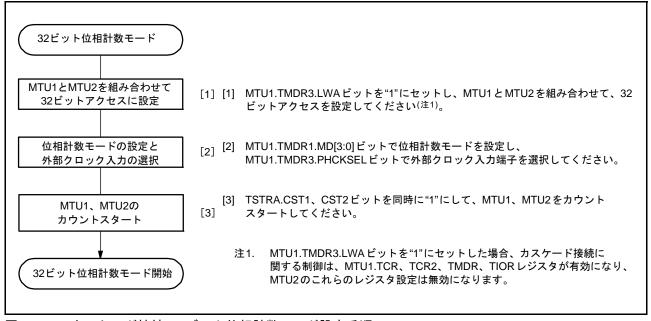

|     | 19.3.6.2 | 2 カスケード接続 32 ビット位相計数モード                          | 434 |

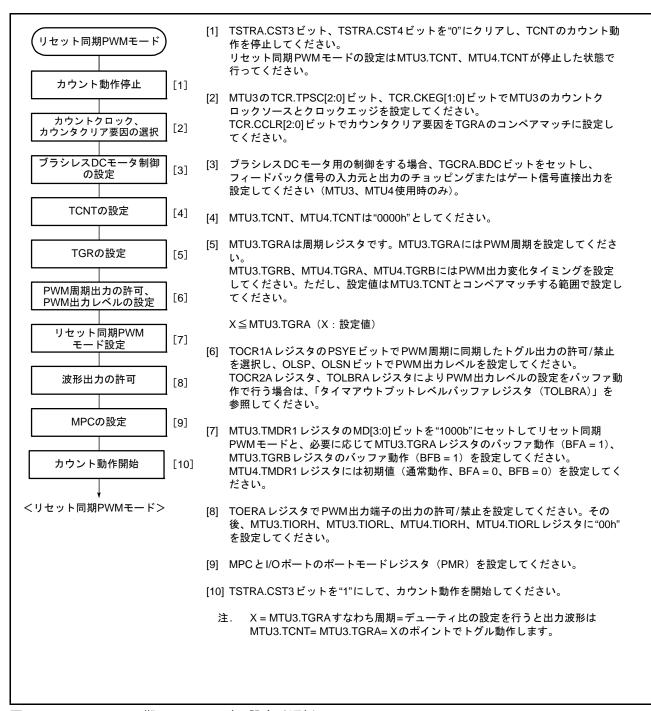

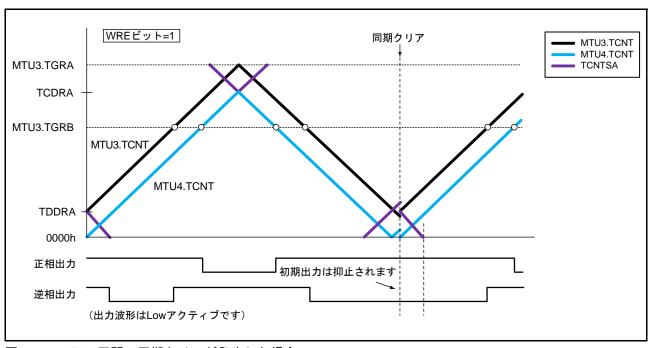

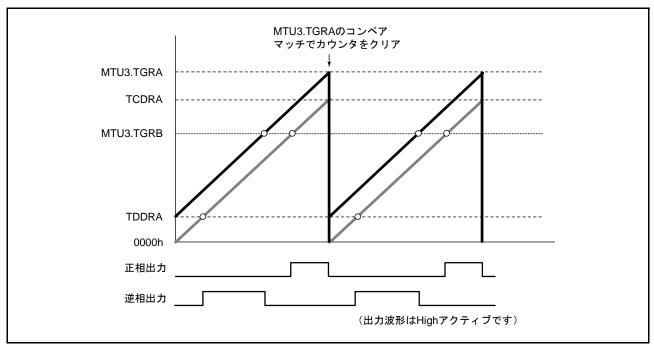

|     | 19.3.7   | リセット同期 PWM モード                                   | 435 |

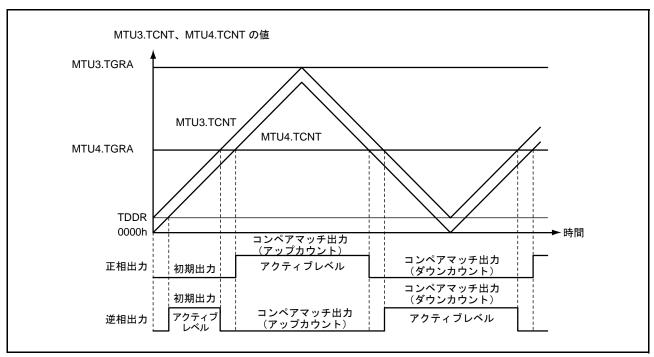

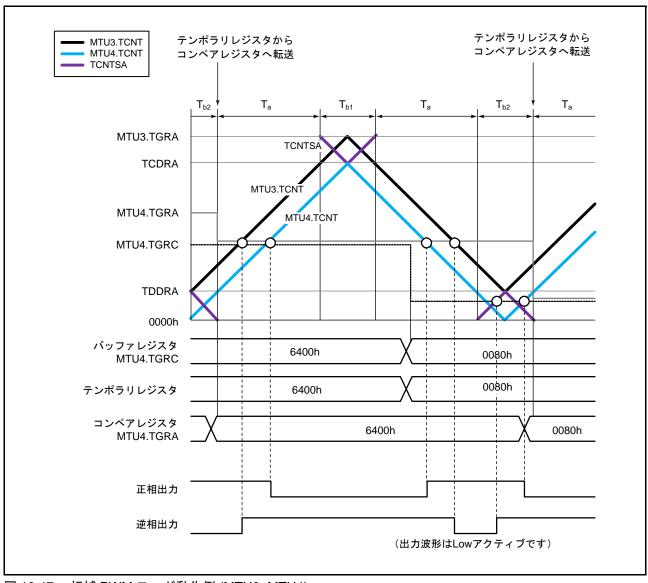

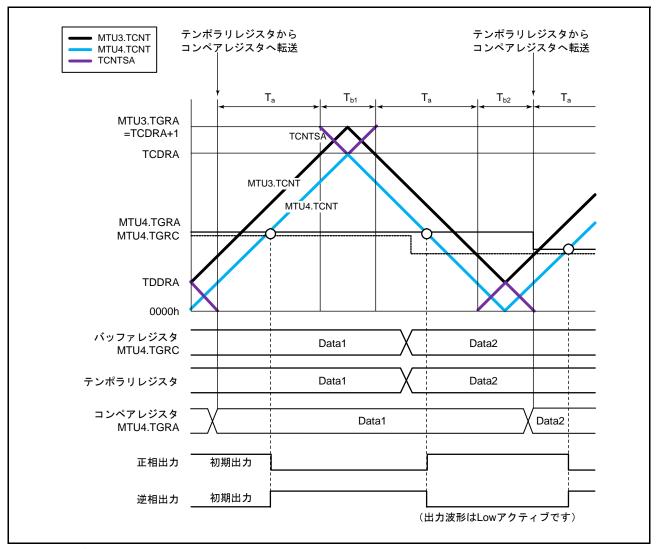

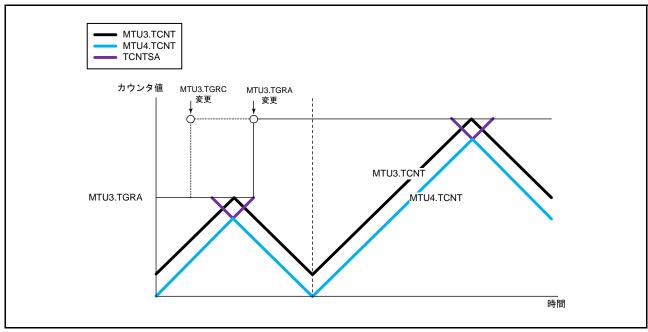

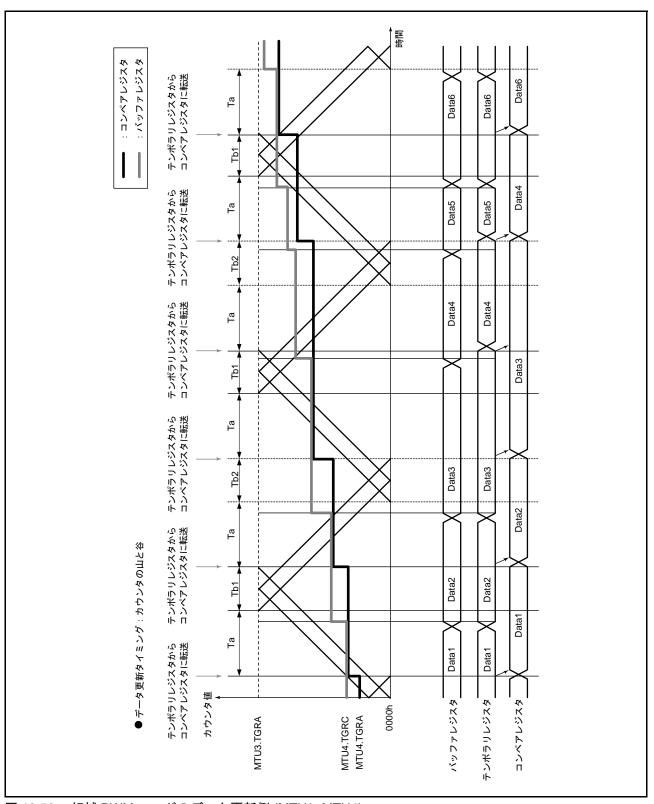

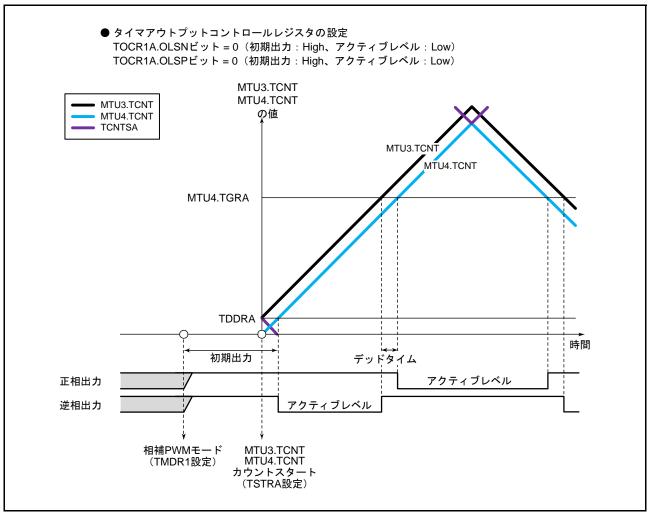

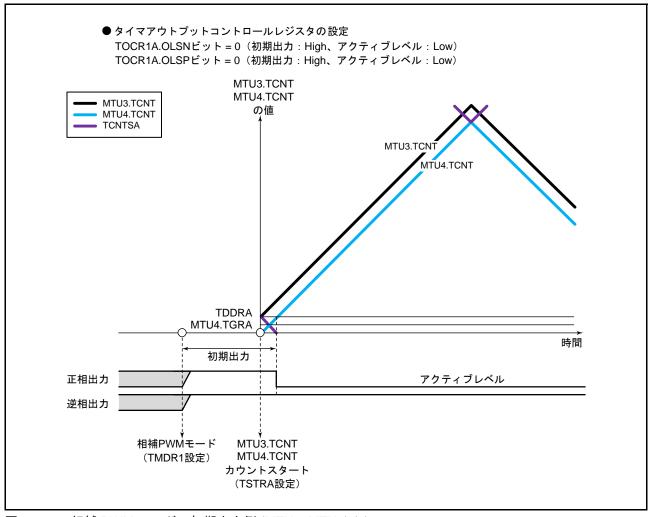

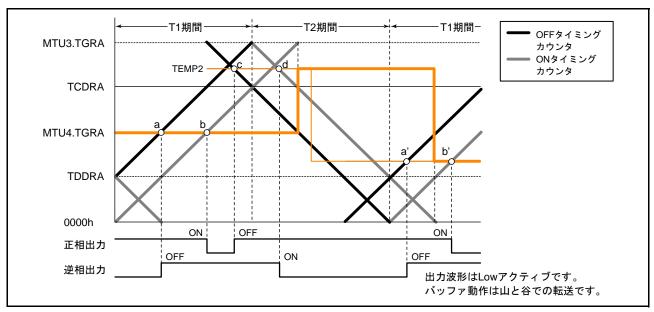

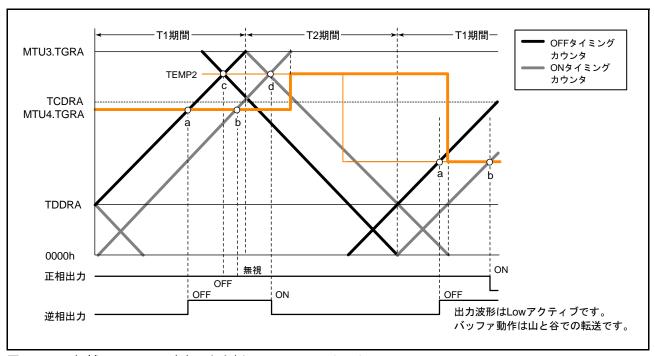

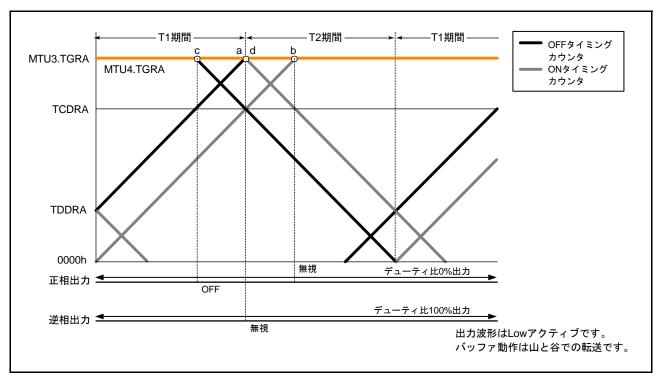

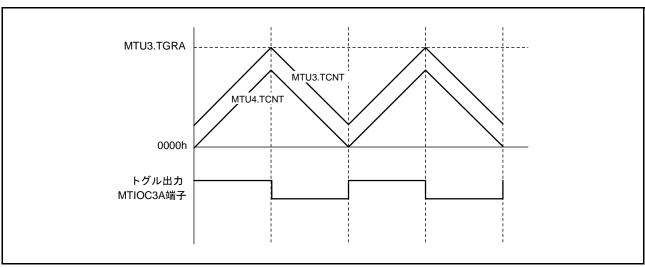

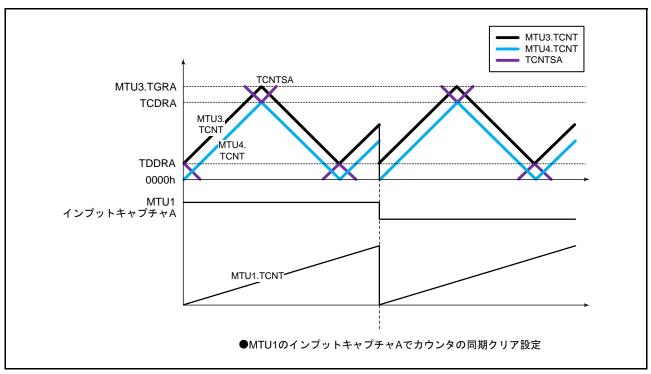

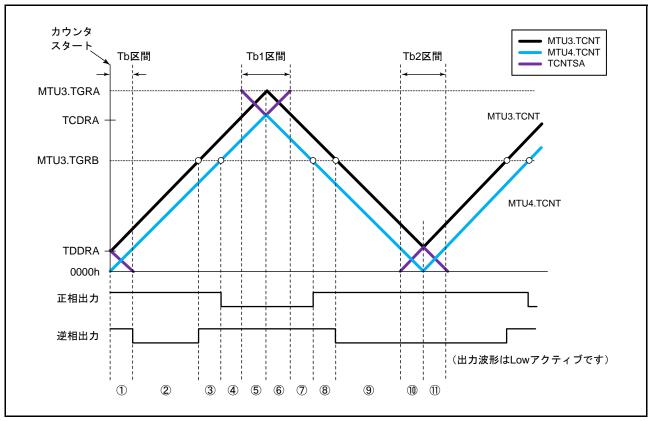

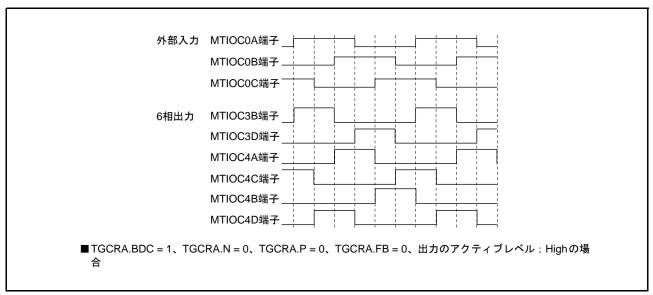

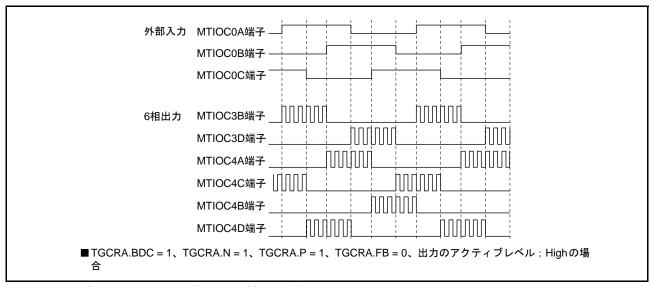

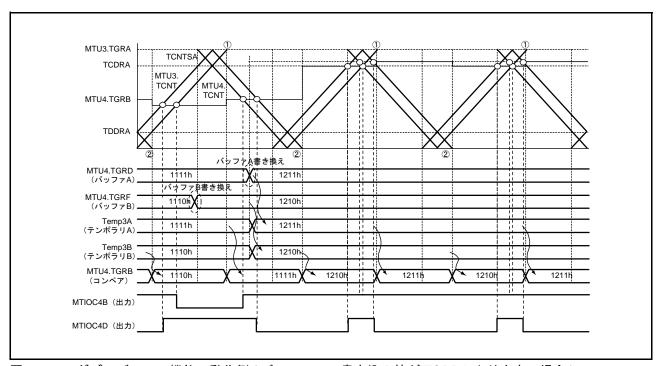

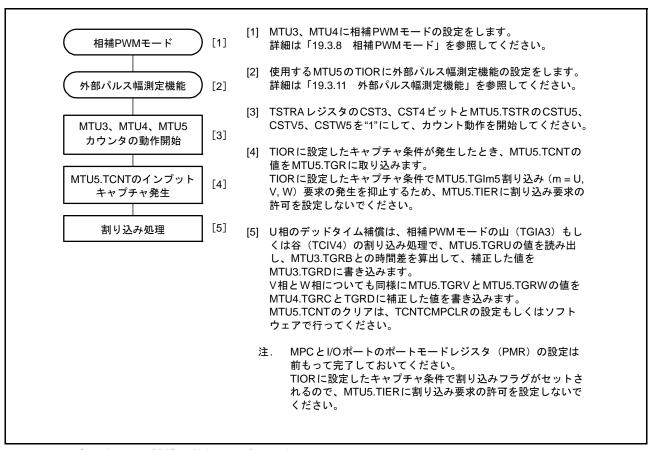

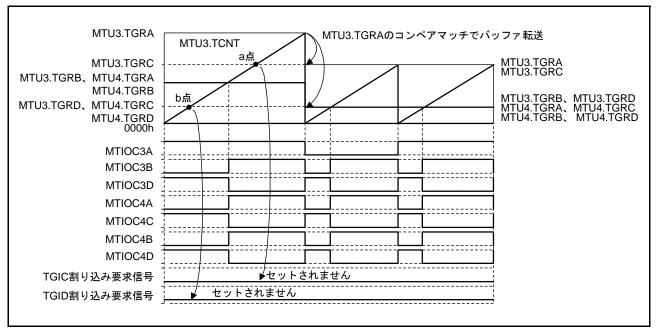

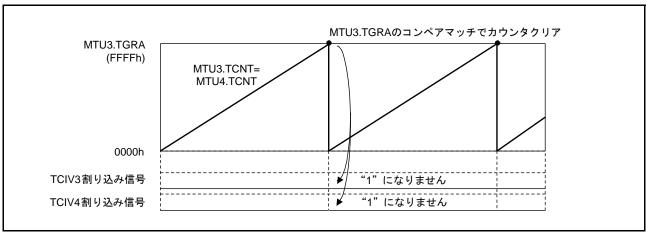

|     | 19.3.8   | 相補 PWM モード                                       | 438 |

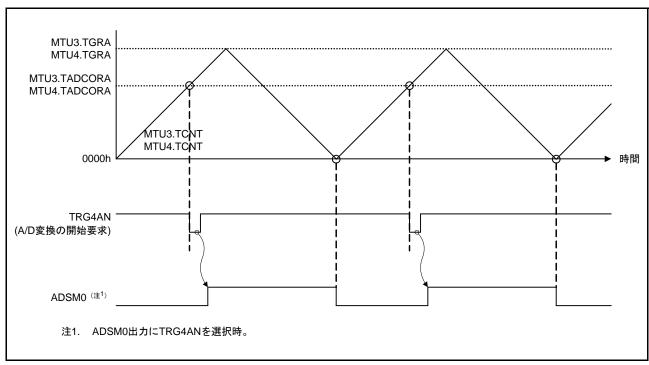

|     | 19.3.9   | A/D 変換開始要求ディレイド機能                                | 473 |

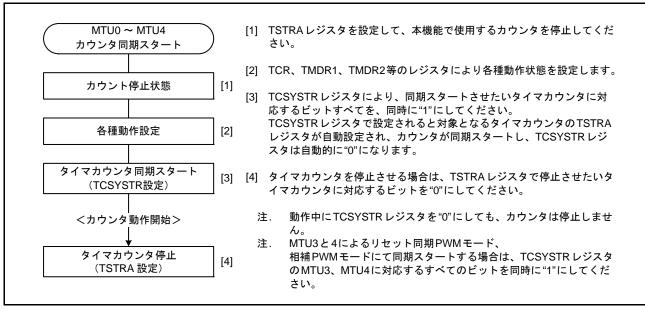

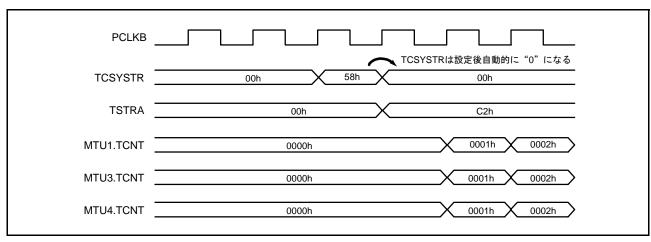

|     | 19.3.10  | MTU0~MTU4の同期動作                                   | 480 |

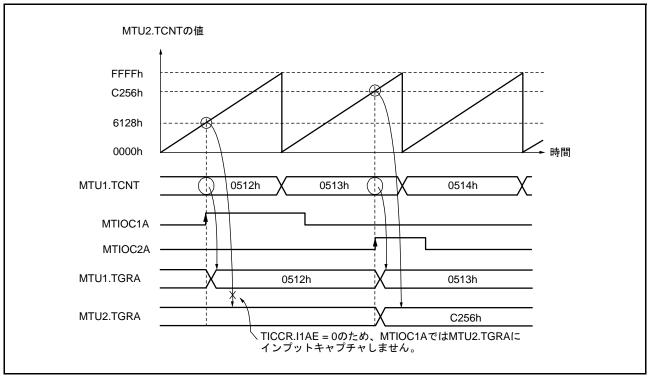

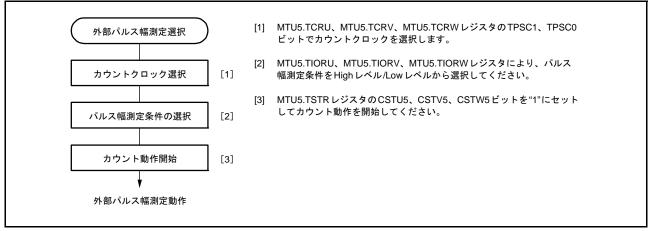

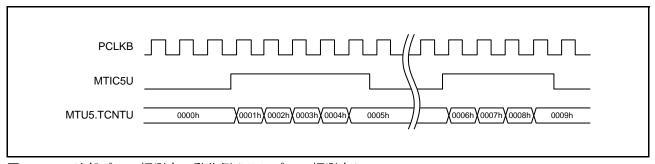

|     | 19.3.11  | 外部パルス幅測定機能                                       | 481 |

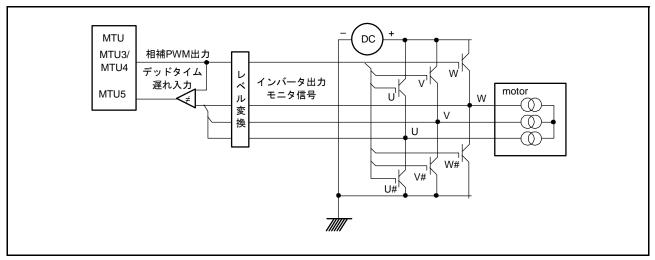

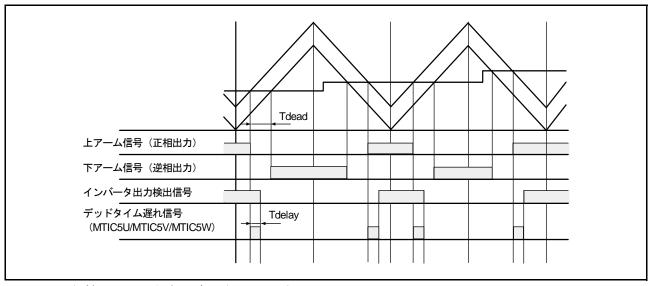

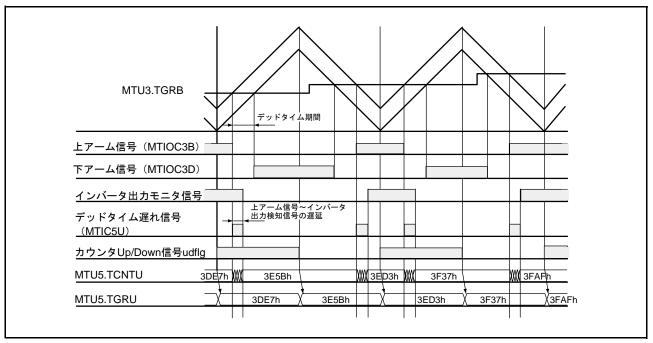

|     | 19.3.12  | デッドタイム補償用機能                                      | 482 |

|     | 19.3.13  | 相補 PWM モード時の山と谷での TCNTU, TCNTV, TCNTW キャプチャ動作    | 484 |

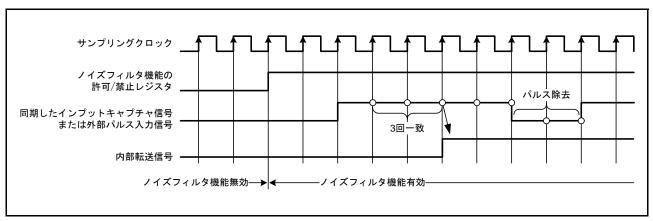

|     | 19.3.14  | ノイズフィルタ機能                                        | 485 |

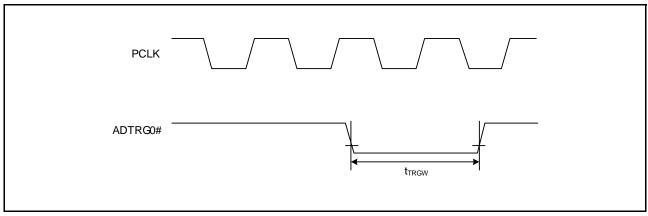

|     | 19.3.15  | A/D 変換開始要求フレーム同期信号                               | 485 |

| 19. | 4 割り     | 込み要因                                             | 486 |

|     | 19.4.1   | 割り込み要因と優先順位                                      | 486 |

|     | 19.4.2   | DTC の起動                                          | 487 |

|     | 19.4.3   | A/D コンバータの起動                                     | 488 |

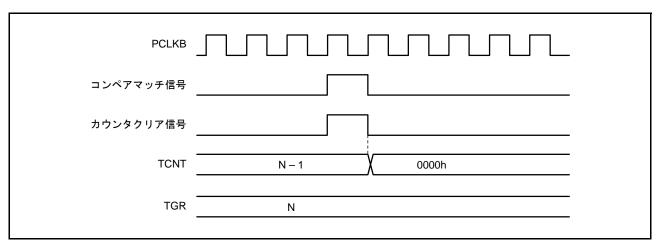

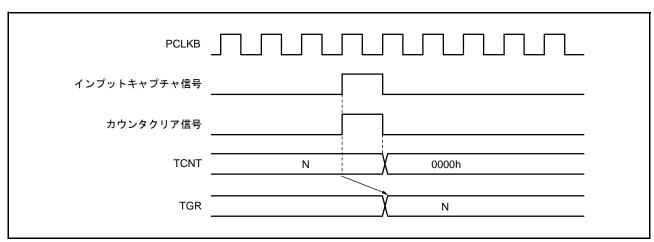

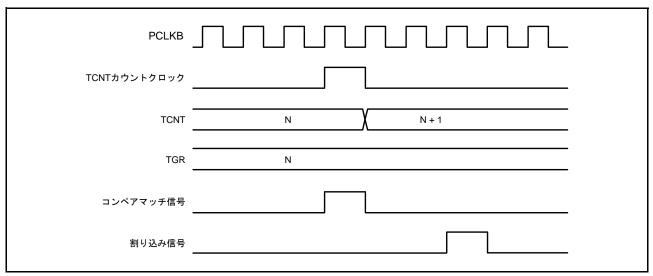

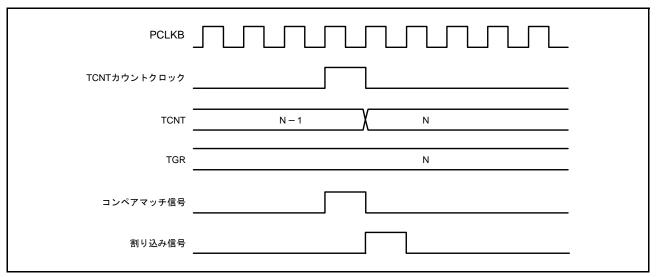

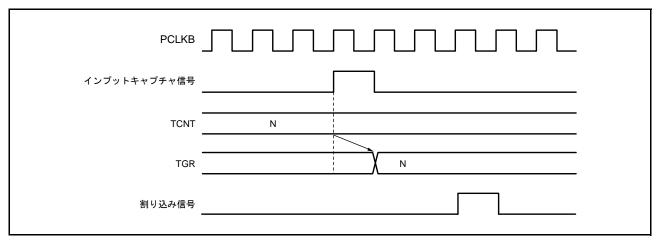

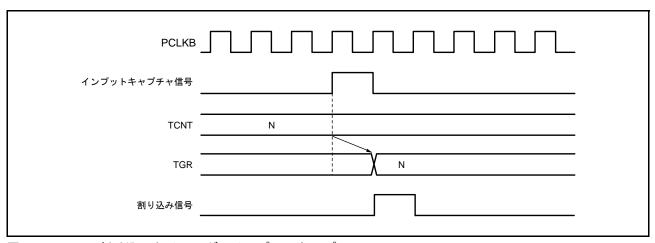

| 19. | 5 動作     | :タイミング                                           | 490 |

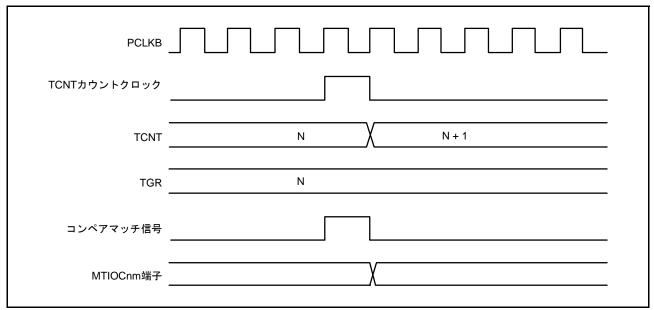

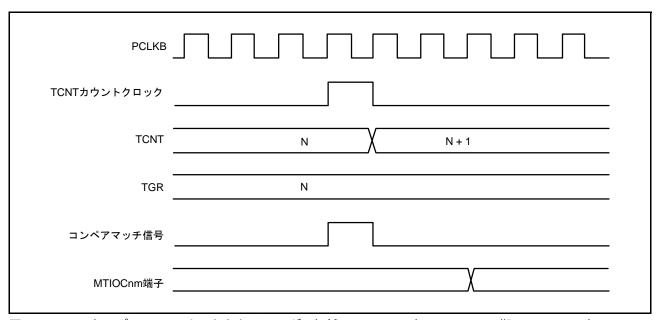

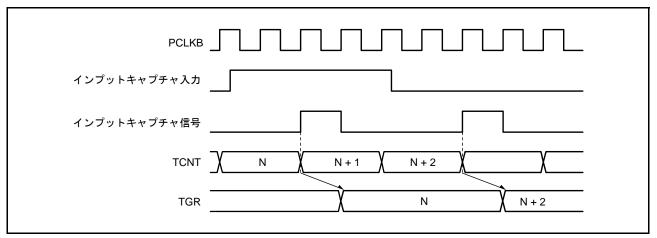

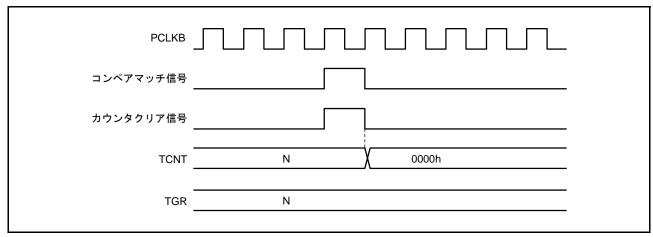

|     | 19.5.1   | 入出力タイミング                                         | 490 |

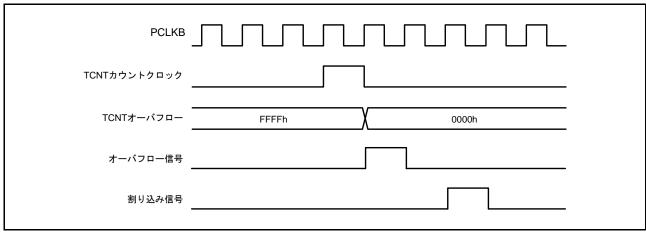

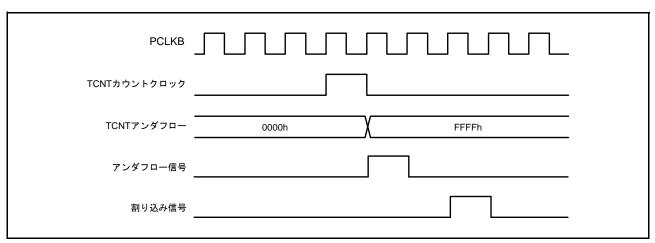

|     | 19.5.2   | 割り込み信号タイミング                                      | 496 |

| 19. | 6 使用     | 上の注意事項                                           |     |

|     | 19.6.1   | モジュールストップ機能の設定                                   | 499 |

|     | 19.6.2   | カウントクロックの制限事項                                    | 499 |

| 19.6.3   | 周期設定上の注意事項                                             | 499 |

|----------|--------------------------------------------------------|-----|

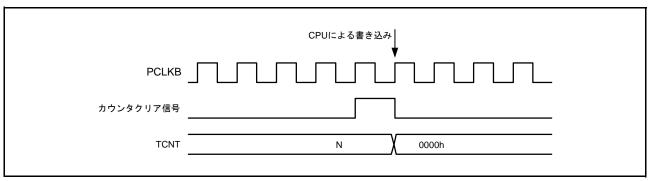

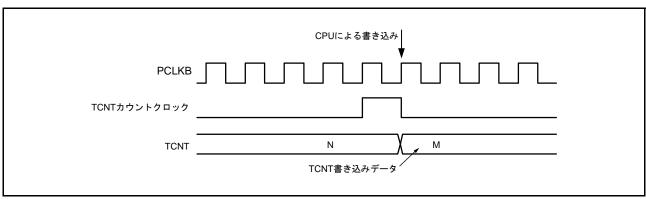

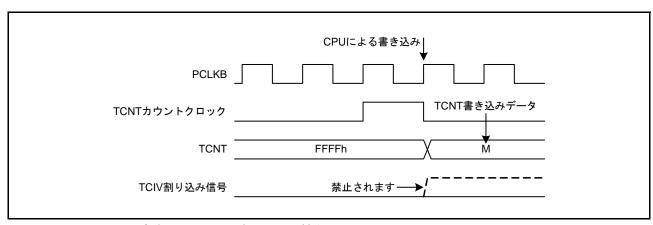

| 19.6.4   | TCNT への書き込みとクリアの競合                                     | 500 |

| 19.6.5   | TCNT への書き込みとカウントアップの競合                                 | 500 |

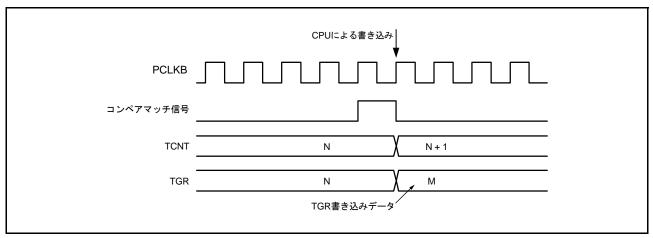

| 19.6.6   | TGR レジスタへの書き込みとコンペアマッチの競合                              | 501 |

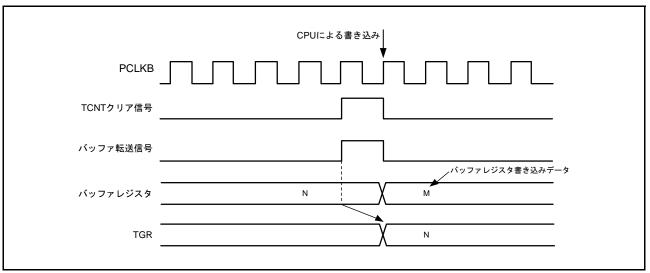

| 19.6.7   | バッファレジスタへの書き込みとコンペアマッチの競合                              | 501 |

| 19.6.8   | バッファレジスタへの書き込みと TCNT クリアの競合                            | 502 |

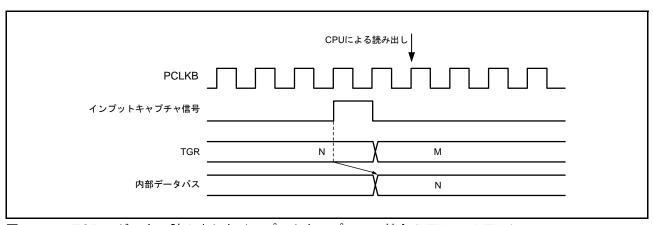

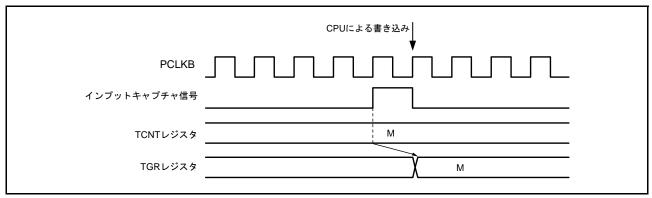

| 19.6.9   | TGR レジスタの読み出しとインプットキャプチャの競合                            | 502 |

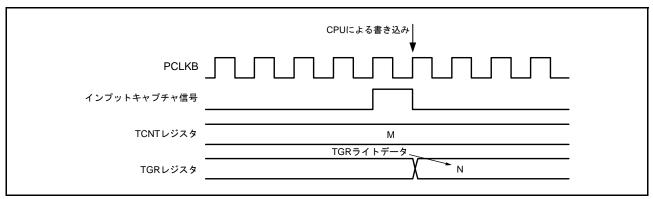

| 19.6.10  | TGR レジスタへの書き込みとインプットキャプチャの競合                           | 503 |

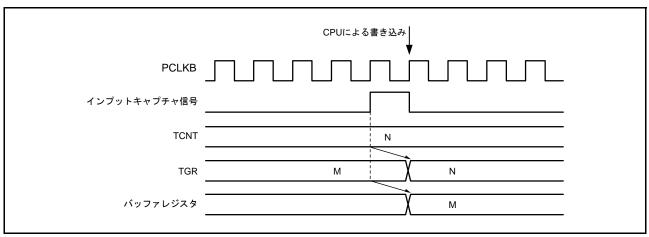

| 19.6.11  | バッファレジスタへの書き込みとインプットキャプチャの競合                           | 504 |

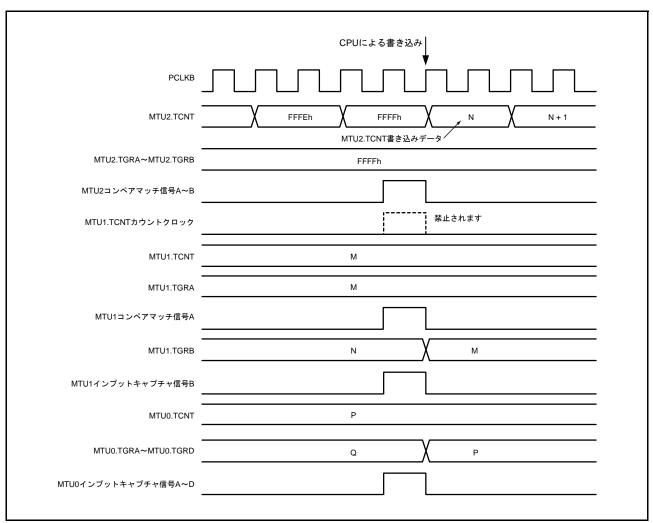

| 19.6.12  | カスケード接続における MTU2.TCNT への書き込みとオーバフロー /<br>アンダフローの競合     | 505 |

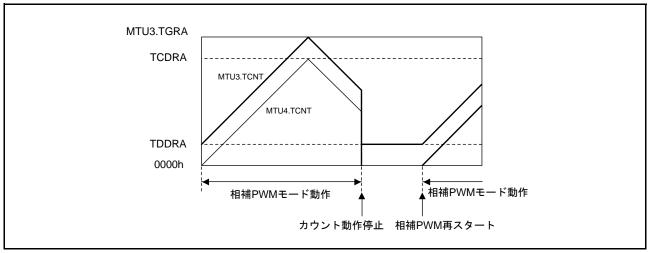

| 19.6.13  | 相補 PWM モードでのカウント動作停止時のカウンタ値                            | 506 |

| 19.6.14  | 相補 PWM モードでのバッファ動作の設定                                  | 506 |

| 19.6.15  | リセット同期 PWM モードのバッファ動作とコンペアマッチ                          | 507 |

| 19.6.16  | リセット同期 PWM モードのオーバフロー                                  | 508 |

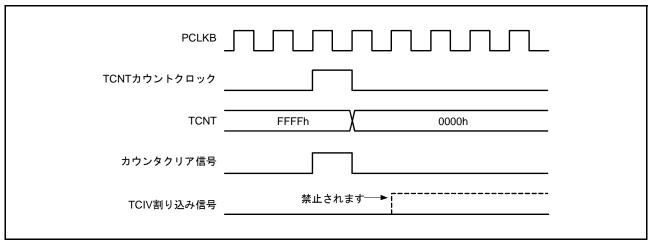

| 19.6.17  | オーバフロー / アンダフローとカウンタクリアの競合                             | 509 |

| 19.6.18  | TCNT への書き込みとオーバフロー / アンダフローの競合                         | 509 |

| 19.6.19  | ノーマルモードまたは PWM モード 1 からリセット同期 PWM モードへ遷移する<br>場合の注意事項  |     |

| 19.6.20  | 相補 PWM モード、リセット同期 PWM モードの出力レベル                        | 510 |

| 19.6.21  | カスケード接続における MTU1.TCNT、MTU2.TCNT 同時インプットキャプチャ           | 510 |

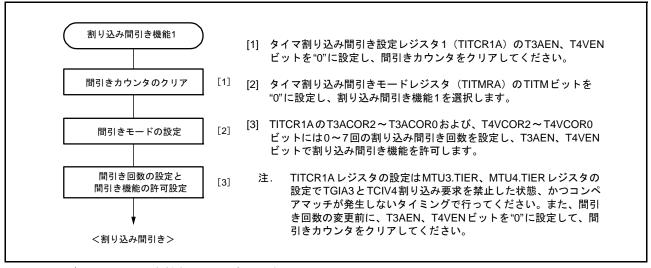

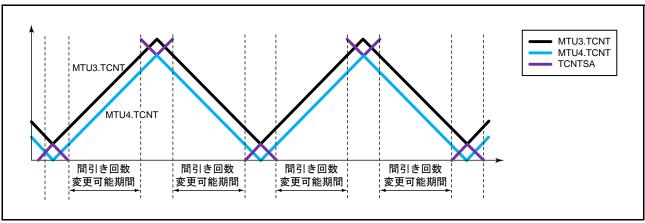

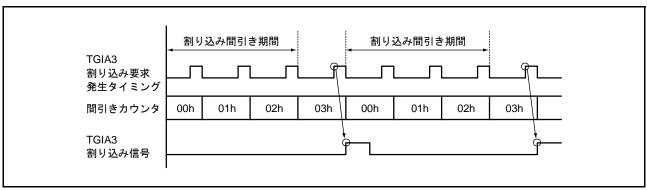

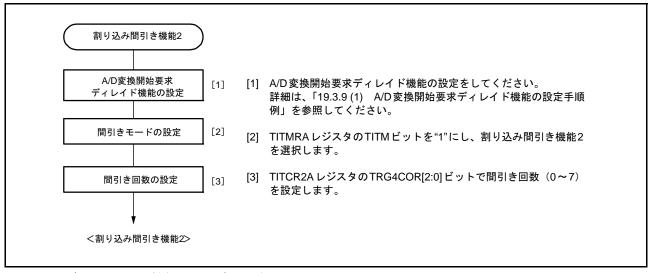

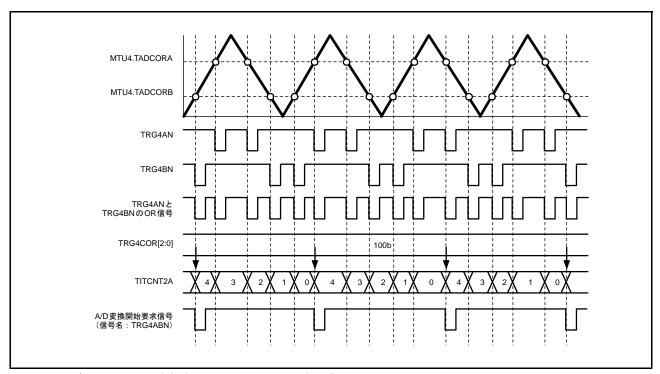

| 19.6.22  | 割り込み間引き機能 2                                            | 511 |

| 19.6.23  | 相補 PWM モードの出力保護機能未使用時の注意事項                             | 511 |

| 19.6.24  | タイマカウンタ (MTU5.TCNT) とタイマジェネラルレジスタ (MTU5.TGR) の<br>注意事項 | 511 |

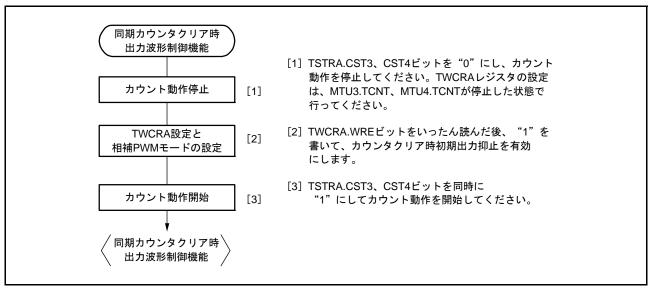

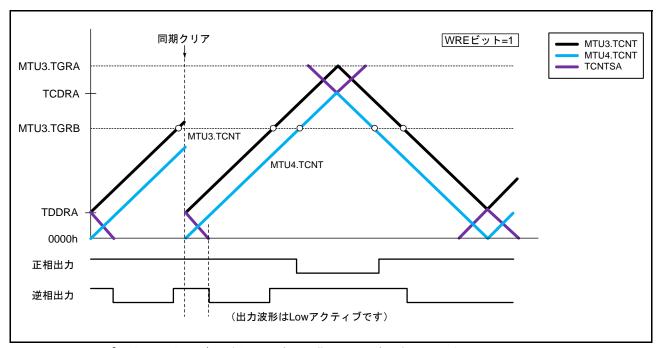

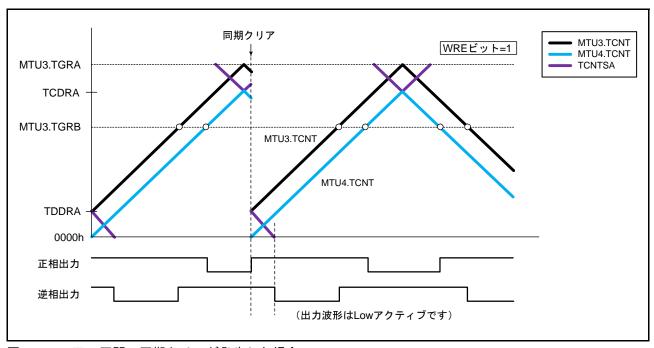

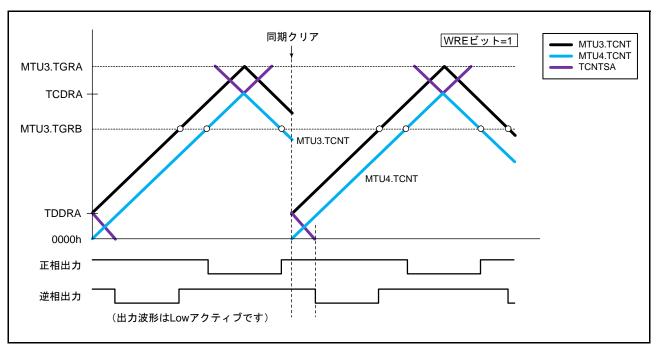

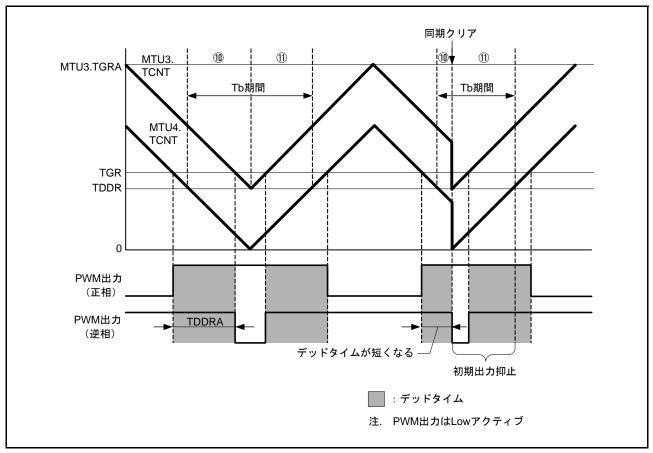

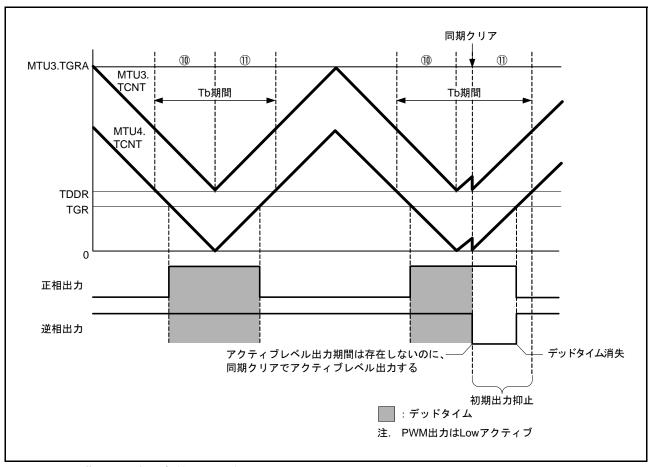

| 19.6.25  | 相補 PWM モード同期クリアするときの異常動作防止の注意事項                        | 512 |

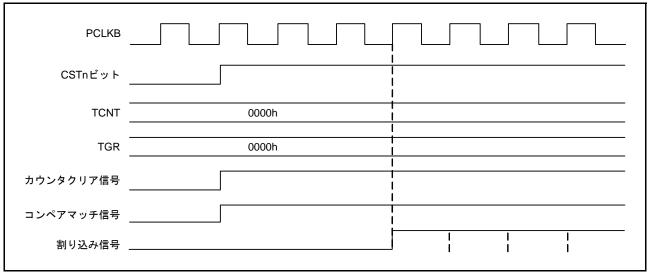

| 19.6.26  | コンペアマッチによる割り込み信号の連続出力                                  | 514 |

| 19.6.27  | 相補 PWM モードにおける A/D 変換ディレイド機能の注意事項                      | 514 |

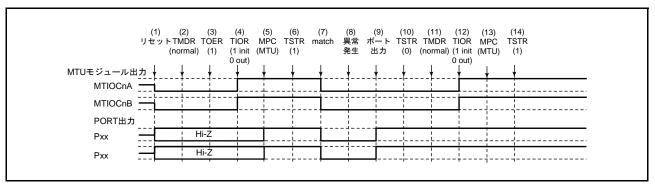

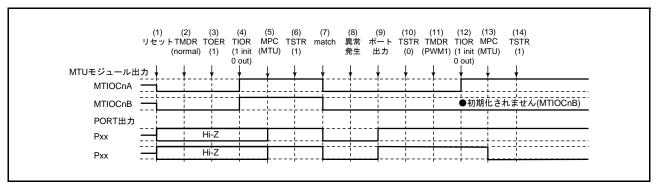

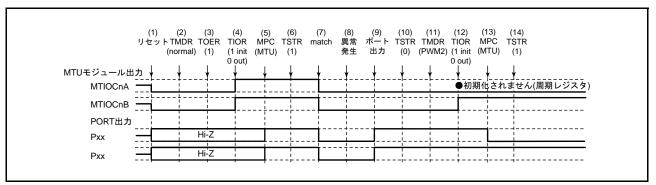

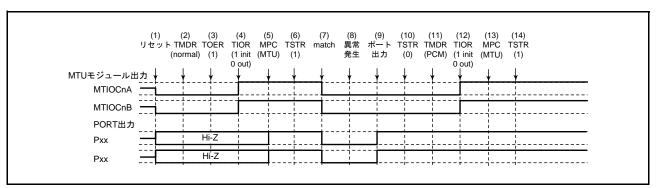

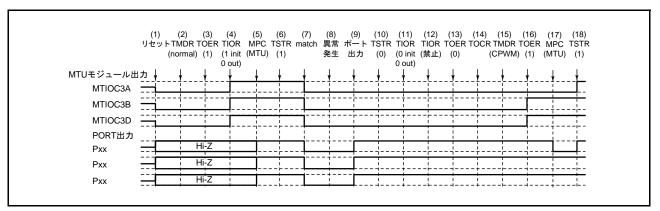

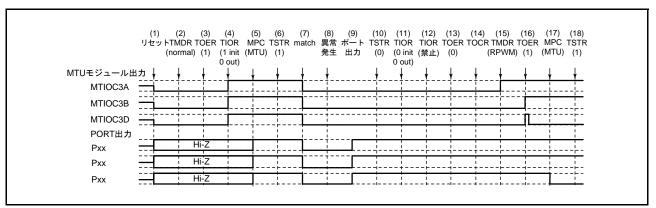

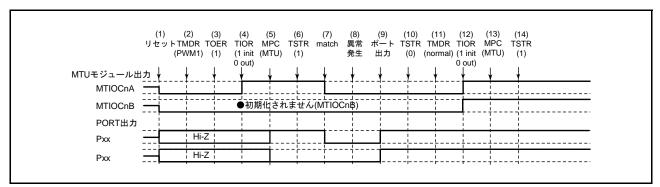

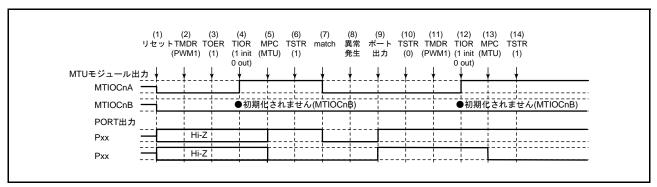

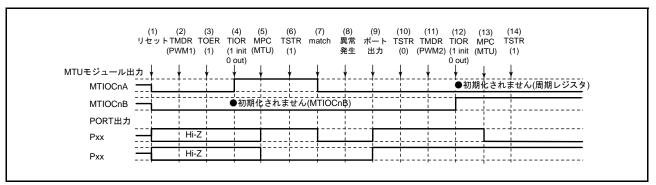

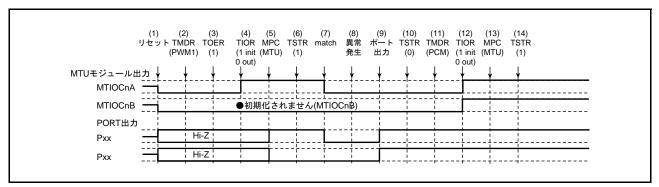

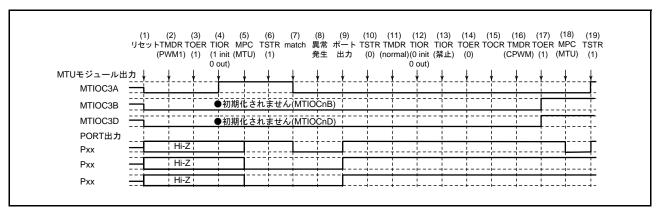

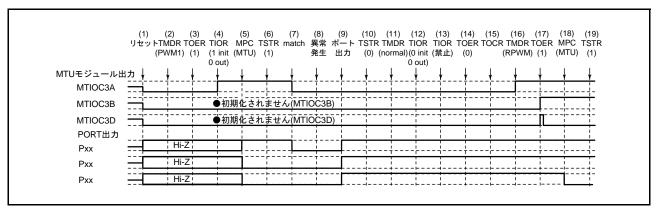

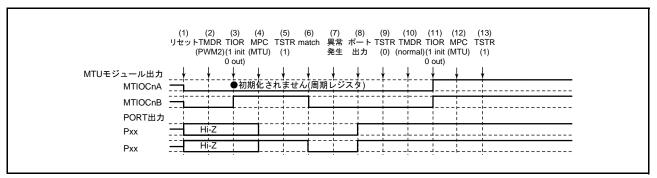

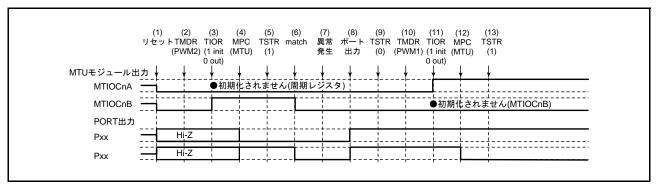

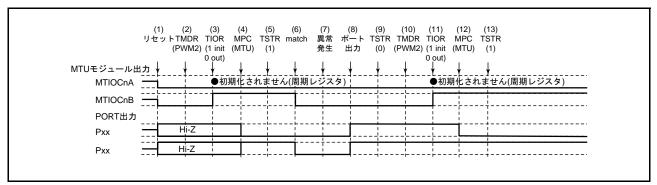

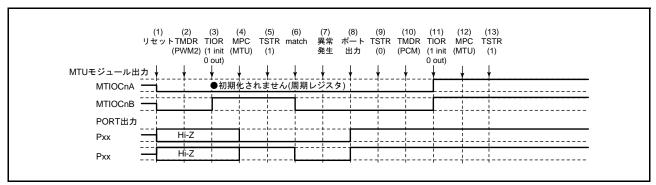

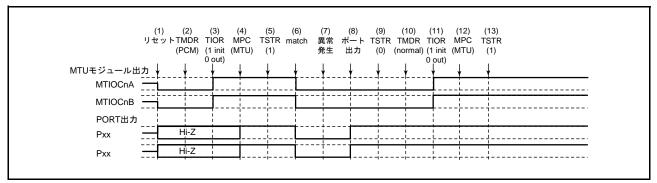

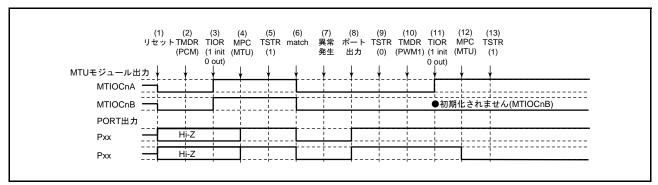

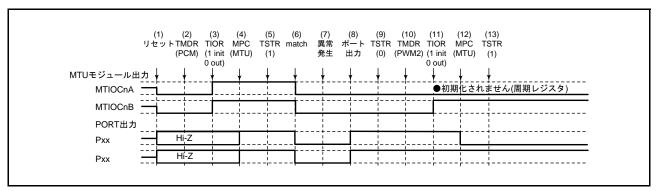

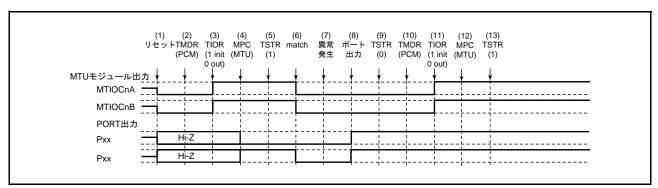

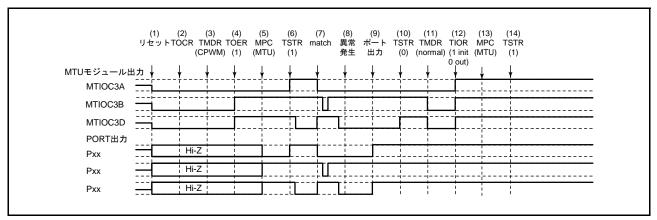

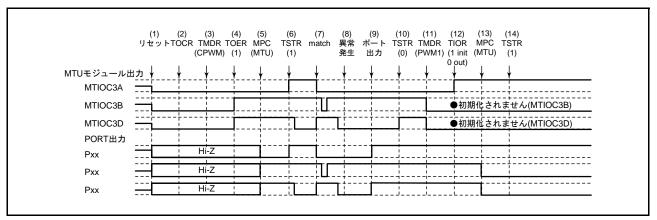

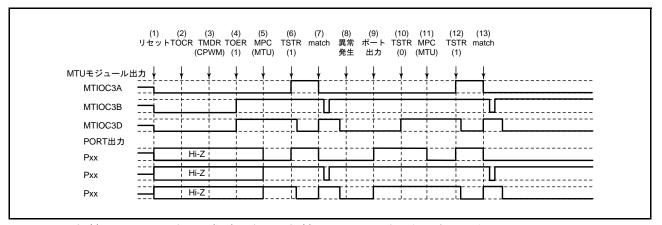

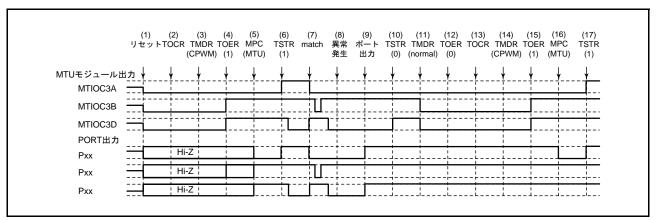

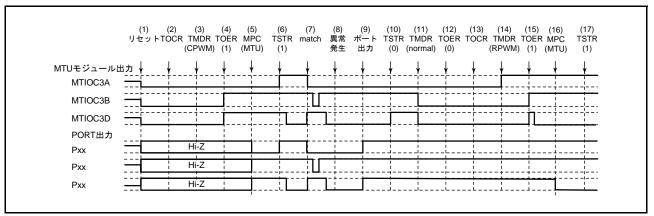

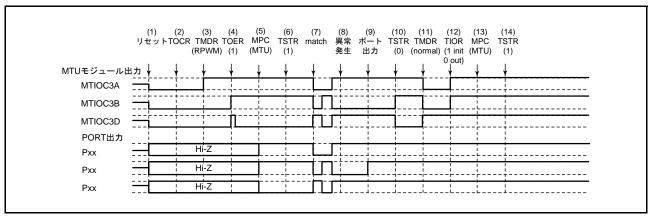

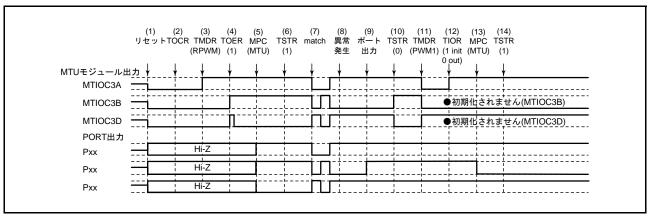

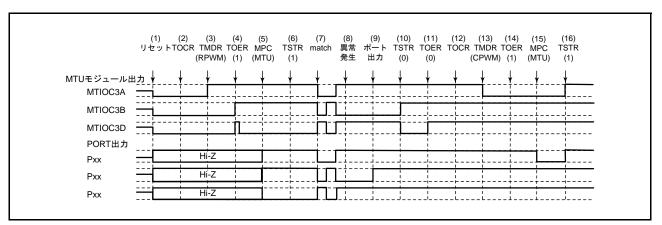

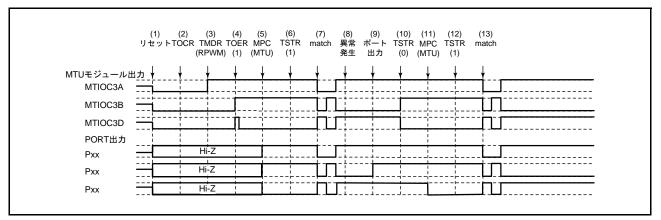

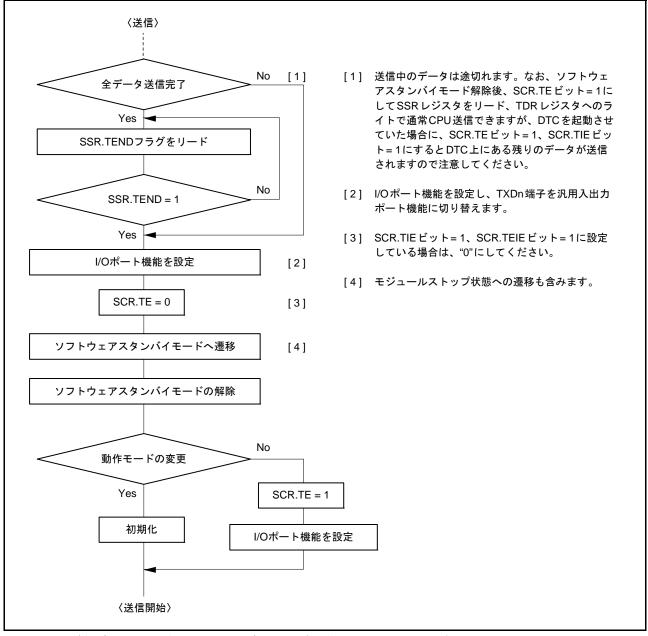

| 19.7 M   | TU 出力端子の初期化方法                                          | 516 |

| 19.7.1   | 動作モード                                                  | 516 |

| 19.7.2   | 動作中の異常などによる再設定時の動作                                     | 516 |

| 19.7.3   | 動作中の異常などによる端子の初期化手順、モード移行の概要                           | 517 |

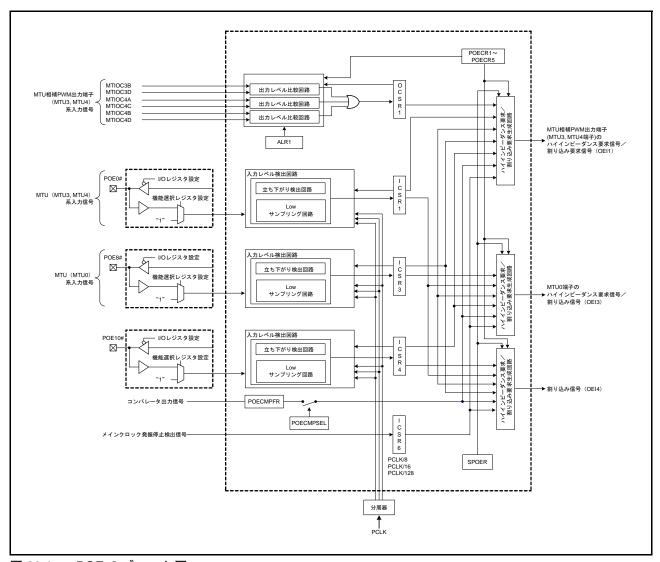

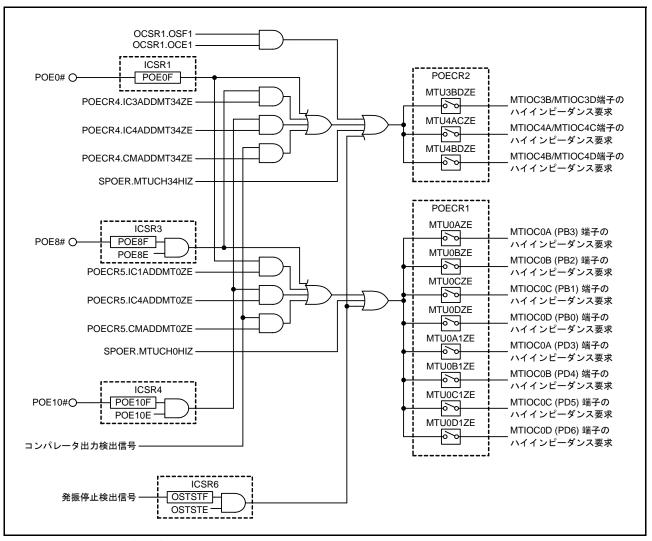

| 20. ポートア | 'ウトプットイネーブル 3 (POE3C)                                  | 547 |

| 20.1 概   | 要                                                      | 547 |

| 20.2 V   | ジスタの説明                                                 | 550 |

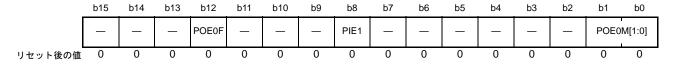

| 20.2.1   | 入力レベルコントロール/ステータスレジスタ 1 (ICSR1)                        | 550 |

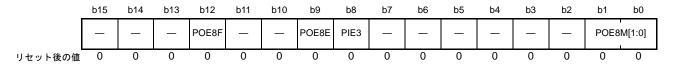

| 20.2.2   | 入力レベルコントロール / ステータスレジスタ 3 (ICSR3)                      |     |

| 20.2.3   | 入力レベルコントロール / ステータスレジスタ 4 (ICSR4)                      |     |

| 20.2.4   | 入力レベルコントロール / ステータスレジスタ 6 (ICSR6)                      |     |

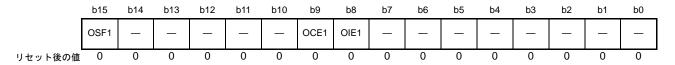

| 20.2.5   | 出力レベルコントロール / ステータスレジスタ 1 (OCSR1)                      | 554 |

| 20.2.6   | アクティブレベルレジスタ 1 (ALR1)                                  | 555 |

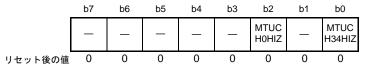

|    | 20.2.7   | ソフトウェアポートアウトプットイネーブルレジスタ (SPOER)              | 557 |

|----|----------|-----------------------------------------------|-----|

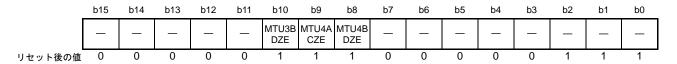

|    | 20.2.8   | ポートアウトプットイネーブルコントロールレジスタ 1 (POECR1)           | 558 |

|    | 20.2.9   | ポートアウトプットイネーブルコントロールレジスタ 2 (POECR2)           | 560 |

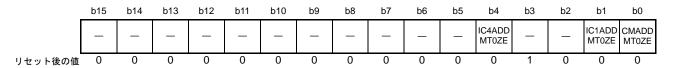

|    | 20.2.10  | ポートアウトプットイネーブルコントロールレジスタ 4 (POECR4)           | 561 |

|    | 20.2.11  | ポートアウトプットイネーブルコントロールレジスタ 5 (POECR5)           | 562 |

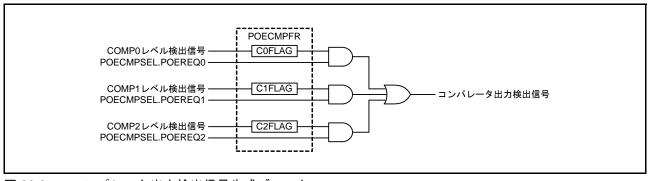

|    | 20.2.12  | ポートアウトプットイネーブルコンパレータ出力検出フラグレジスタ<br>(POECMPFR) | 563 |

|    | 20.2.13  | ポートアウトプットイネーブルコンパレータ要求選択レジスタ (POECMPSEL)      | 564 |

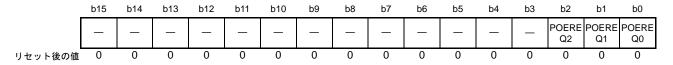

|    | 20.3 動作  | =説明                                           | 565 |

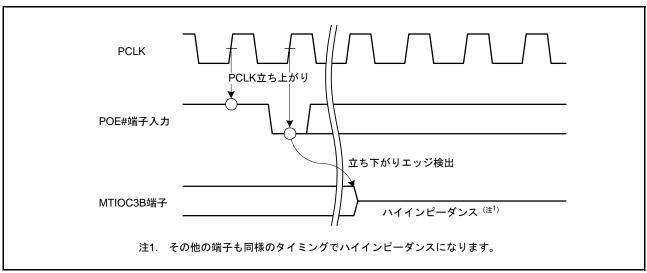

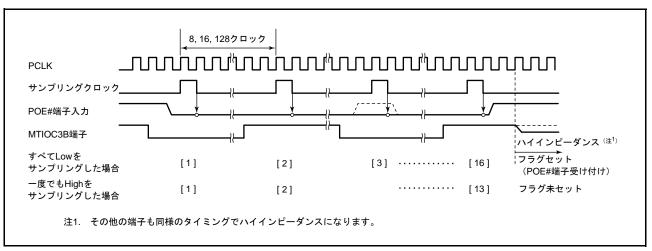

|    | 20.3.1   | 入力レベル検出動作                                     | 572 |

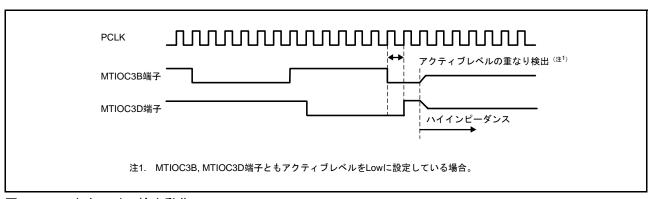

|    | 20.3.2   | 出力レベル比較動作                                     | 573 |

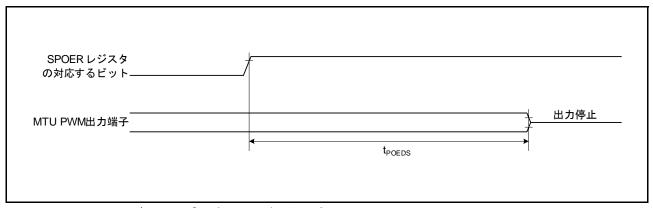

|    | 20.3.3   | レジスタによるハイインピーダンス制御                            | 574 |

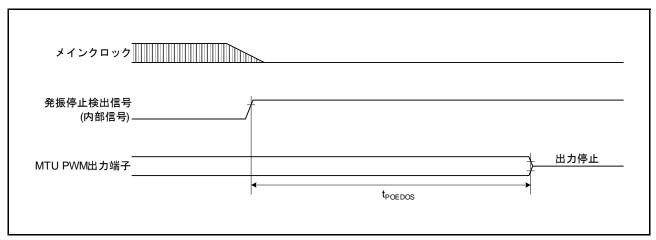

|    | 20.3.4   | 発振停止検出検知によるハイインピーダンス制御                        | 574 |

|    | 20.3.5   | コンパレータ出力検出によるハイインピーダンス制御                      | 574 |

|    | 20.3.6   | ハイインピーダンス制御条件の追加機能                            | 574 |

|    | 20.3.7   | ハイインピーダンス状態の解除                                | 574 |

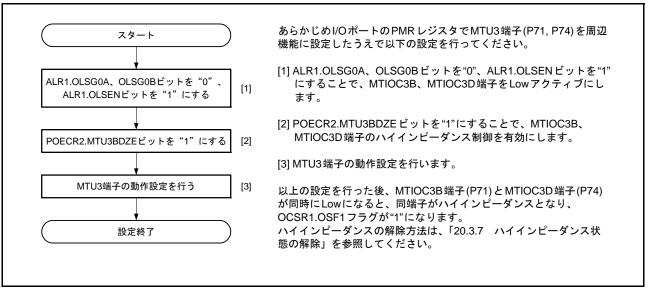

|    | 20.4 POE | 3 設定手順                                        | 576 |

|    | 20.5 割り  | 込み                                            | 576 |

|    | 20.6 使用  | 上の注意事項                                        | 577 |

|    | 20.6.1   | 低消費電力モードへの遷移                                  | 577 |

|    | 20.6.2   | MTU 端子非選択時のハイインピーダンス制御                        | 577 |

|    | 20.6.3   | POE を使用しない場合について                              | 577 |

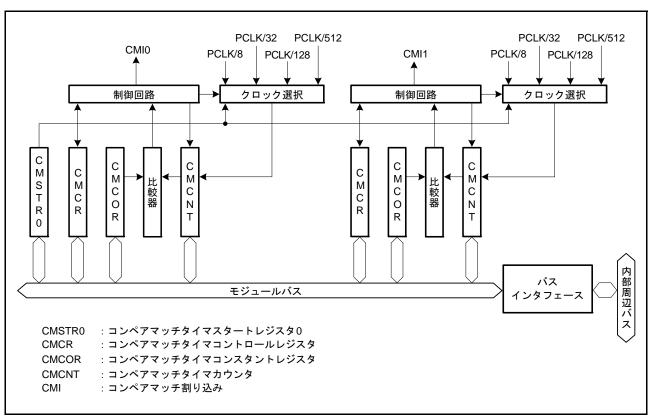

| 21 | . コンペアマ  | マッチタイマ (CMT)                                  | 578 |

|    | 21.1 概要  | · · · · · · · · · · · · · · · · · · ·         | 578 |

|    | 21.2 レジ  | ジスタの説明                                        | 579 |

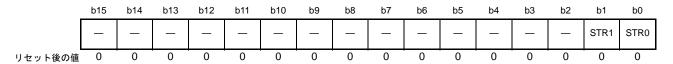

|    | 21.2.1   | コンペアマッチタイマスタートレジスタ 0 (CMSTR0)                 | 579 |

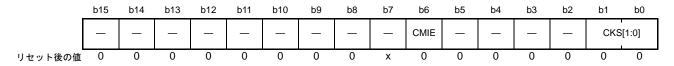

|    | 21.2.2   | コンペアマッチタイマコントロールレジスタ (CMCR)                   | 580 |

|    | 21.2.3   | コンペアマッチタイマカウンタ (CMCNT)                        | 581 |

|    | 21.2.4   | コンペアマッチタイマコンスタントレジスタ (CMCOR)                  | 581 |

|    | 21.3 動作  | =説明                                           | 582 |

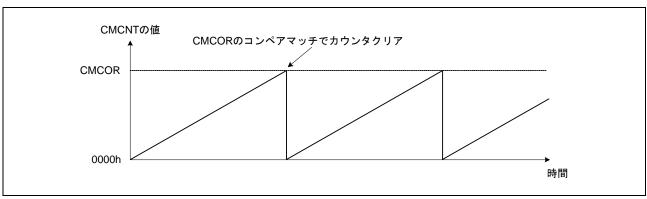

|    | 21.3.1   | 周期カウント動作                                      | 582 |

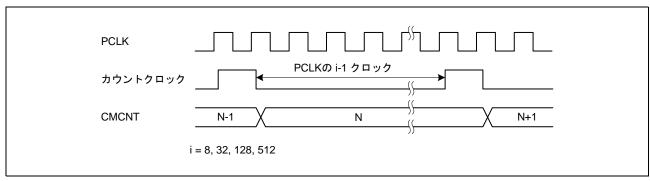

|    | 21.3.2   | CMCNT カウンタのカウントタイミング                          | 582 |

|    | 21.4 割り  | 込み                                            | 583 |

|    | 21.4.1   | 割り込み要因                                        | 583 |

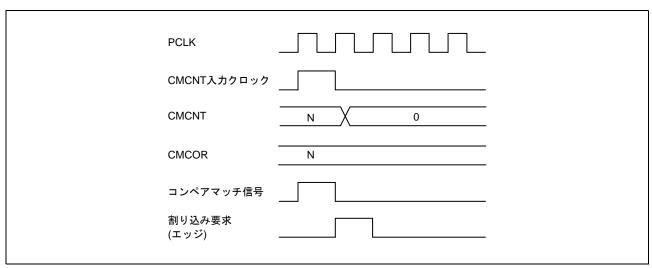

|    | 21.4.2   | コンペアマッチ割り込みの発生タイミング                           | 583 |

|    | 21.5 使用  | 上の注意事項                                        | 584 |

|    | 21.5.1   | モジュールストップ機能の設定                                | 584 |

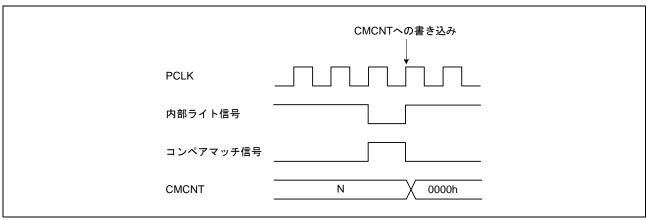

|    | 21.5.2   | CMCNT カウンタへの書き込みとコンペアマッチの競合                   | 584 |

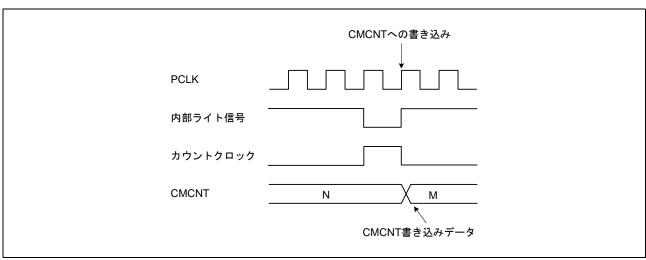

|    | 21.5.3   | CMCNT カウンタへの書き込みとカウントアップの競合                   | 584 |

|    |          |                                               |     |

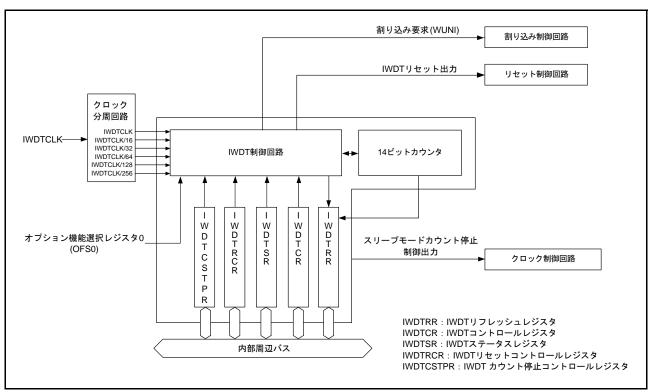

| 22. | 独立ウォ    | ッチドッグタイマ (IWDTa)                              | 585 |

|-----|---------|-----------------------------------------------|-----|

|     | 22.1 概要 | ₹                                             | 585 |

|     | 22.2 レミ | ジスタの説明                                        | 587 |

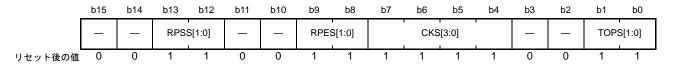

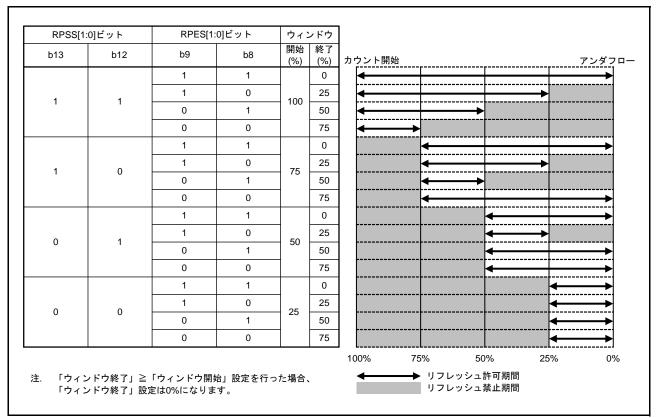

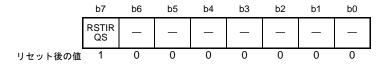

|     | 22.2.1  | IWDT リフレッシュレジスタ (IWDTRR)                      | 587 |

|     | 22.2.2  | IWDT コントロールレジスタ (IWDTCR)                      | 588 |

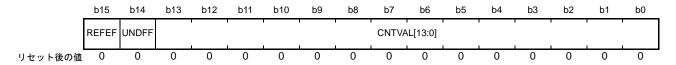

|     | 22.2.3  | IWDT ステータスレジスタ (IWDTSR)                       | 591 |

|     | 22.2.4  | IWDT リセットコントロールレジスタ (IWDTRCR)                 | 592 |

|     | 22.2.5  | IWDT カウント停止コントロールレジスタ (IWDTCSTPR)             | 593 |

|     | 22.2.6  | オプション機能選択レジスタ 0 (OFS0)                        | 593 |

|     | 22.3 動作 | 乍説明                                           | 594 |

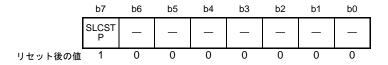

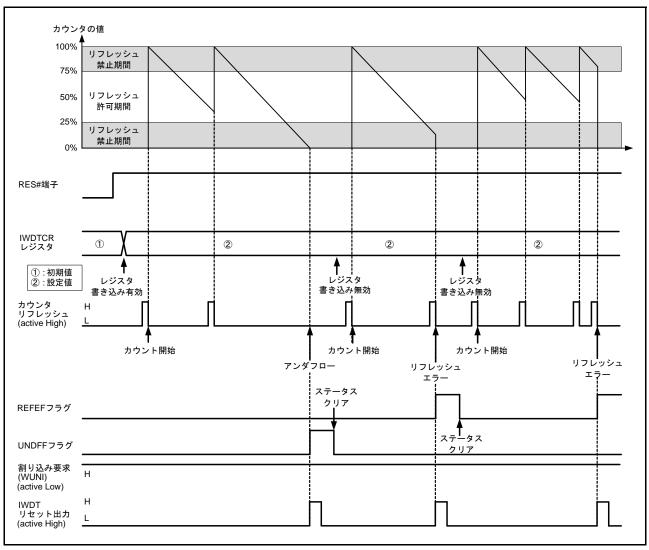

|     | 22.3.1  | カウント開始条件別の各動作                                 | 594 |

|     | 22.3.1  | 1 レジスタスタートモード                                 | 594 |

|     | 22.3.1  | 2 オートスタートモード                                  | 596 |

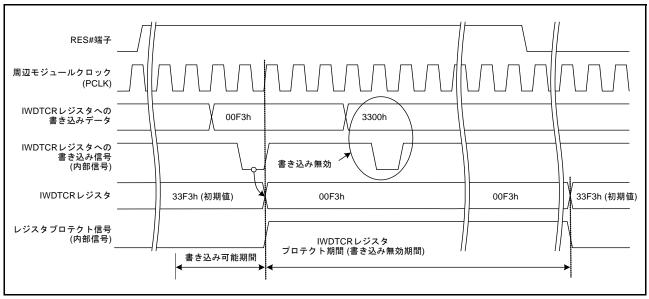

|     | 22.3.2  | IWDTCR レジスタ、IWDTRCR レジスタ、IWDTCSTPR レジスタ書き込み制御 | 598 |

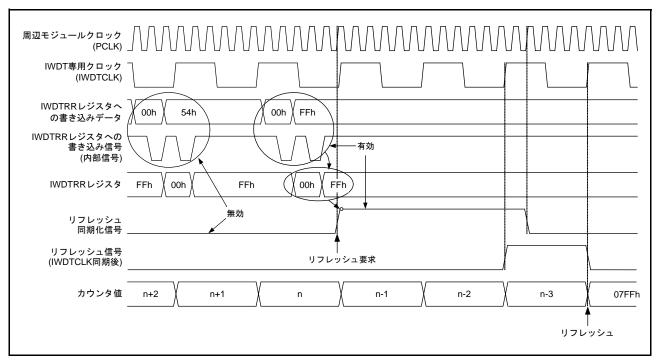

|     | 22.3.3  | リフレッシュ動作                                      | 599 |

|     | 22.3.4  | ステータスフラグ                                      | 601 |

|     | 22.3.5  | リセット出力                                        | 601 |

|     | 22.3.6  | 割り込み要因                                        | 601 |

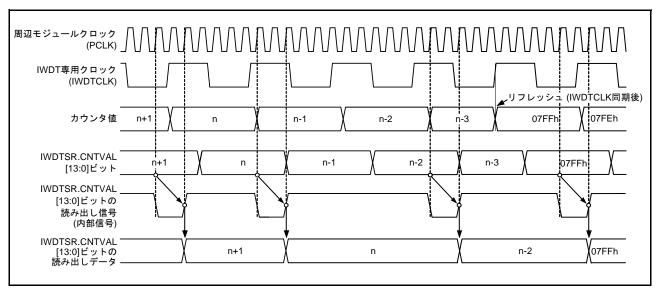

|     | 22.3.7  | カウンタ値の読み出し                                    | 602 |

|     | 22.3.8  | オプション機能選択レジスタ 0 (OFS0) と IWDT レジスタの対応         | 603 |

|     | 22.4 使月 | 月上の注意事項                                       | 603 |

|     | 22.4.1  | リフレッシュ動作について                                  | 603 |

|     | 22.4.2  | クロック分周比の設定                                    | 603 |

| 23. | シリアル:   | コミュニケーションインタフェース (SCIg, SCIh)                 | 604 |

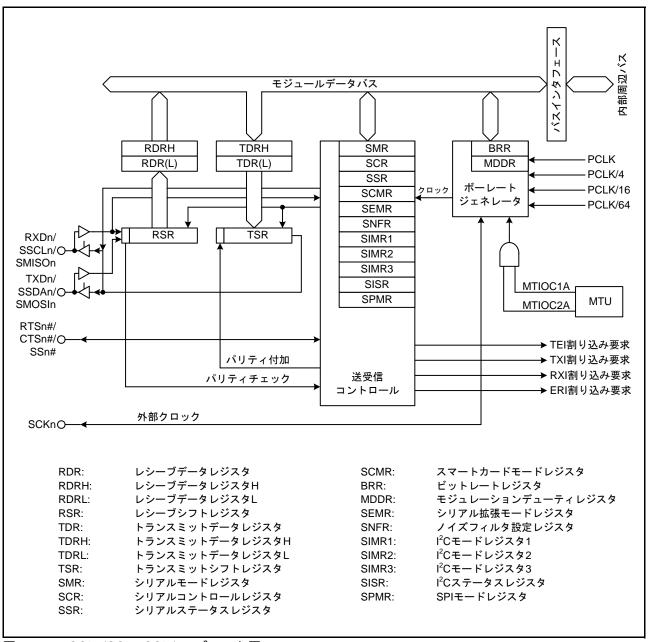

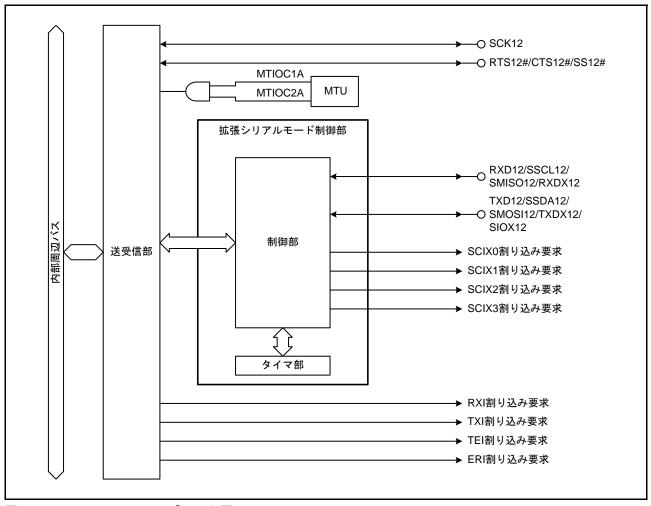

|     | 23.1 概要 | 포                                             | 604 |

|     | 23.2 レミ | ジスタの説明                                        | 610 |

|     | 23.2.1  | レシーブシフトレジスタ (RSR)                             | 610 |

|     | 23.2.2  | レシーブデータレジスタ (RDR)                             | 610 |

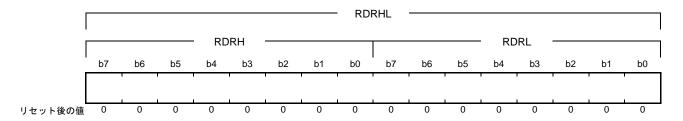

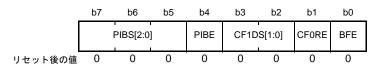

|     | 23.2.3  | レシーブデータレジスタ H、L、HL (RDRH, RDRL, RDRHL)        | 611 |

|     | 23.2.4  | トランスミットデータレジスタ (TDR)                          | 612 |

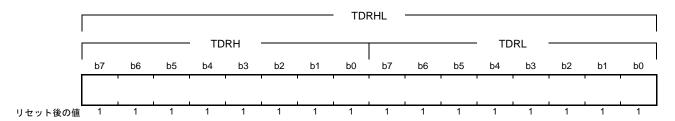

|     | 23.2.5  | トランスミットデータレジスタ H、L、HL (TDRH, TDRL, TDRHL)     | 613 |

|     | 23.2.6  | トランスミットシフトレジスタ (TSR)                          | 613 |

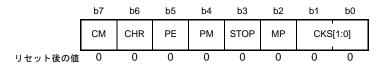

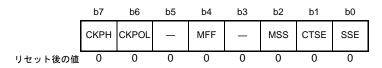

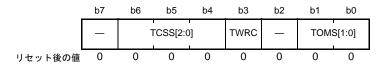

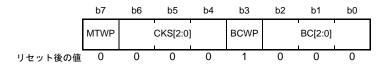

|     | 23.2.7  | シリアルモードレジスタ (SMR)                             | 614 |

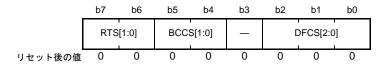

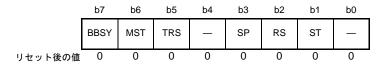

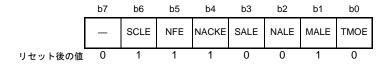

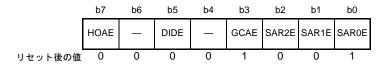

|     | 23.2.8  | シリアルコントロールレジスタ (SCR)                          | 618 |

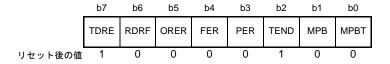

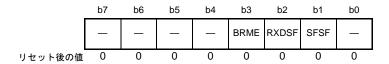

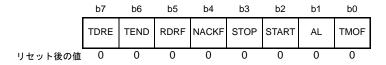

|     | 23.2.9  | シリアルステータスレジスタ (SSR)                           | 622 |

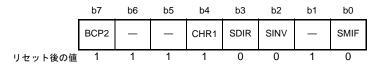

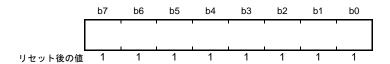

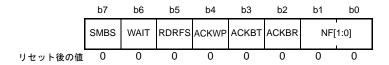

|     | 23.2.10 | スマートカードモードレジスタ (SCMR)                         | 627 |

|     | 23.2.11 | ビットレートレジスタ (BRR)                              | 629 |

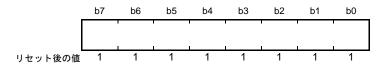

|     | 23.2.12 | モジュレーションデューティレジスタ (MDDR)                      | 636 |

|     | 23.2.13 | シリアル拡張モードレジスタ (SEMR)                          | 637 |

|     | 23.2.14 | ノイズフィルタ設定レジスタ (SNFR)                          | 640 |

| 23.2.15 | I <sup>2</sup> C モードレジスタ 1 (SIMR1)     | 641 |

|---------|----------------------------------------|-----|

| 23.2.16 | I <sup>2</sup> C モードレジスタ 2 (SIMR2)     | 642 |

| 23.2.17 | I <sup>2</sup> C モードレジスタ 3 (SIMR3)     | 643 |

| 23.2.18 | I <sup>2</sup> C ステータスレジスタ (SISR)      | 645 |

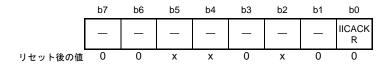

| 23.2.19 | SPI モードレジスタ (SPMR)                     | 646 |

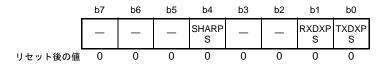

| 23.2.20 | 拡張シリアルモード有効レジスタ (ESMER)                | 647 |

| 23.2.21 | コントロールレジスタ 0 (CR0)                     | 648 |

| 23.2.22 | コントロールレジスタ 1 (CR1)                     | 648 |

| 23.2.23 | コントロールレジスタ 2 (CR2)                     | 649 |

| 23.2.24 | コントロールレジスタ 3 (CR3)                     | 650 |

| 23.2.25 | ポートコントロールレジスタ (PCR)                    | 650 |

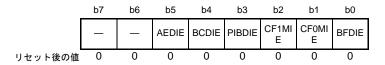

| 23.2.26 | 割り込みコントロールレジスタ (ICR)                   | 651 |

| 23.2.27 | ステータスレジスタ (STR)                        | 652 |

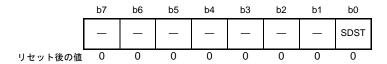

| 23.2.28 | ステータスクリアレジスタ (STCR)                    | 653 |

| 23.2.29 | Control Field 0 データレジスタ (CF0DR)        | 653 |

| 23.2.30 | Control Field 0 コンペアイネーブルレジスタ (CF0CR)  | 654 |

| 23.2.31 | Control Field 0 受信データレジスタ (CF0RR)      | 654 |

| 23.2.32 | プライマリ Control Field 1 データレジスタ (PCF1DR) | 654 |

| 23.2.33 | セカンダリ Control Field 1 データレジスタ (SCF1DR) | 655 |

| 23.2.34 | Control Field 1 コンペアイネーブルレジスタ (CF1CR)  | 655 |

| 23.2.35 | Control Field 1 受信データレジスタ (CF1RR)      | 655 |

| 23.2.36 | タイマコントロールレジスタ (TCR)                    | 656 |

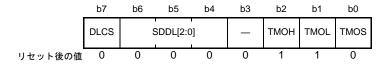

| 23.2.37 | タイマモードレジスタ (TMR)                       | 656 |

| 23.2.38 | タイマプリスケーラレジスタ (TPRE)                   | 657 |

| 23.2.39 | タイマカウントレジスタ (TCNT)                     | 657 |

| 23.3 調  | 歩同期式モードの動作                             | 658 |

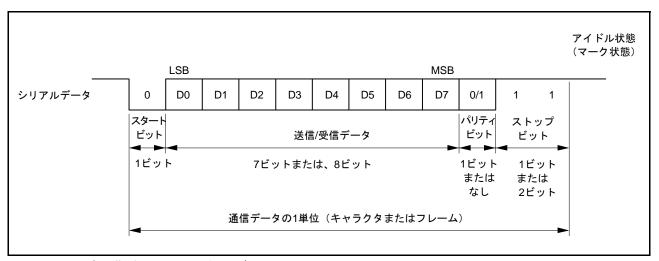

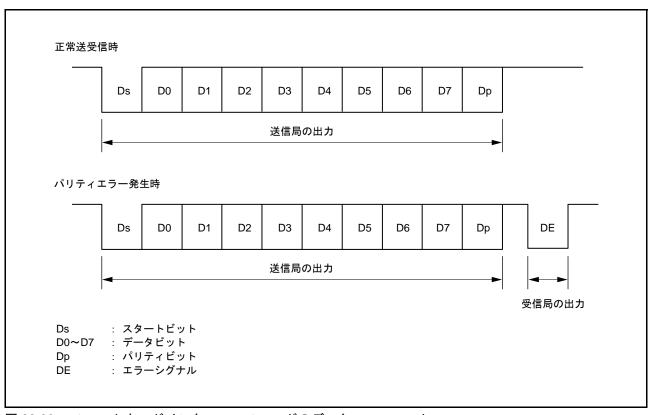

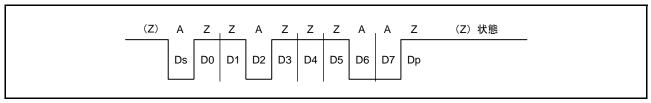

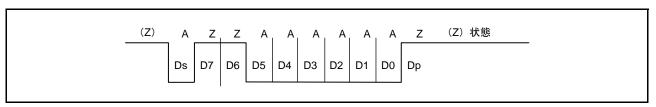

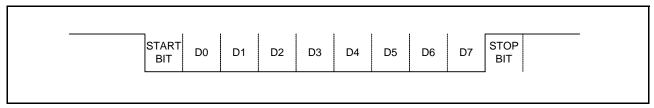

| 23.3.1  | シリアル送信 / 受信フォーマット                      | 658 |

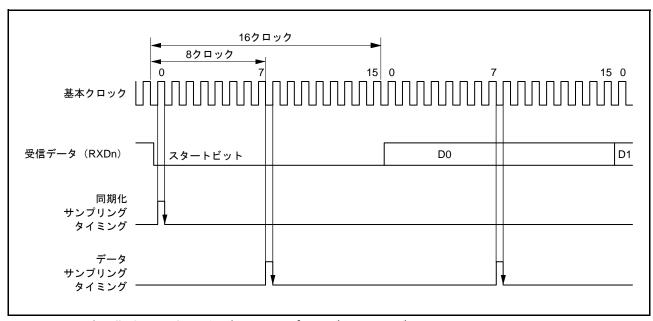

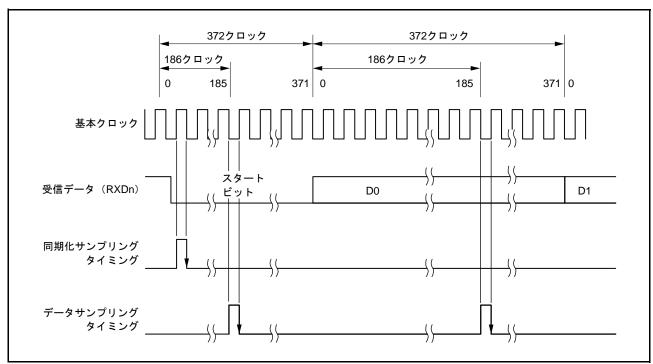

| 23.3.2  | 調歩同期式モードの受信データサンプリングタイミングと受信マージン       | 660 |

| 23.3.3  | クロック                                   | 661 |

| 23.3.4  | 倍速モード                                  | 661 |

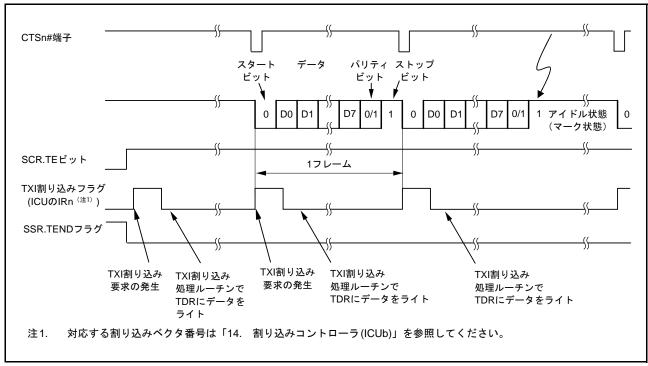

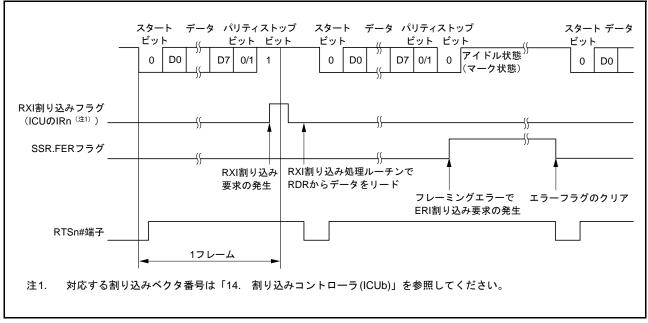

| 23.3.5  | CTS、RTS 機能                             | 662 |

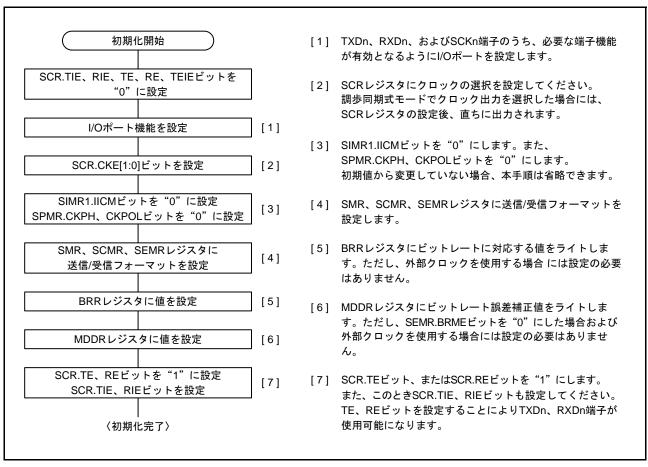

| 23.3.6  | SCI の初期化 (調歩同期式モード)                    | 663 |

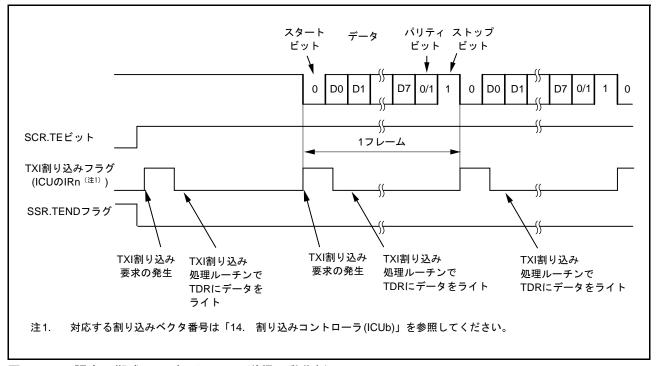

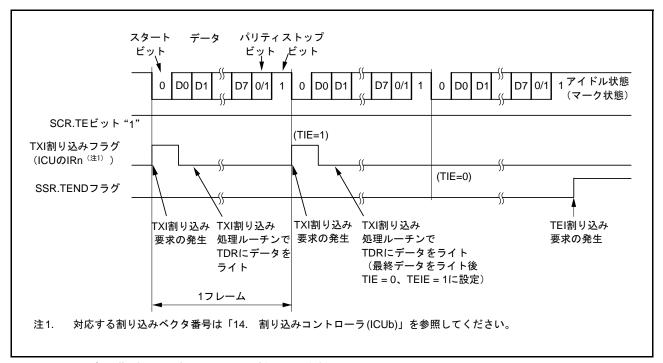

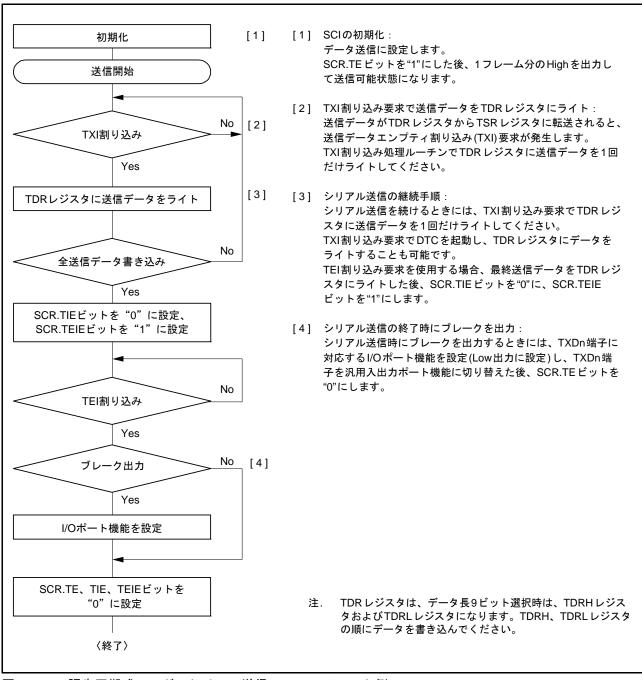

| 23.3.7  | シリアルデータの送信 (調歩同期式モード)                  | 665 |

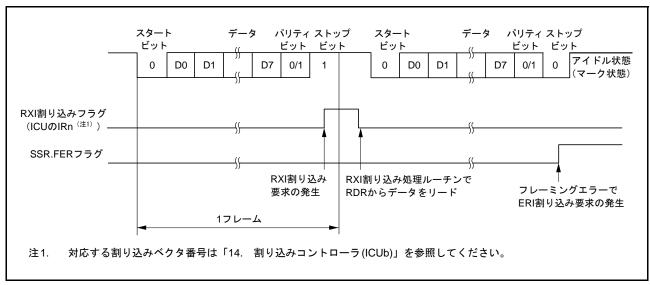

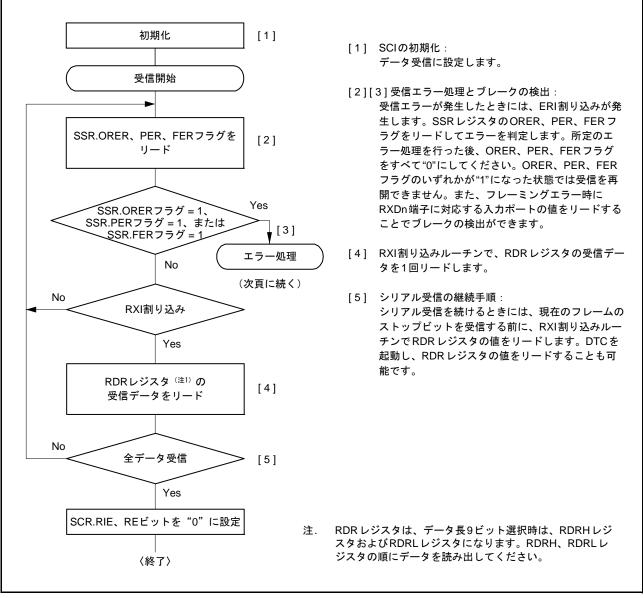

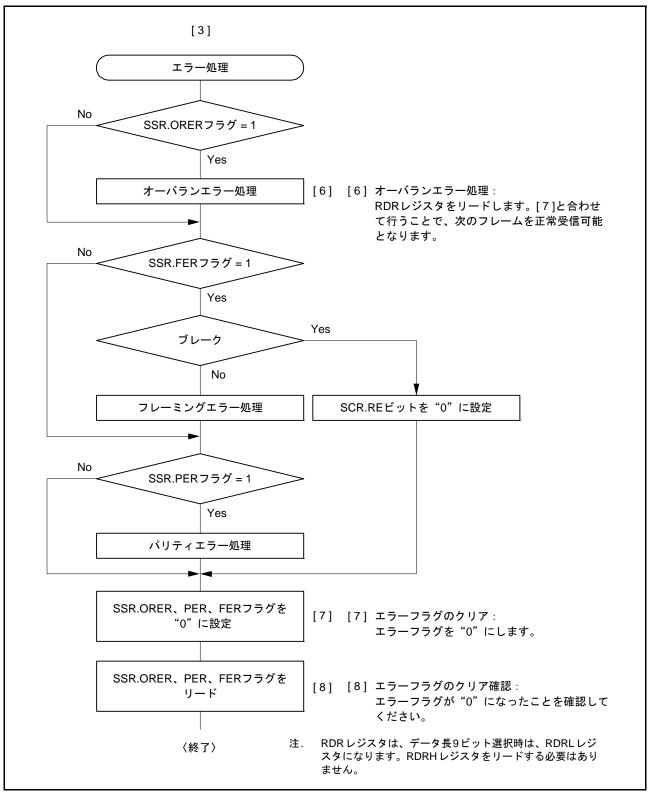

| 23.3.8  | シリアルデータの受信(調歩同期式モード)                   | 669 |

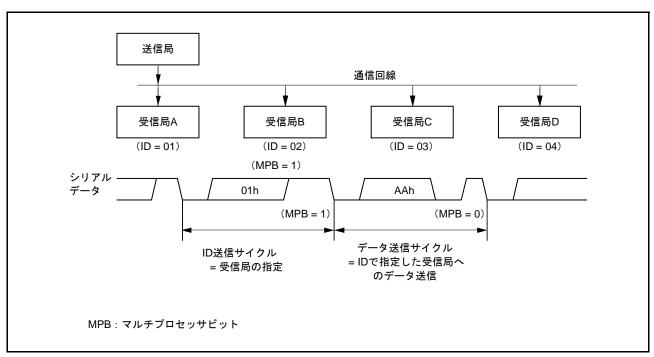

| 23.4    | ルチプロセッサ通信機能                            | 673 |

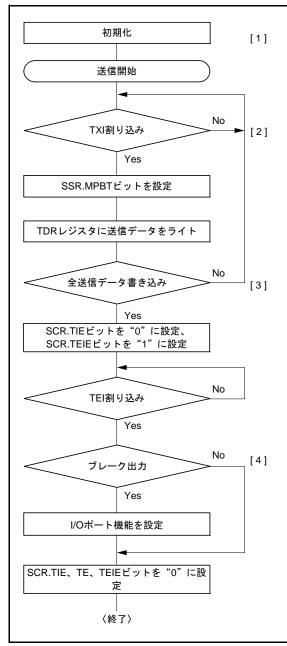

| 23.4.1  | マルチプロセッサシリアルデータ送信                      | 674 |

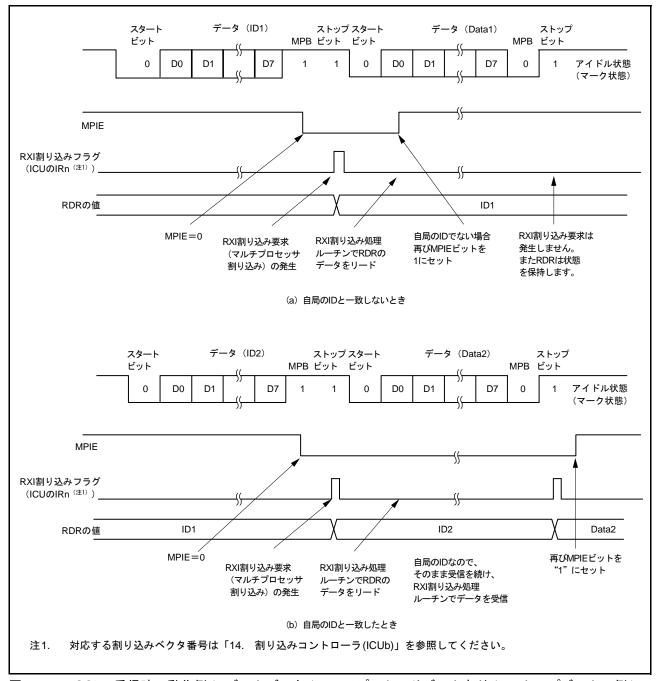

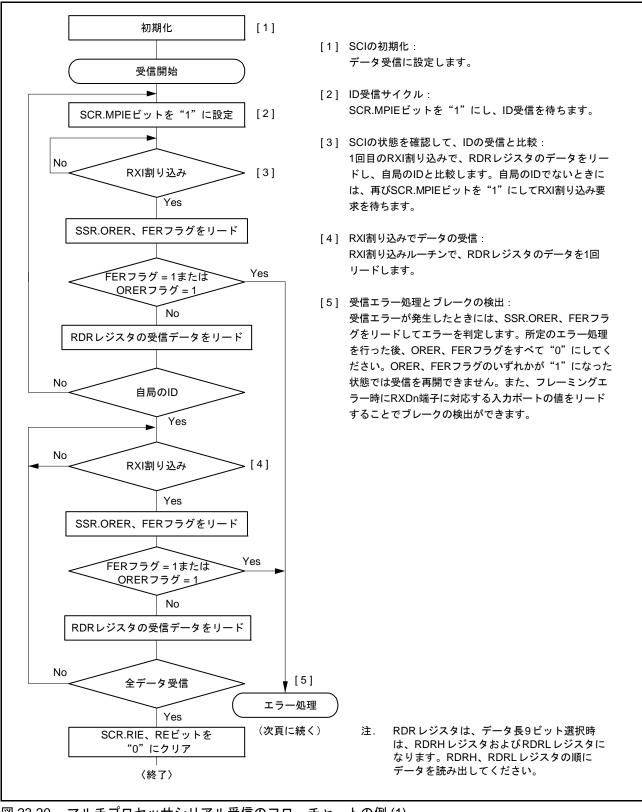

| 23.4.2  | マルチプロセッサシリアルデータ受信                      | 675 |

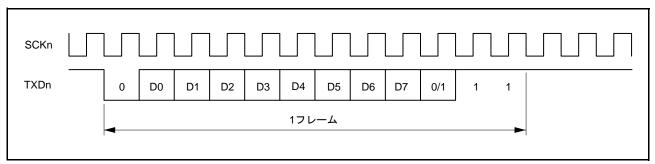

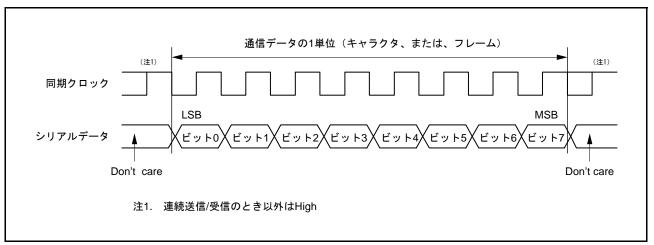

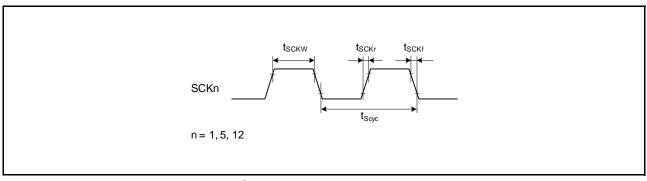

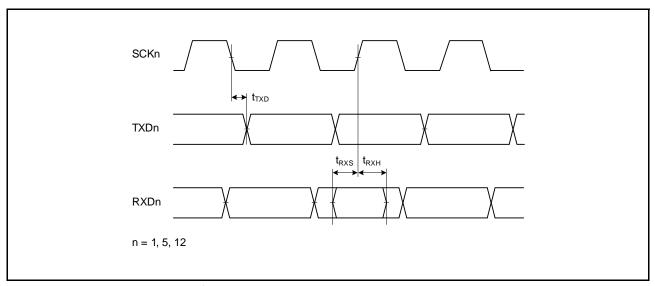

| 23.5 ク  | ロック同期式モードの動作                           | 678 |

| 23.5.1  | クロック                                   | 678 |

| 23.5.2  | CTS、RTS 機能                             | 679 |

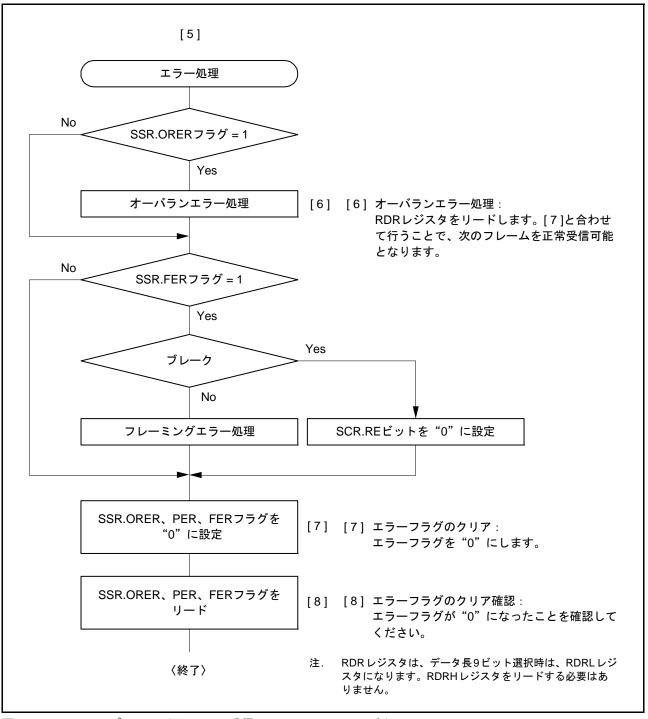

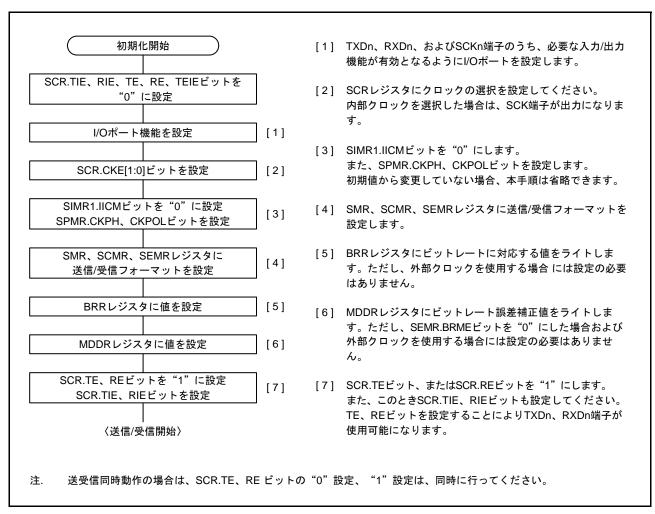

| 23.5.3   | SCI の初期化 (クロック同期式モード)                | 680 |

|----------|--------------------------------------|-----|

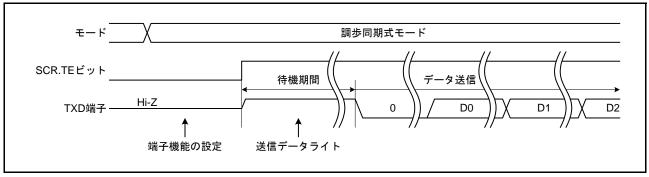

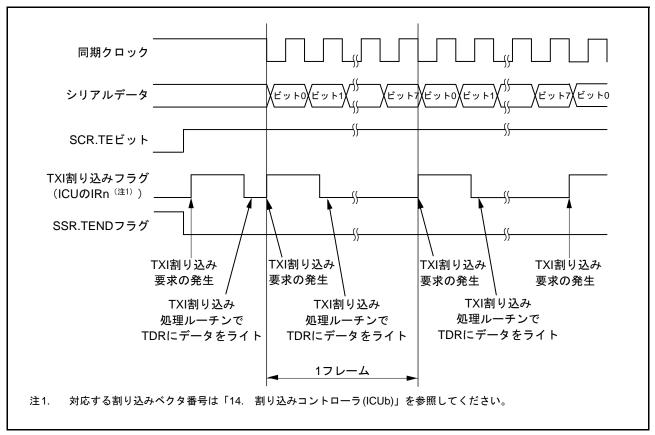

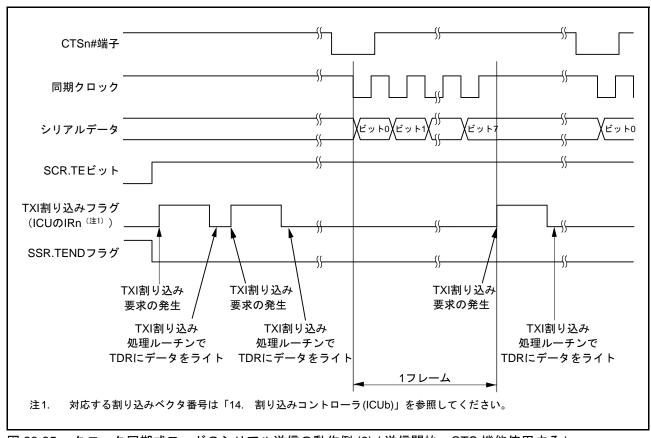

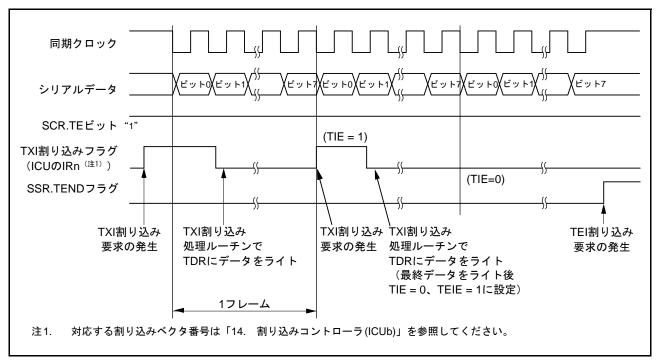

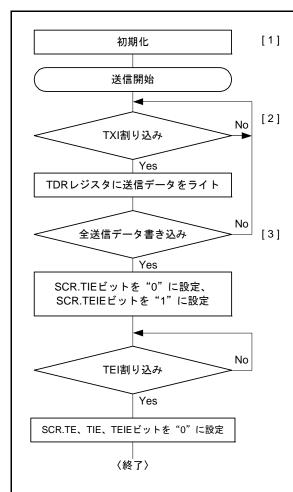

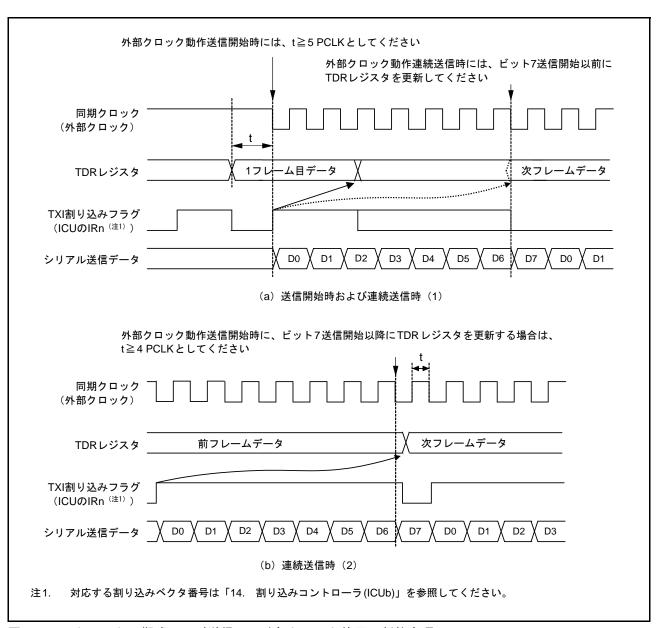

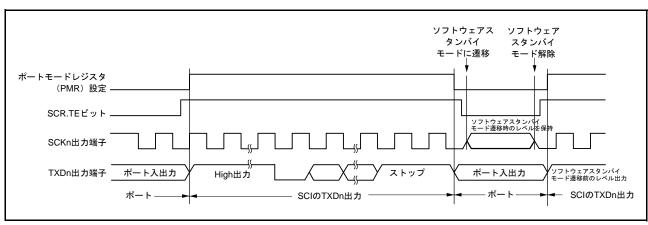

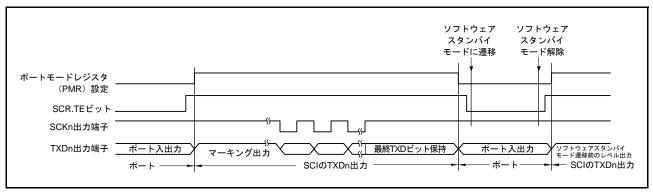

| 23.5.4   | シリアルデータの送信 (クロック同期式モード)              | 681 |

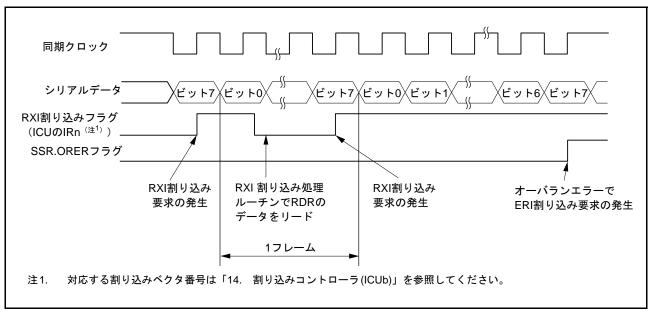

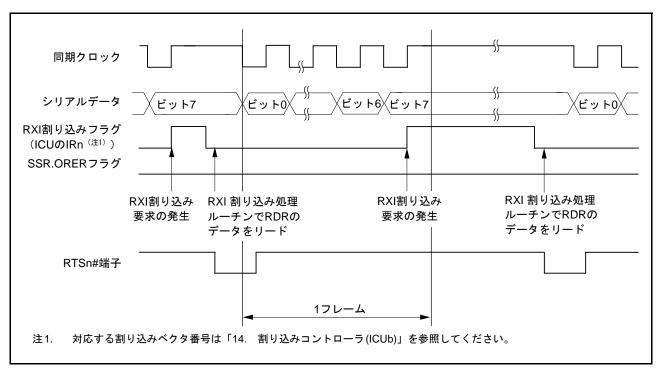

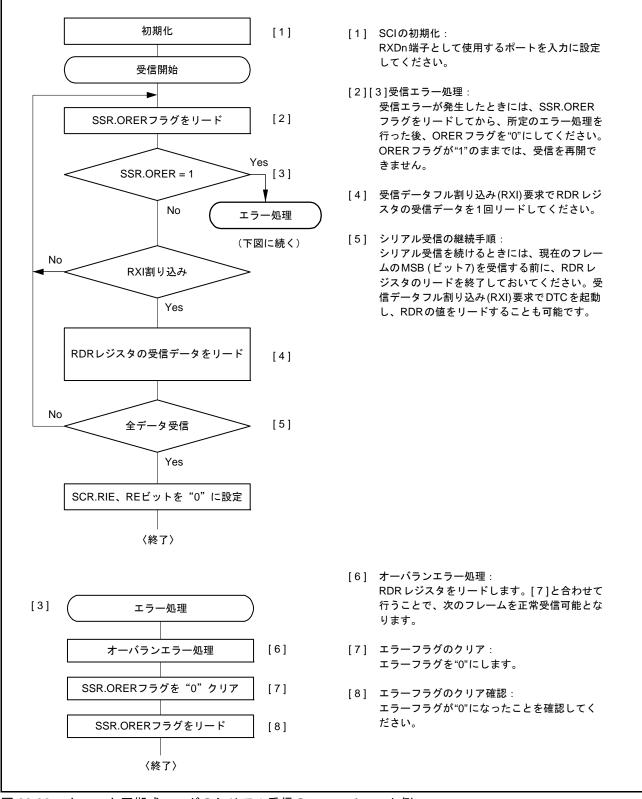

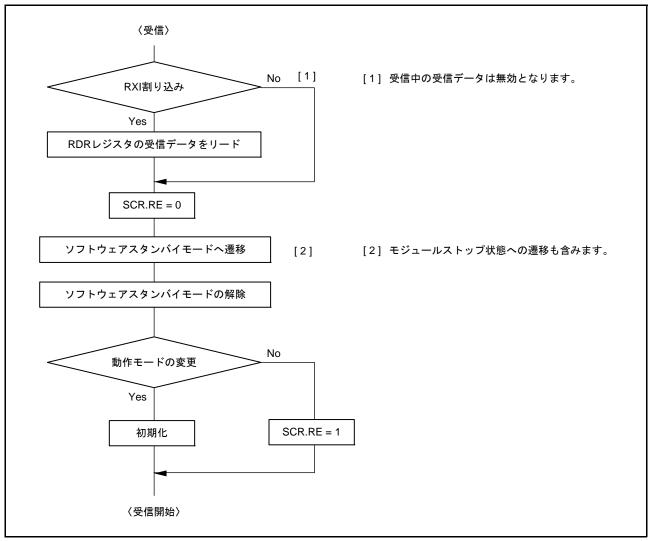

| 23.5.5   | シリアルデータの受信 (クロック同期式モード)              | 685 |

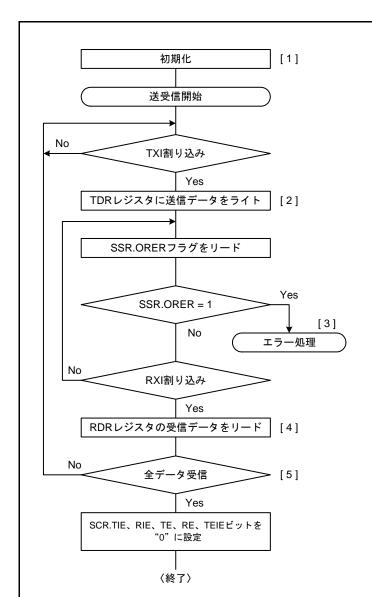

| 23.5.6   | シリアルデータの送受信同時動作(クロック同期式モード)          | 688 |

| 23.6 スマ  | アートカードインタフェースモードの動作                  | 689 |

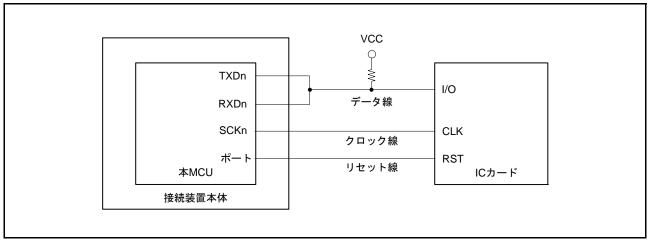

| 23.6.1   | 接続例                                  | 689 |

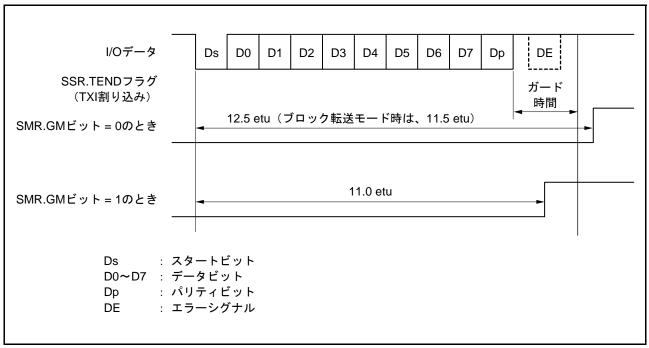

| 23.6.2   | データフォーマット(ブロック転送モード時を除く)             | 690 |

| 23.6.3   | ブロック転送モード                            | 691 |

| 23.6.4   | 受信データサンプリングタイミングと受信マージン              | 692 |

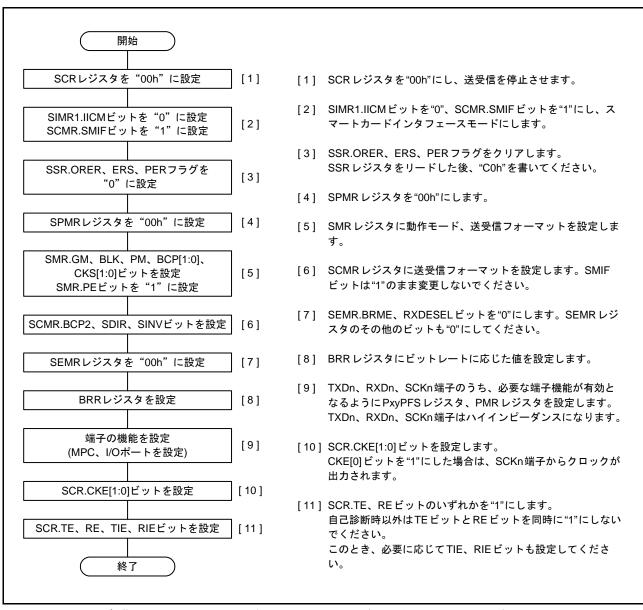

| 23.6.5   | SCI の初期化(スマートカードインタフェースモード)          | 693 |

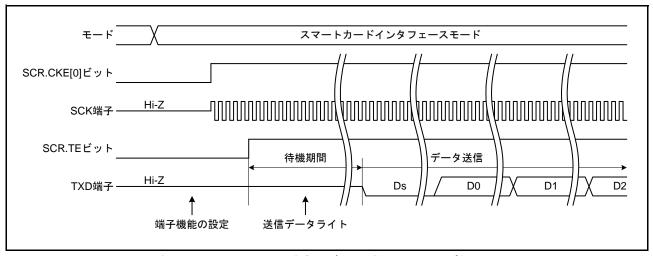

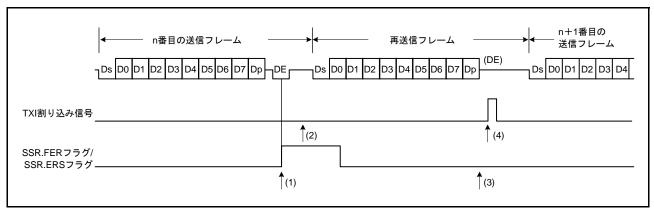

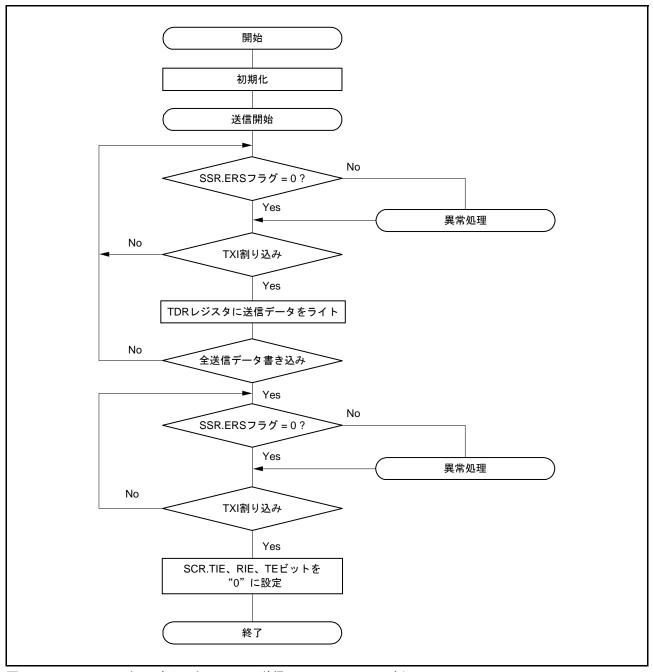

| 23.6.6   | シリアルデータの送信 (ブロック転送モードを除く)            | 695 |

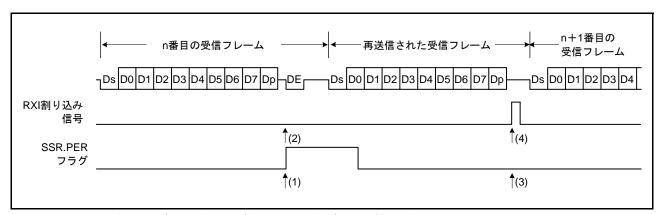

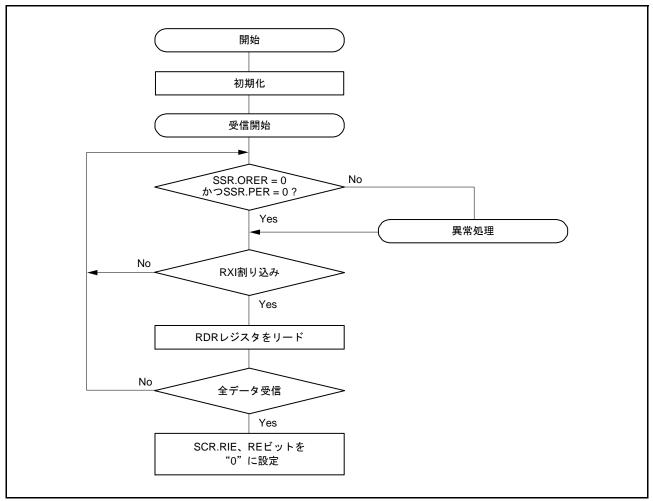

| 23.6.7   | シリアルの受信 (ブロック転送モードを除く)               | 698 |

| 23.6.8   | クロック出力制御                             | 700 |

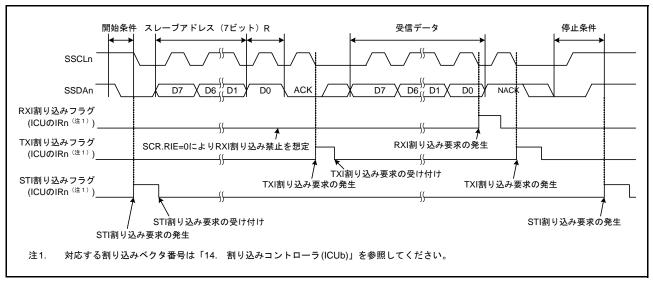

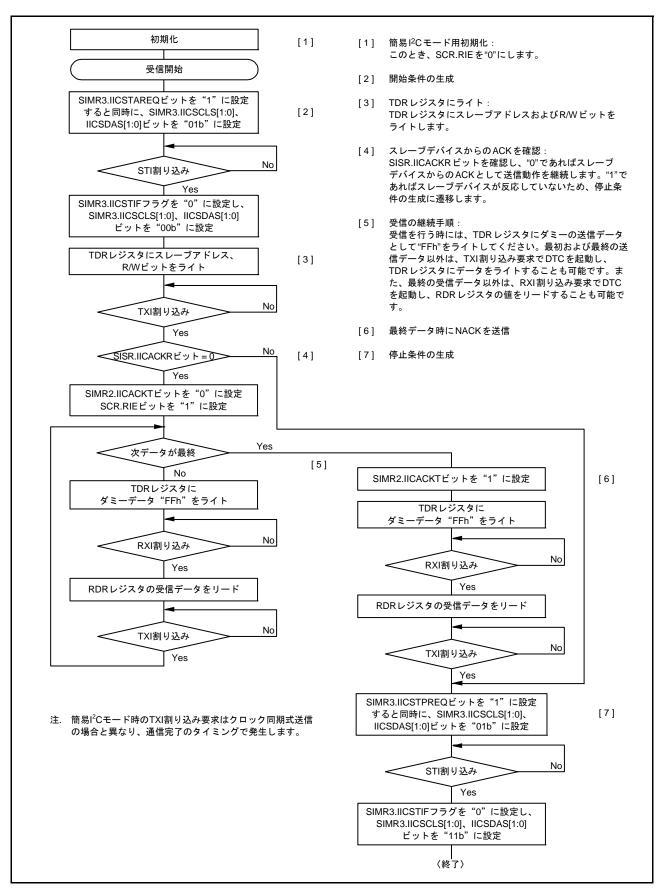

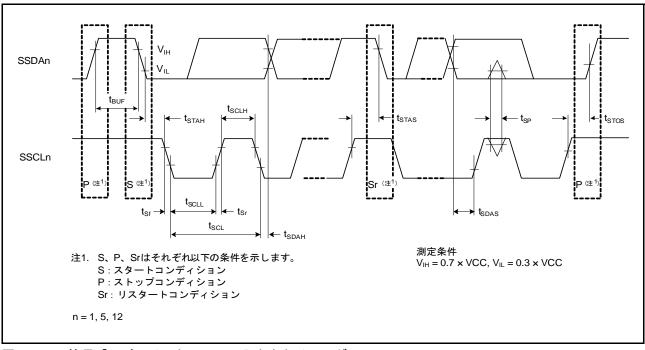

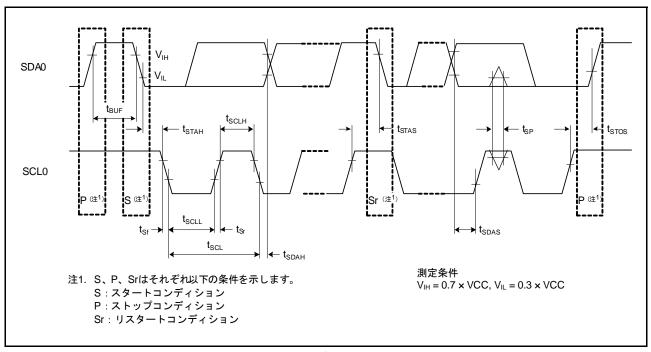

| 23.7 簡易  | 占 I <sup>2</sup> C モードの動作            | 701 |

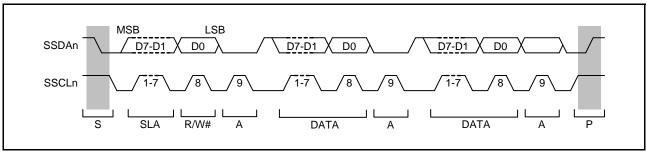

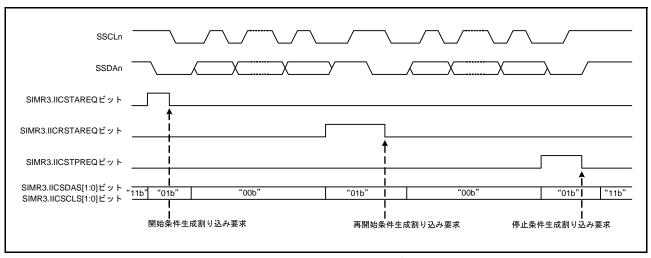

| 23.7.1   | 開始条件、再開始条件、停止条件の生成                   | 702 |

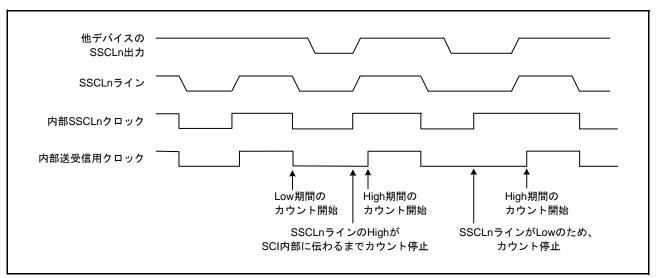

| 23.7.2   | クロック同期化                              | 704 |

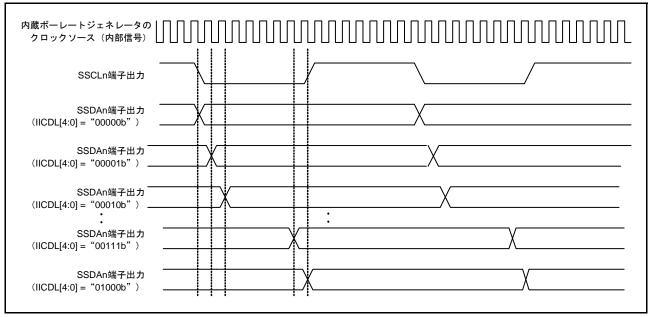

| 23.7.3   | SSDA 出力遅延                            | 705 |

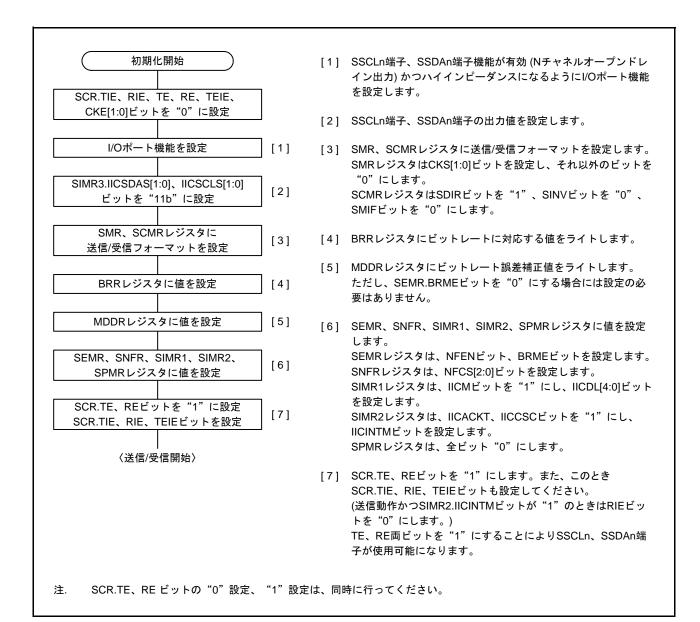

| 23.7.4   | SCI の初期化 ( 簡易 I <sup>2</sup> C モード ) | 706 |

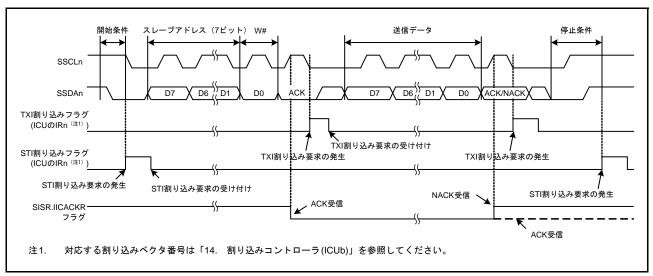

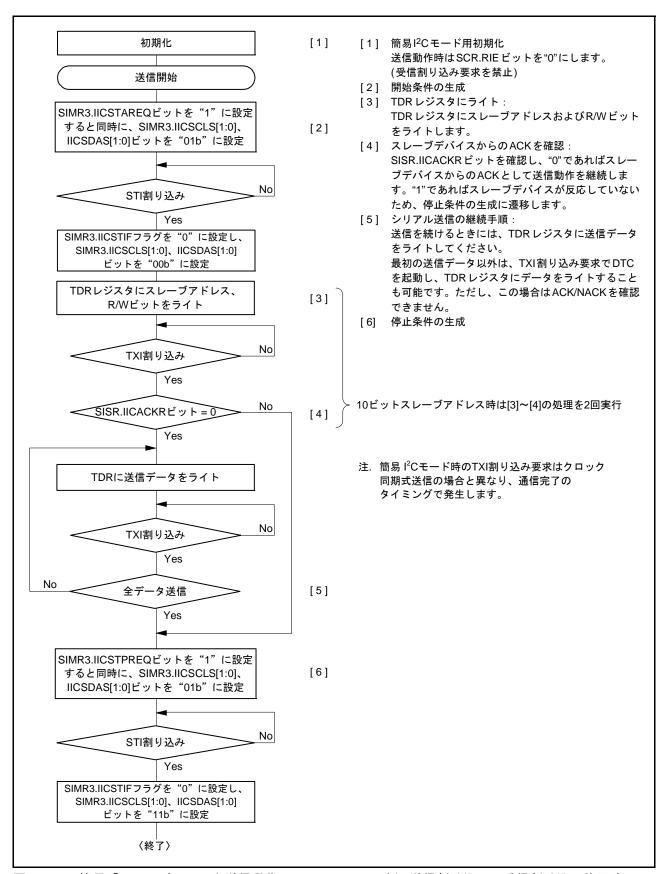

| 23.7.5   | マスタ送信動作 ( 簡易 I <sup>2</sup> C モード )  | 707 |

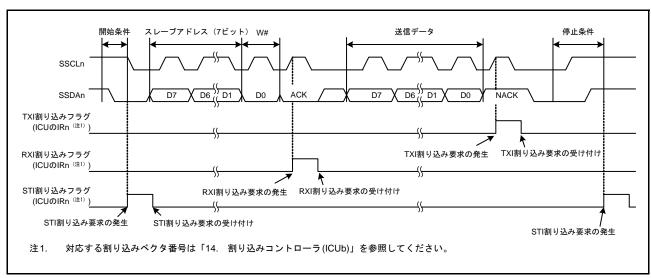

| 23.7.6   | マスタ受信動作(簡易 I <sup>2</sup> C モード)     | 709 |

| 23.7.7   | バスハングアップからの回復                        | 711 |

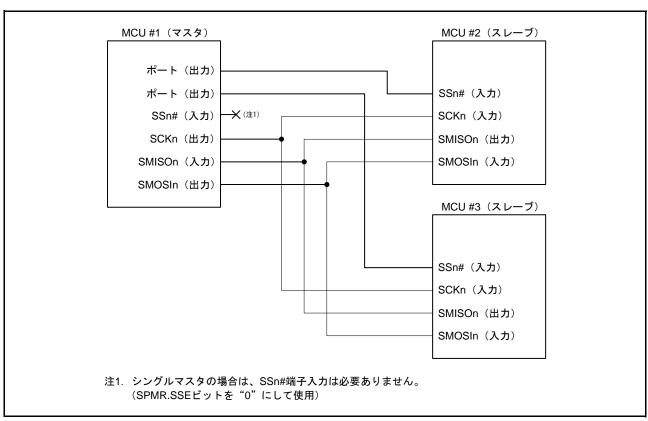

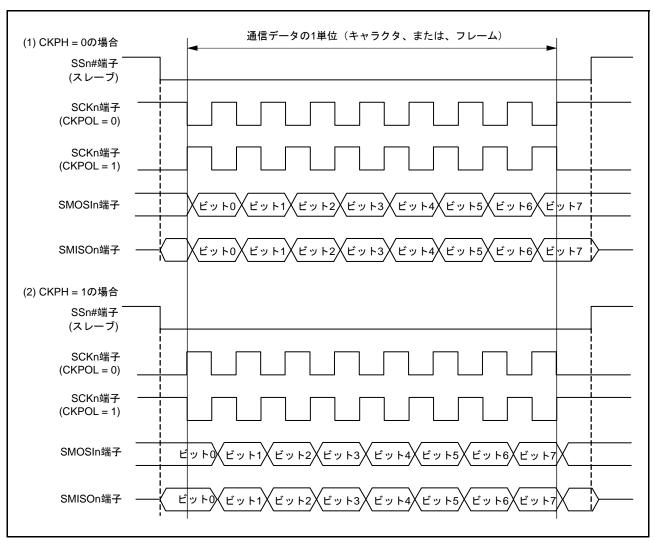

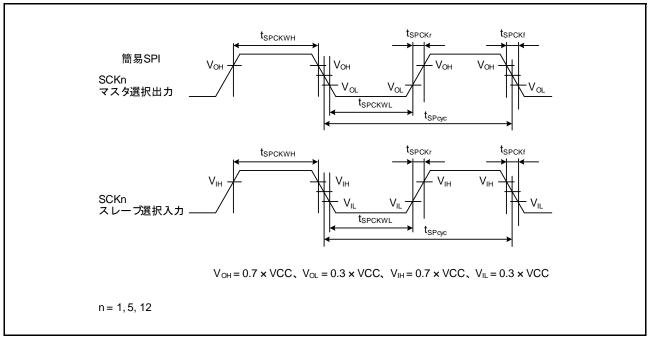

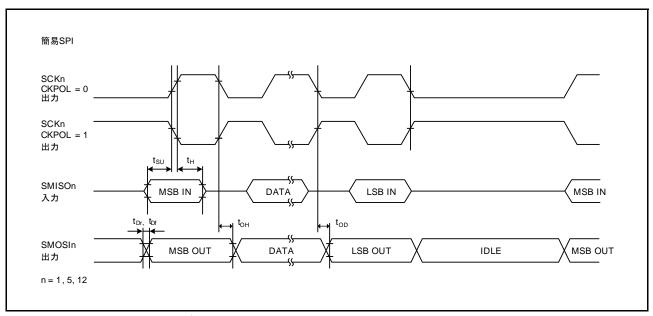

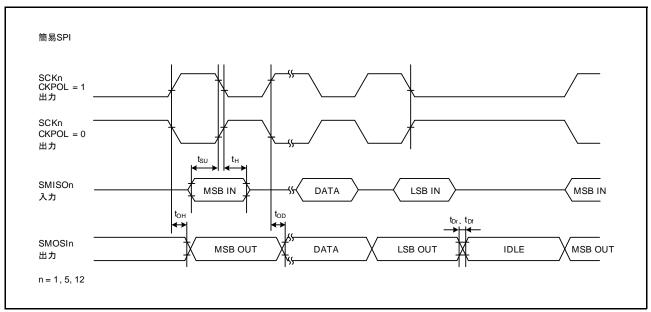

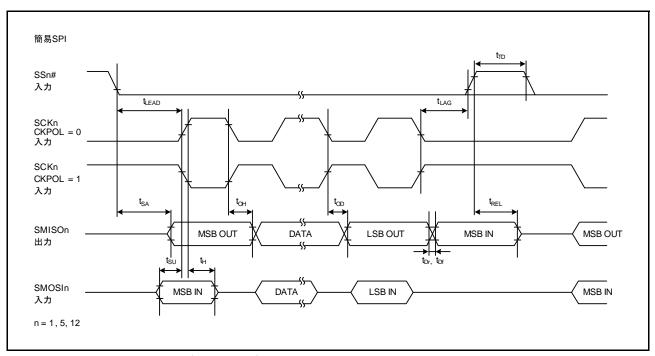

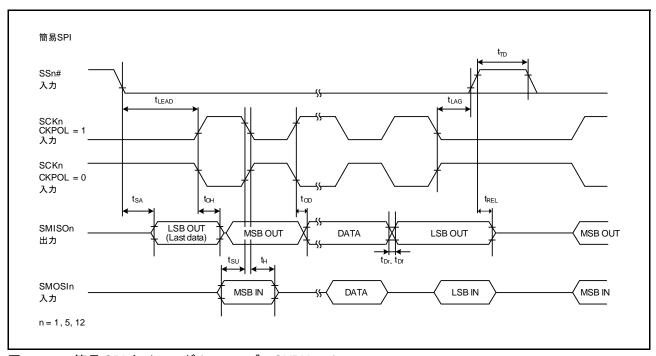

| 23.8 簡易  | 号 SPI モードの動作                         | 712 |

| 23.8.1   | マスタモード、スレーブモードと各端子の状態                | 713 |

| 23.8.2   | マスタモード時の <b>SS</b> 機能                | 713 |

| 23.8.3   | スレーブモード時の <b>SS</b> 機能               | 713 |

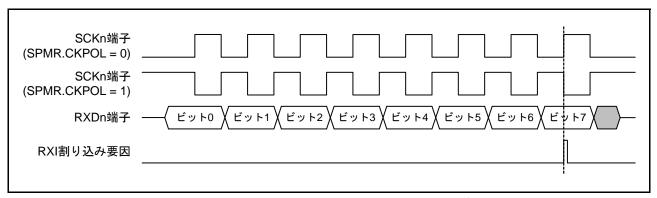

| 23.8.4   | クロックと送受信データの関係                       | 714 |

| 23.8.5   | SCI の初期化 ( 簡易 SPI モード )              | 714 |

| 23.8.6   | シリアルデータの送受信 ( 簡易 SPI モード )           | 715 |

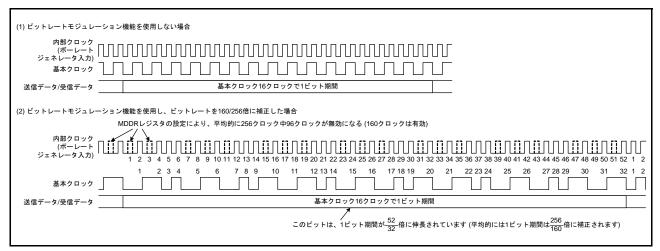

| 23.9 ビッ  | ・トレートモジュレーション機能                      | 715 |

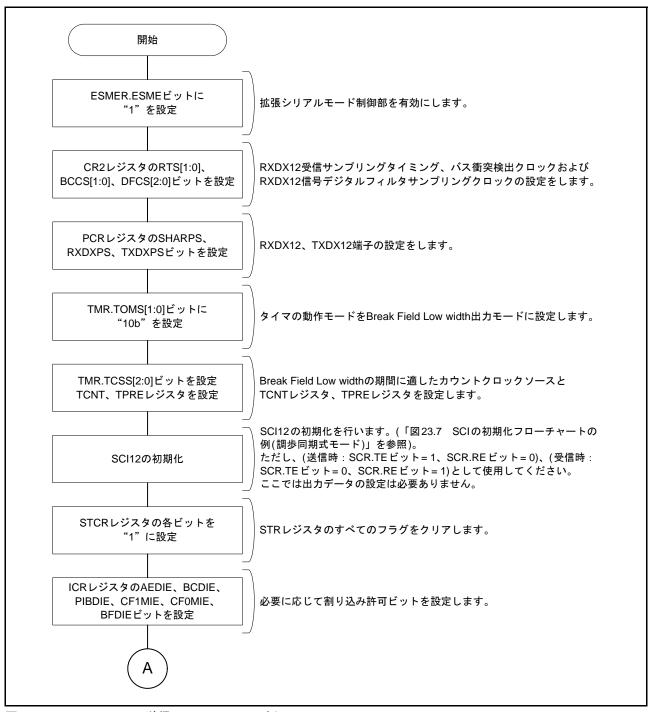

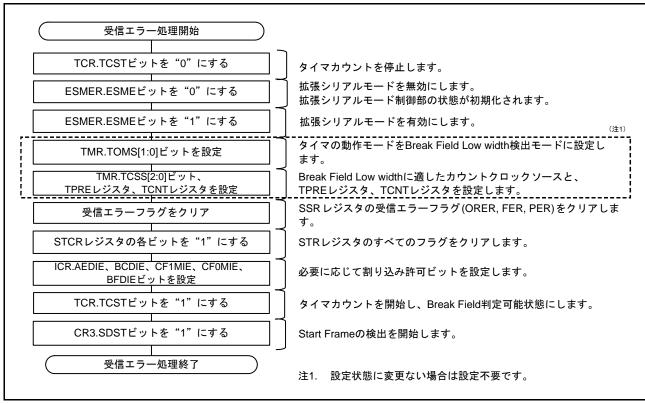

| 23.10 拡張 | <ul><li>シリアルモード制御部の動作説明</li></ul>    | 716 |

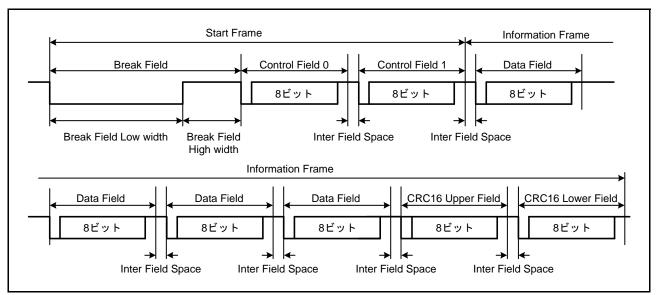

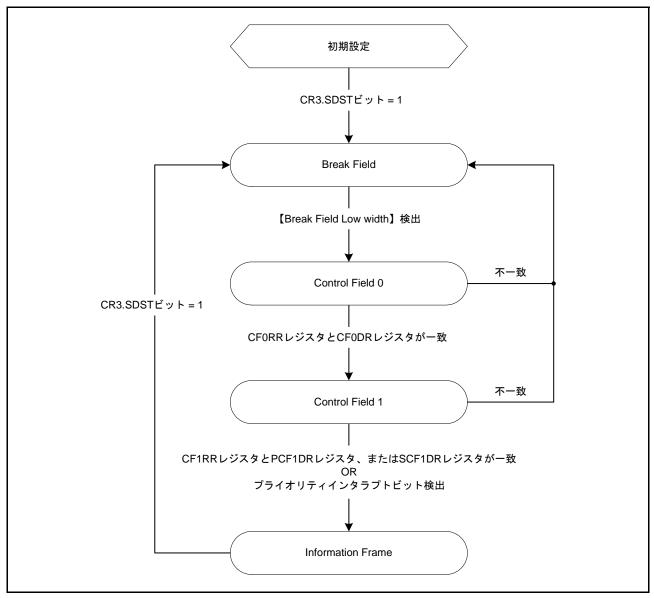

| 23.10.1  | シリアル通信プロトコル                          | 716 |

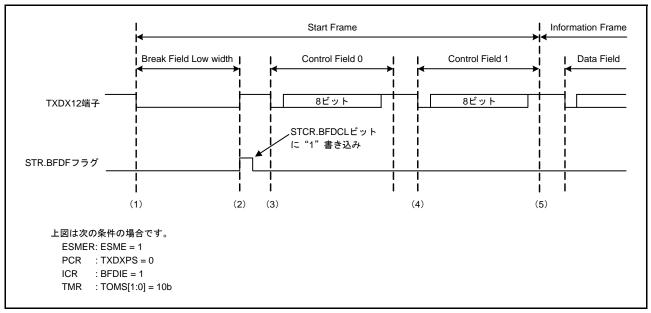

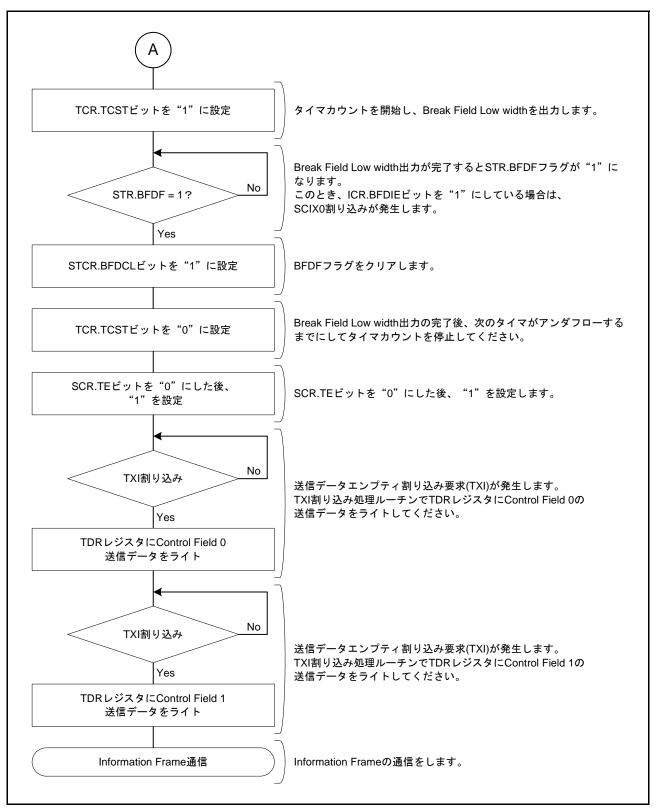

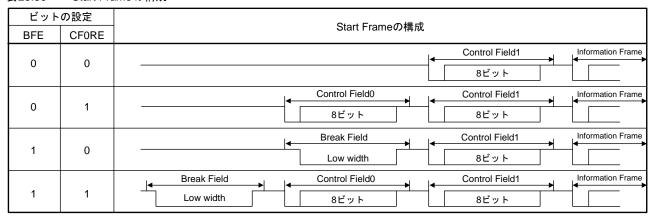

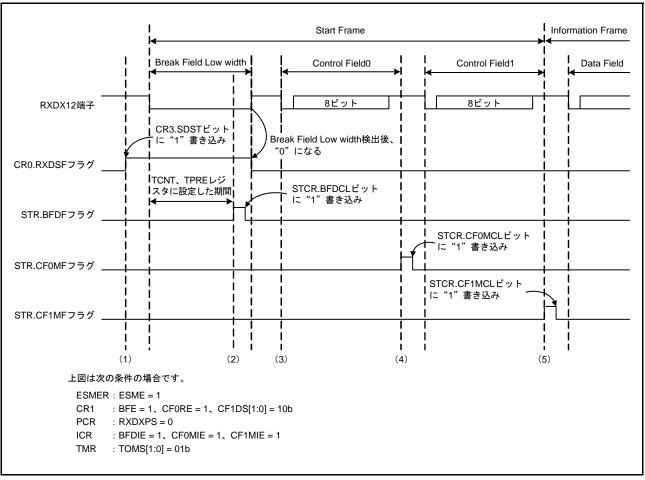

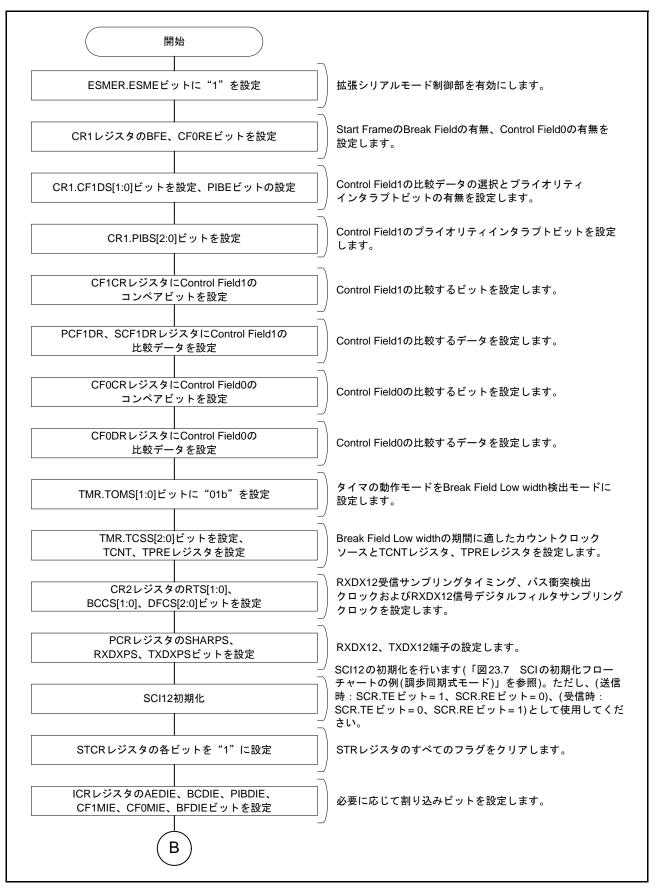

| 23.10.2  | Start Frame 送信                       | 716 |

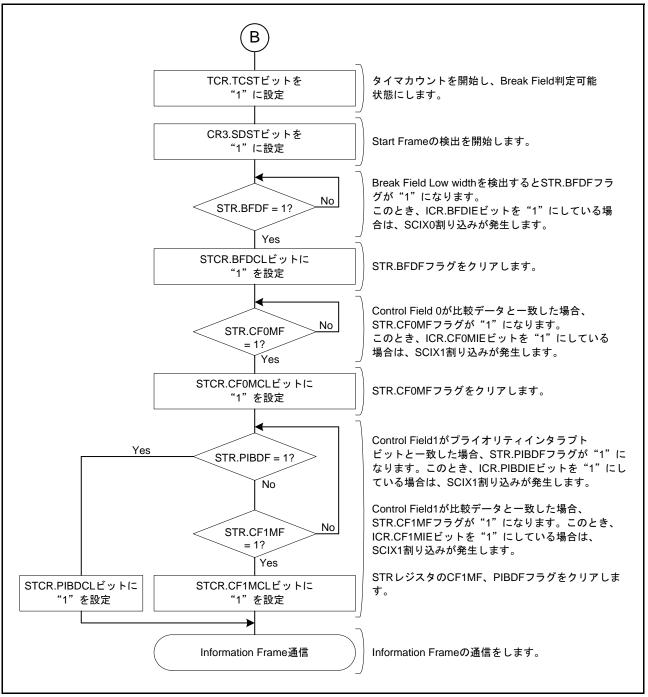

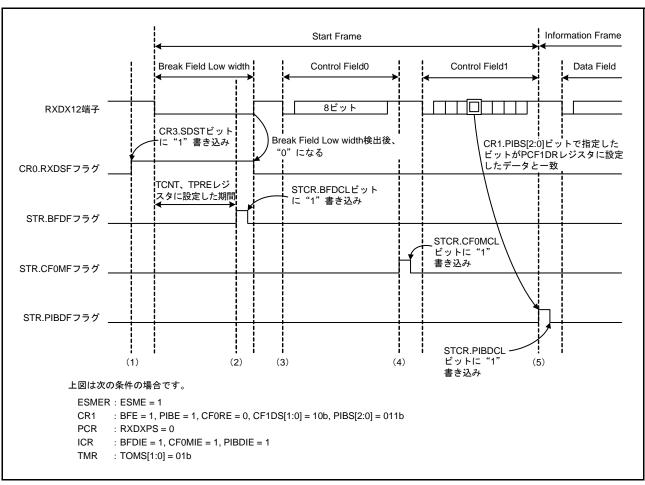

| 23.10.3  | Start Frame 受信                       | 720 |

| 23.10.3  | 3.1 プライオリティインタラプトビット                 | 725 |

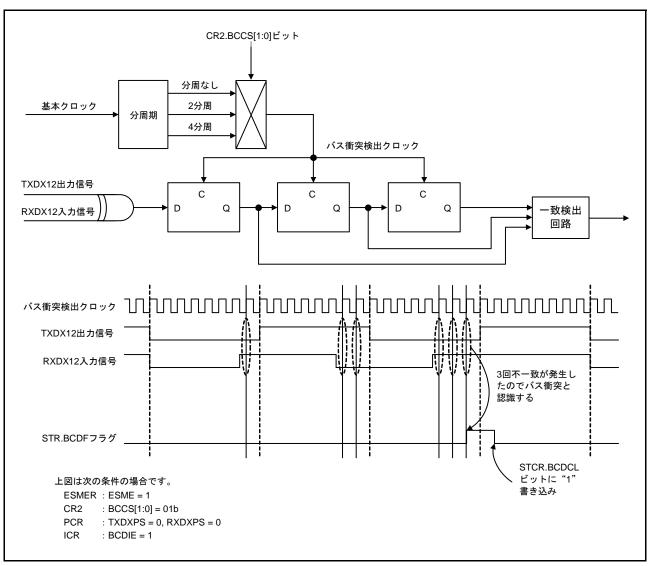

| 23.10.4  | バス衝突検出機能                             | 726 |

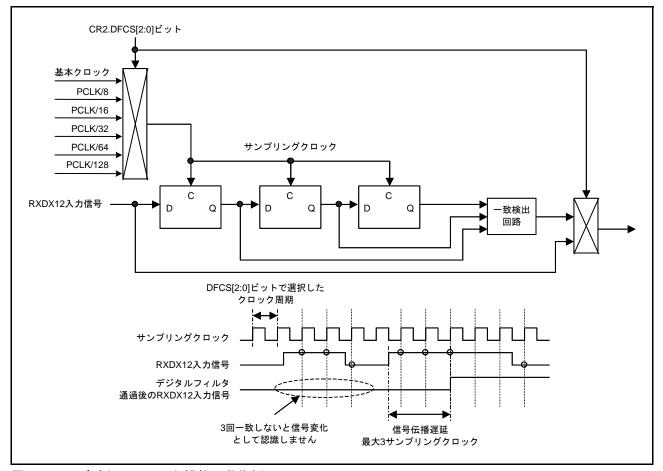

| 23.10.5  | RXDX12 端子入力デジタルフィルタ機能                |     |

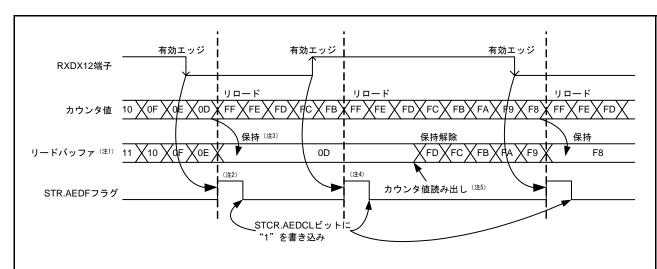

| 23.10.6  | ビットレート測定機能                           |     |

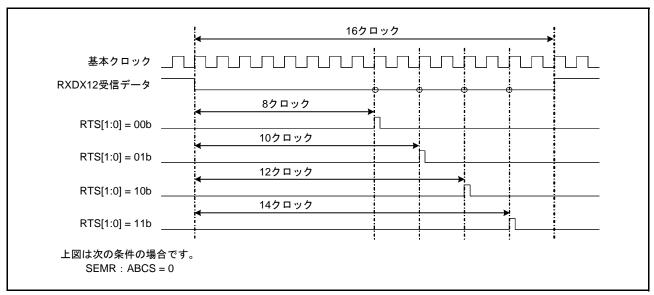

| 23.10.7  | RXDX12 受信データサンプリングタイミング選択機能          | 729 |

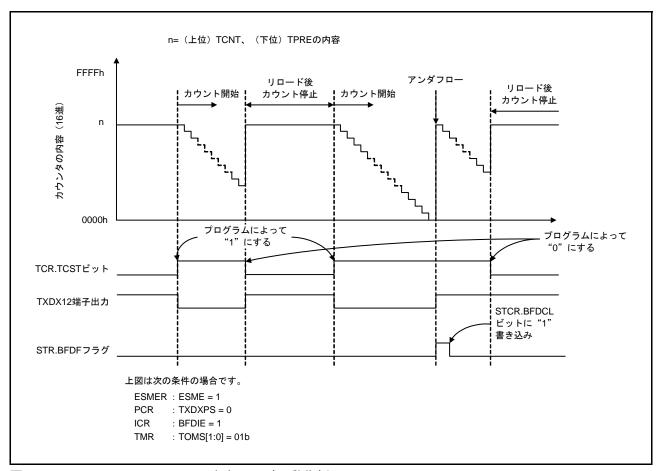

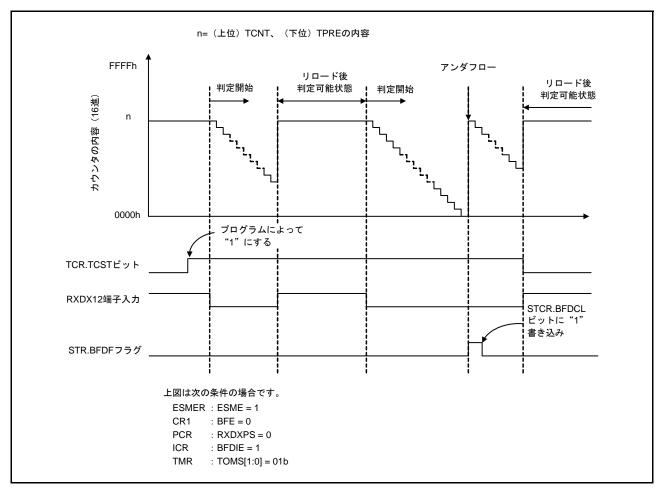

| 23.10.8  | タイマ                                  | 730 |

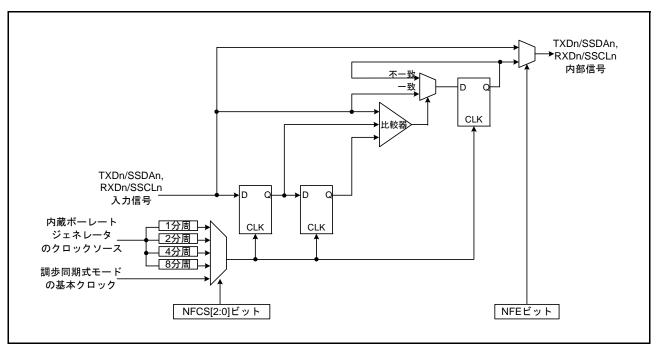

| 23.11 ノイ | `ズ除去機能                               | 732 |

| 23.12 害                 | り込み要因                                          | 733 |

|-------------------------|------------------------------------------------|-----|

| 23.12.1                 | TXI 割り込みおよび RXI 割り込みバッファ動作                     | 733 |

| 23.12.2                 | 調歩同期式モード、クロック同期式モードおよび<br>簡易 SPI モードにおける割り込み   | 733 |

| 23.12.3                 | スマートカードインタフェースモードにおける割り込み                      | 734 |

| 23.12.4                 | 簡易 I <sup>2</sup> C モードにおける割り込み                | 735 |

| 23.12.5                 | 拡張シリアルモード制御部の割り込み要求                            | 736 |

| 23.13 (                 |                                                | 737 |

| 23.13.1                 | モジュールストップ機能の設定                                 | 737 |

| 23.13.2                 | ブレークの検出と処理について                                 | 737 |

| 23.13.3                 | マーク状態とブレークの送出                                  | 737 |

| 23.13.4                 | 受信エラーフラグと送信動作について<br>(クロック同期式モードおよび簡易 SPI モード) | 737 |

| 23.13.5                 | TDR レジスタへのライトについて                              | 737 |

| 23.13.6                 | クロック同期送信時の制約事項<br>( クロック同期式モードおよび簡易 SPI モード )  | 738 |

| 23.13.7                 | DTC 使用上の制約事項                                   | 739 |

| 23.13.8                 | 通信の開始に関する注意事項                                  | 739 |

| 23.13.9                 | 低消費電力状態時の動作について                                | 739 |

| 23.13.10                | クロック同期式モードおよび簡易 SPI モードにおける外部クロック入力            | 741 |

| 23.13.11                | 簡易 SPI モードの制約事項                                | 742 |

| 23.13.12                | . 拡張シリアルモード制御部の使用上の制約事項 1                      | 743 |

| 23.13.13                | 拡張シリアルモード制御部の使用上の制約事項 2                        | 743 |

| 23.13.14                | トランスミットイネーブルビット (TE ビット ) に関する注意事項             | 744 |

| 23.13.15                | 調歩同期式モードにおける RTS 機能使用時の受信停止に関する注意事項            | 744 |

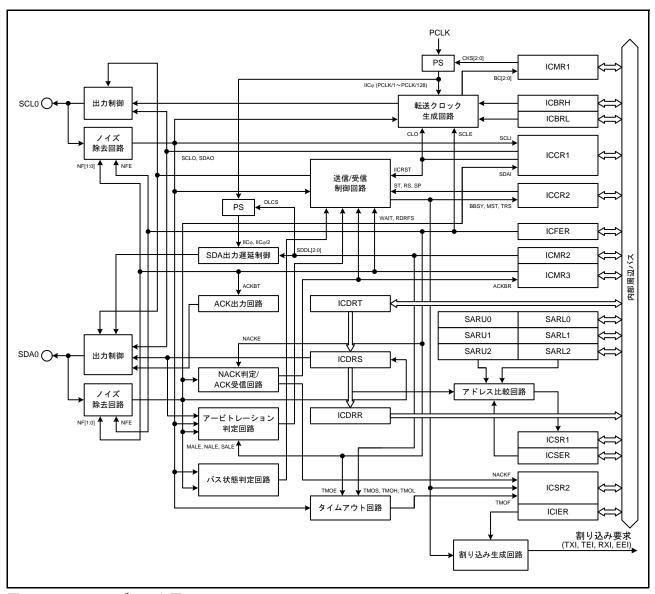

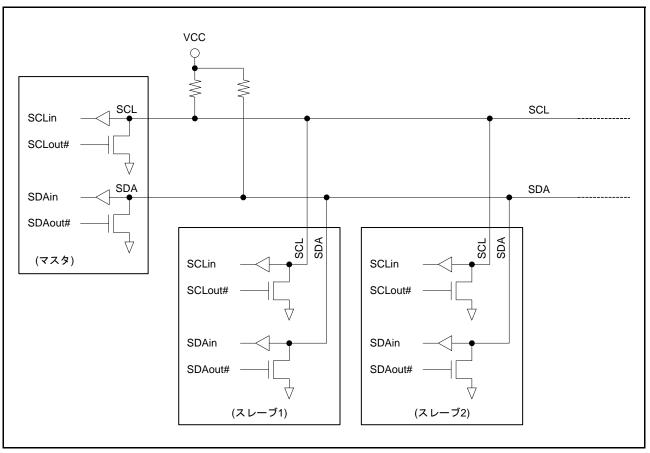

| 24. I <sup>2</sup> C バス | インタフェース (RIICa)                                | 745 |

| 24.1 栂                  | 要                                              | 745 |

| 24.2 レ                  | ジスタの説明                                         | 748 |

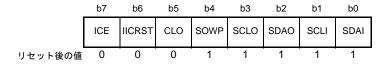

| 24.2.1                  | I <sup>2</sup> C バスコントロールレジスタ 1 (ICCR1)        | 748 |

| 24.2.2                  | I <sup>2</sup> C バスコントロールレジスタ 2 (ICCR2)        | 750 |

| 24.2.3                  | I <sup>2</sup> C バスモードレジスタ 1 (ICMR1)           | 753 |

| 24.2.4                  | I <sup>2</sup> C バスモードレジスタ 2 (ICMR2)           | 754 |

| 24.2.5                  | I <sup>2</sup> C バスモードレジスタ 3 (ICMR3)           | 756 |

| 24.2.6                  | I <sup>2</sup> C バスファンクション許可レジスタ (ICFER)       | 758 |

| 24.2.7                  | I <sup>2</sup> C バスステータス許可レジスタ (ICSER)         | 760 |

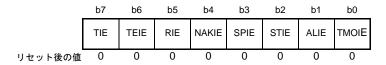

| 24.2.8                  | I <sup>2</sup> C バス割り込み許可レジスタ (ICIER)          | 762 |

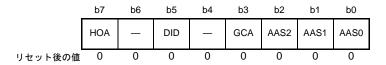

| 24.2.9                  | I <sup>2</sup> C バスステータスレジスタ 1 (ICSR1)         | 764 |

| 24.2.10                 | I <sup>2</sup> C バスステータスレジスタ 2 (ICSR2)         | 766 |

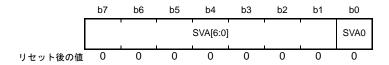

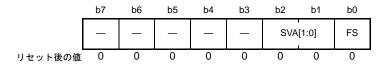

| 24.2.11                 | スレーブアドレスレジスタ Ly (SARLy) (y = 0 $\sim$ 2)       | 769 |

| 24.2.12                 | スレーブアドレスレジスタ Uy (SARUy) (y = 0 $\sim$ 2)       | 770 |

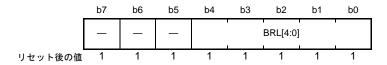

| 24.2.13                 | I <sup>2</sup> C バスビットレート Low レジスタ (ICBRL)     | 771 |

| 24    | 1.2.14 | I <sup>2</sup> C バスビットレート High レジスタ (ICBRH) | 772 |

|-------|--------|---------------------------------------------|-----|

| 24    | 1.2.15 | I <sup>2</sup> C バス送信データレジスタ (ICDRT)        | 773 |

| 24    | 1.2.16 | I <sup>2</sup> C バス受信データレジスタ (ICDRR)        | 774 |

| 24    | 1.2.17 | I <sup>2</sup> C バスシフトレジスタ (ICDRS)          | 774 |

| 24.3  | 動作     | 乍説明                                         | 775 |

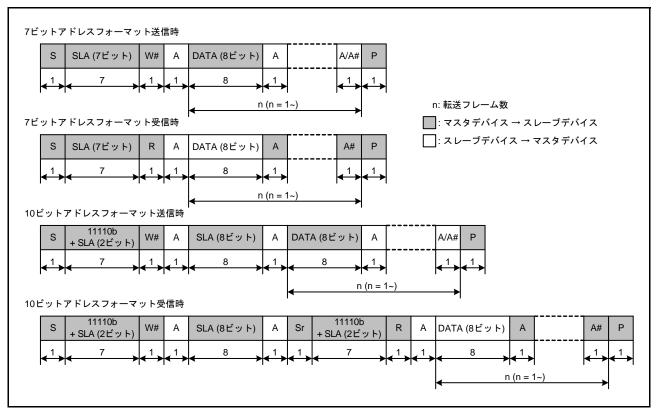

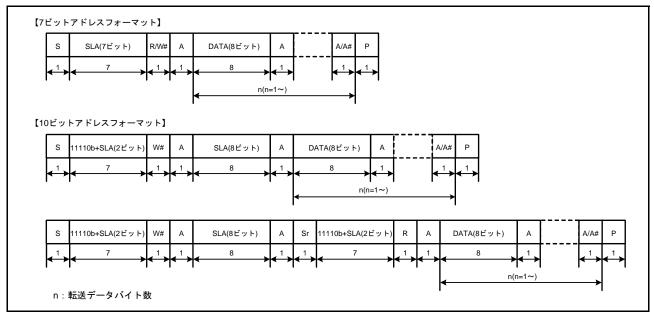

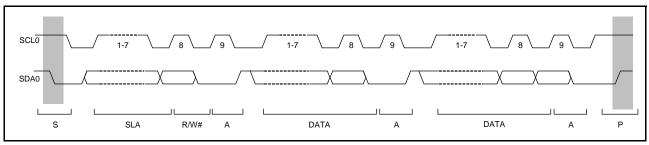

| 24    | 1.3.1  | 通信データフォーマット                                 | 775 |

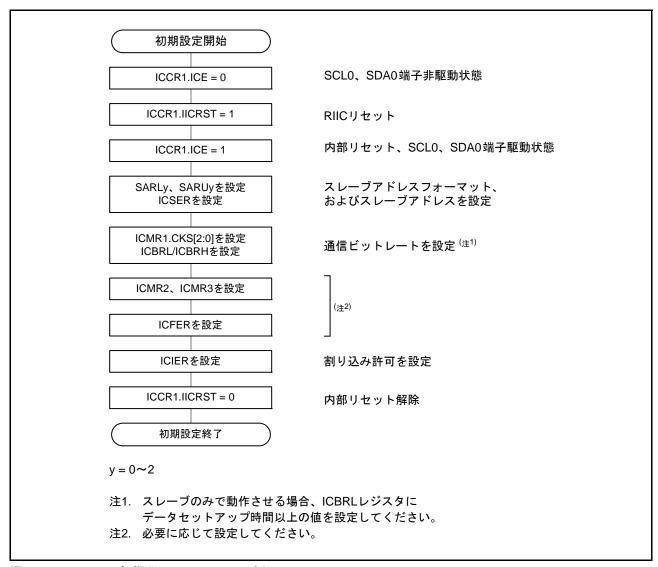

| 24    | 1.3.2  | 初期設定                                        | 776 |

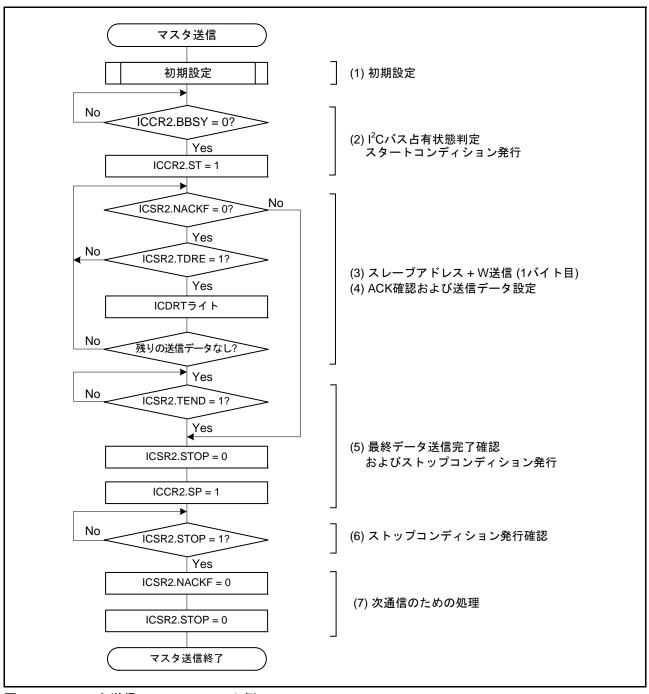

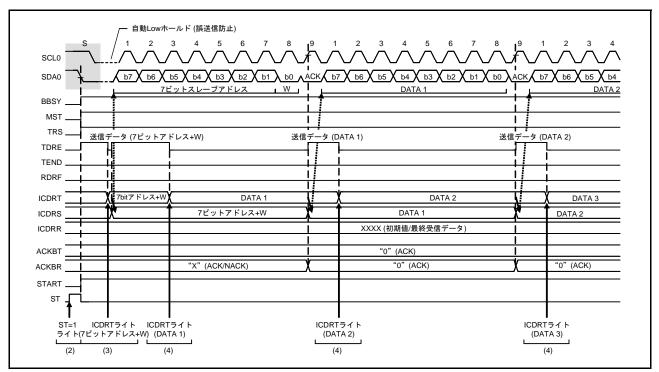

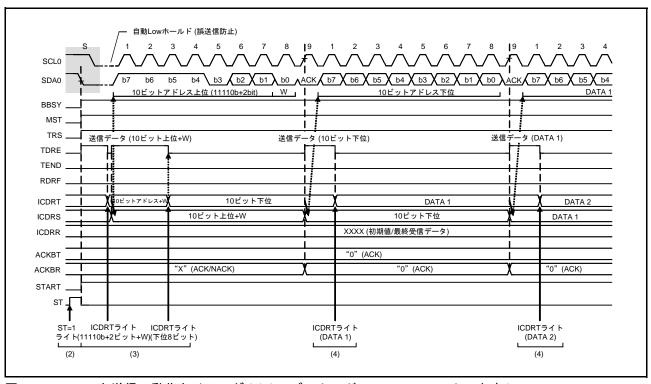

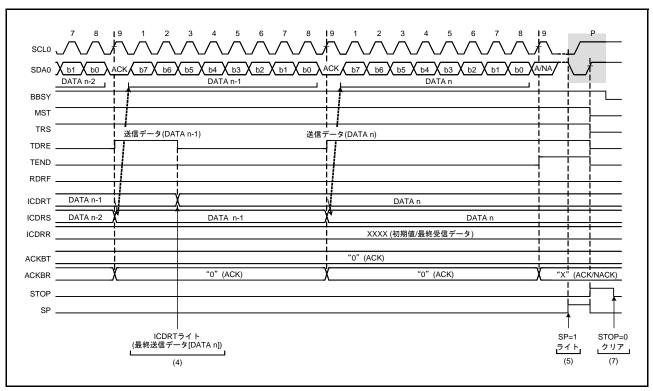

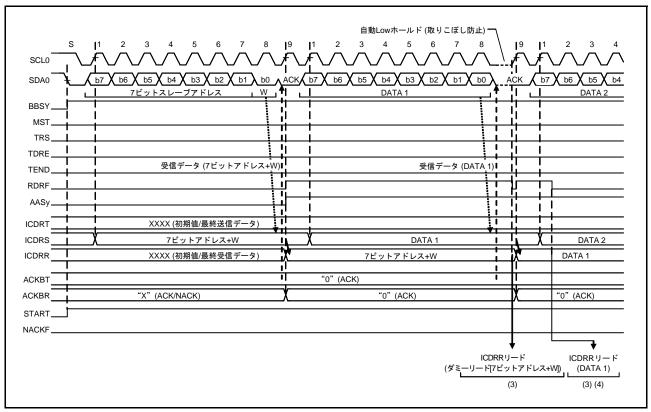

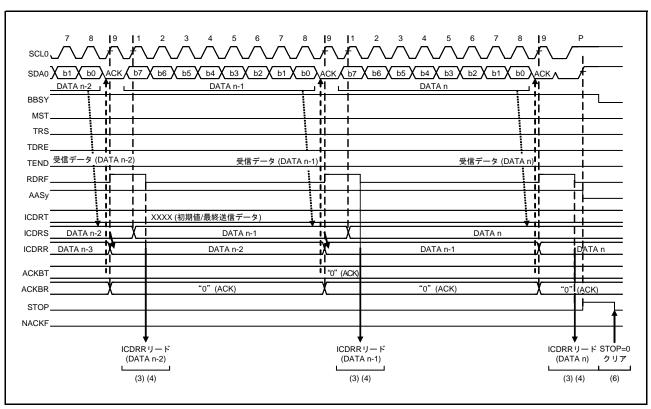

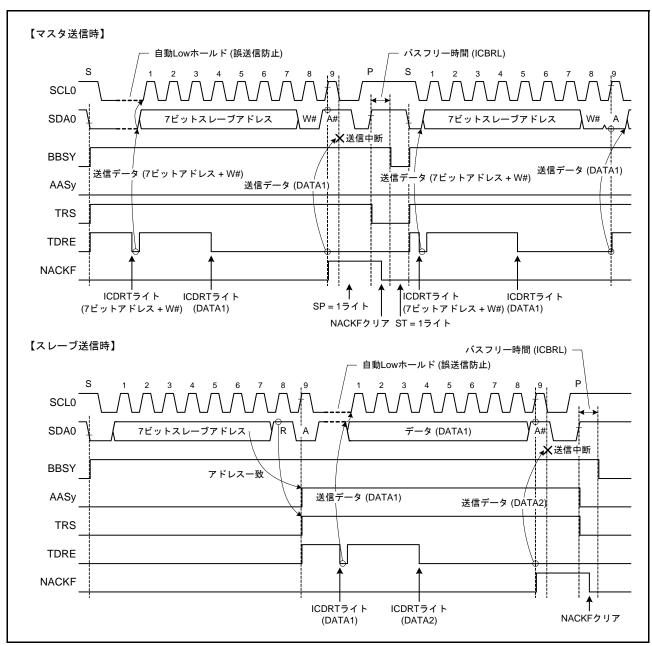

| 24    | 1.3.3  | マスタ送信動作                                     | 777 |

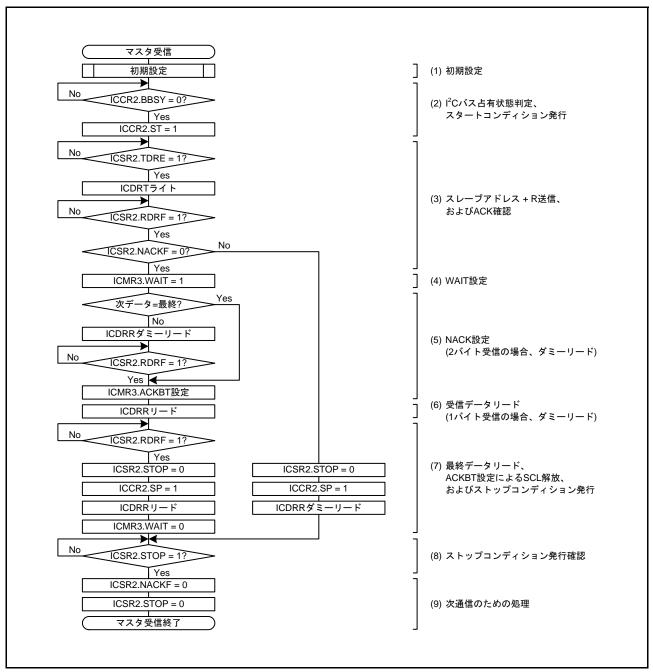

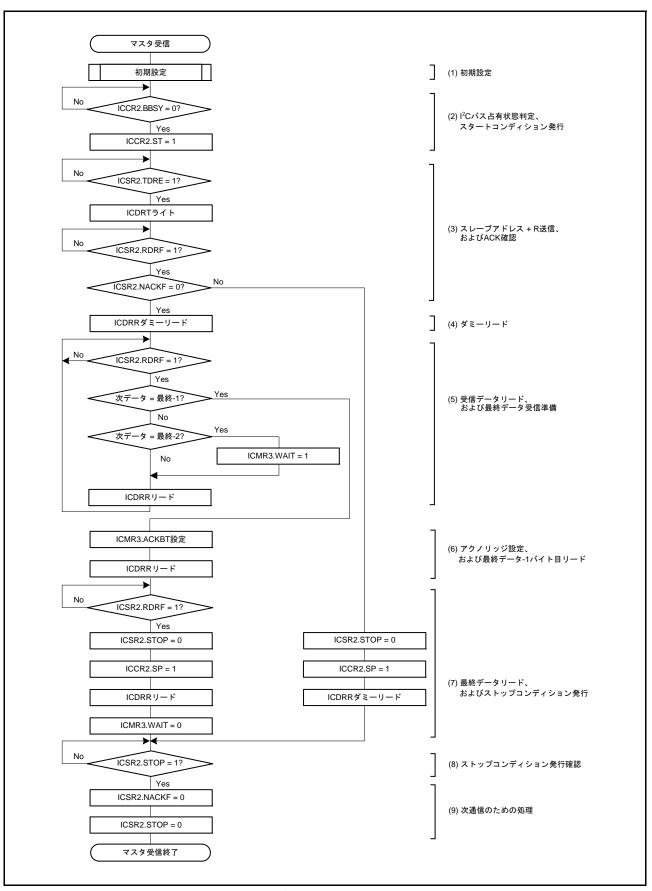

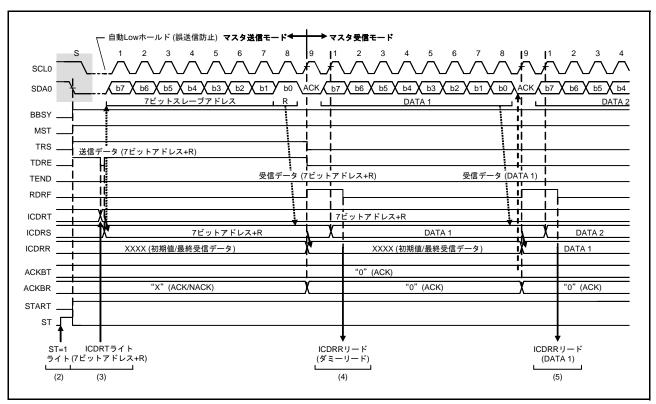

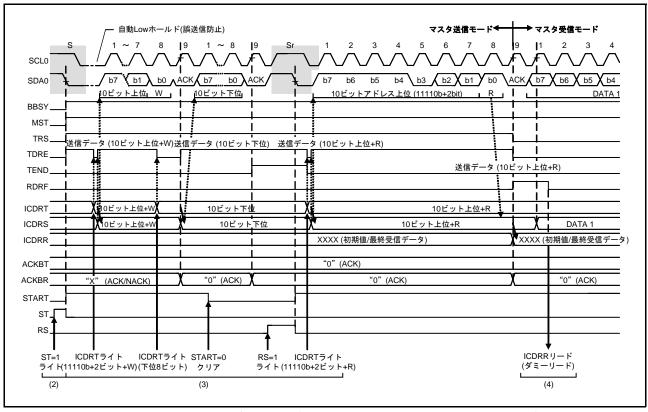

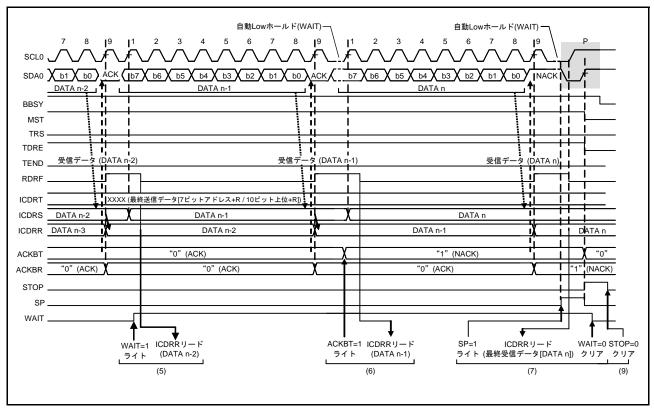

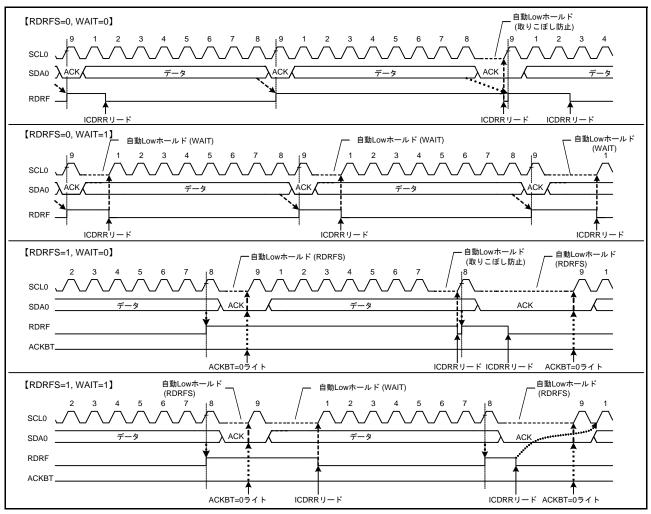

| 24    | 1.3.4  | マスタ受信動作                                     | 780 |

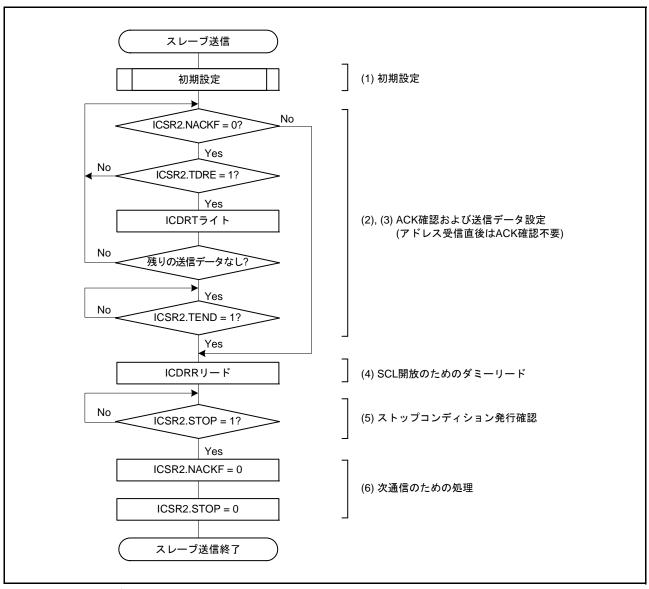

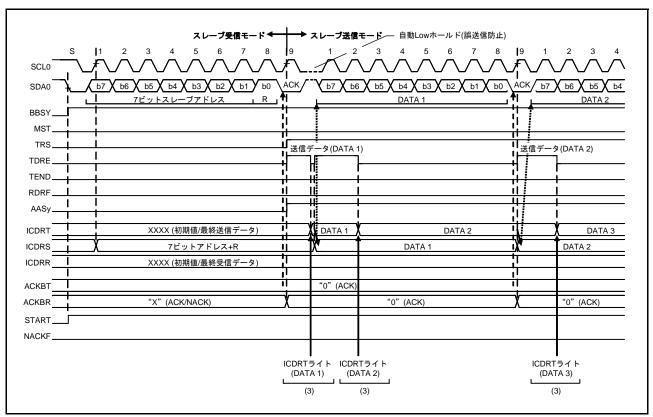

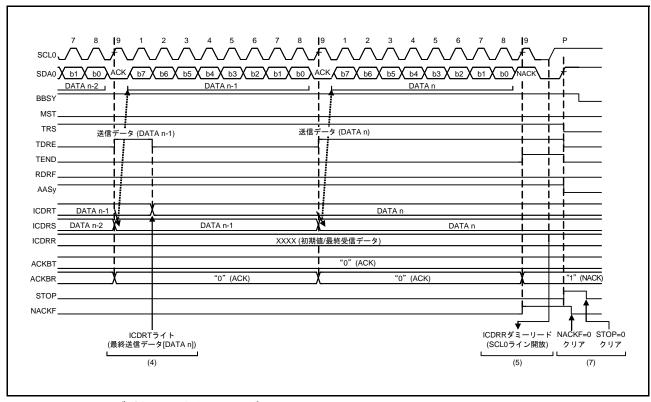

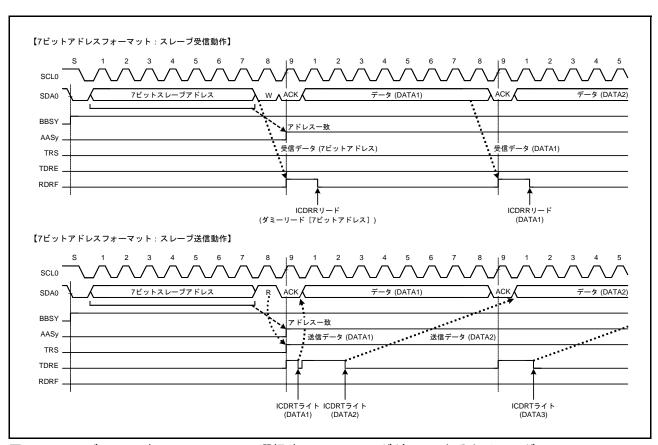

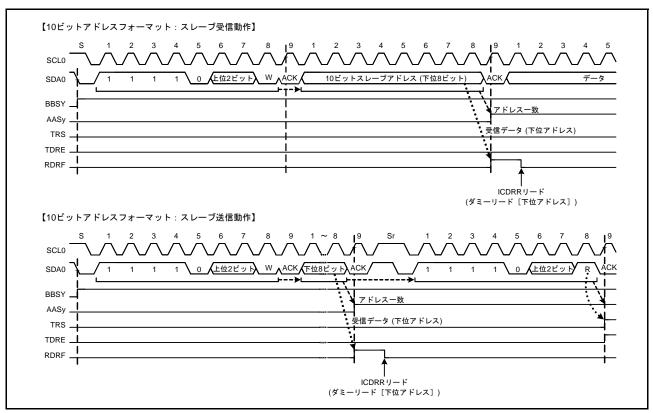

| 24    | 1.3.5  | スレーブ送信動作                                    | 786 |

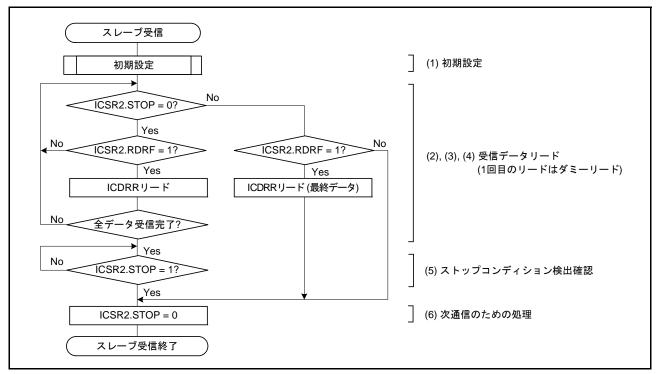

| 24    | 1.3.6  | スレーブ受信動作                                    | 789 |

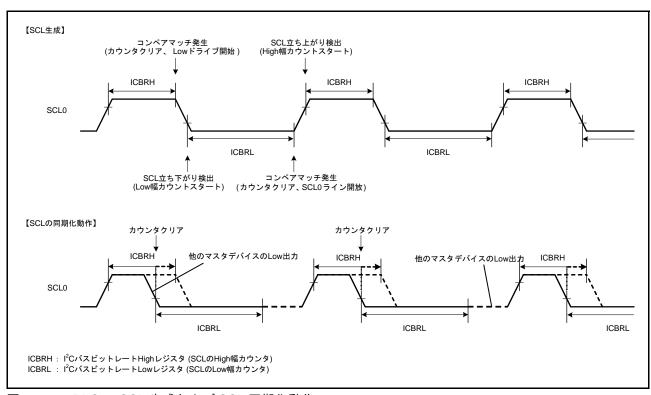

| 24.4  | SCI    | L 同期回路                                      | 791 |

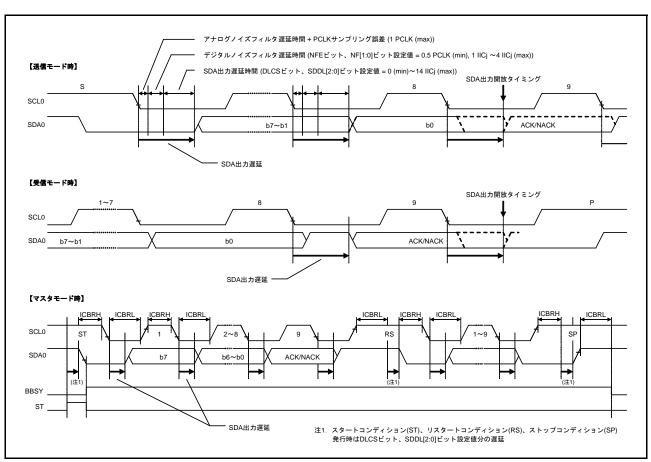

| 24.5  | SD     | A 出力遅延機能                                    | 792 |

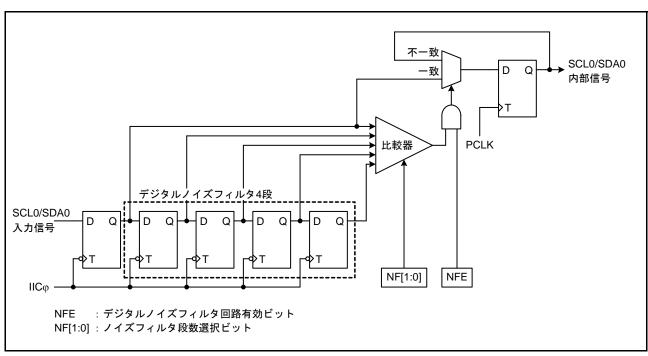

| 24.6  | デミ     | ブタルノイズフィルタ回路                                | 793 |

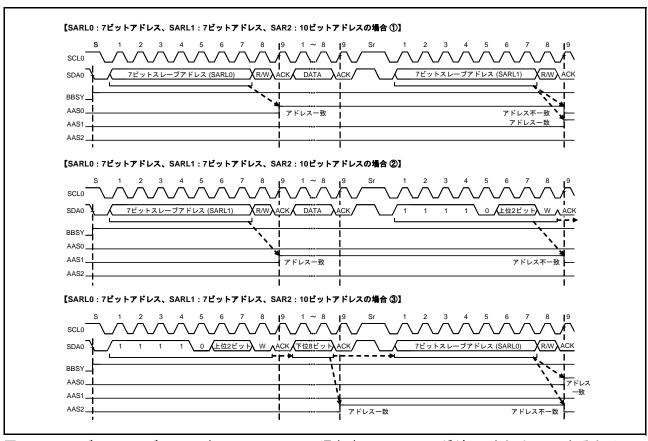

| 24.7  | ア      | ドレス一致検出機能                                   | 794 |

| 24    | 1.7.1  | スレーブアドレス一致検出機能                              | 794 |

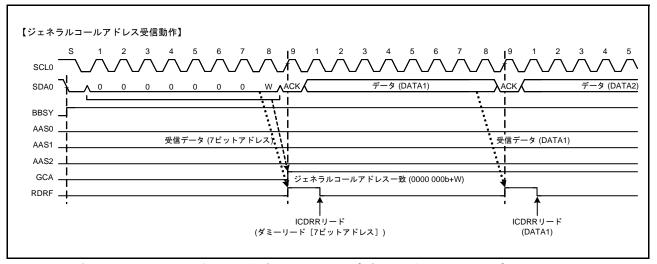

| 24    | 1.7.2  | ジェネラルコールアドレス検出機能                            | 796 |

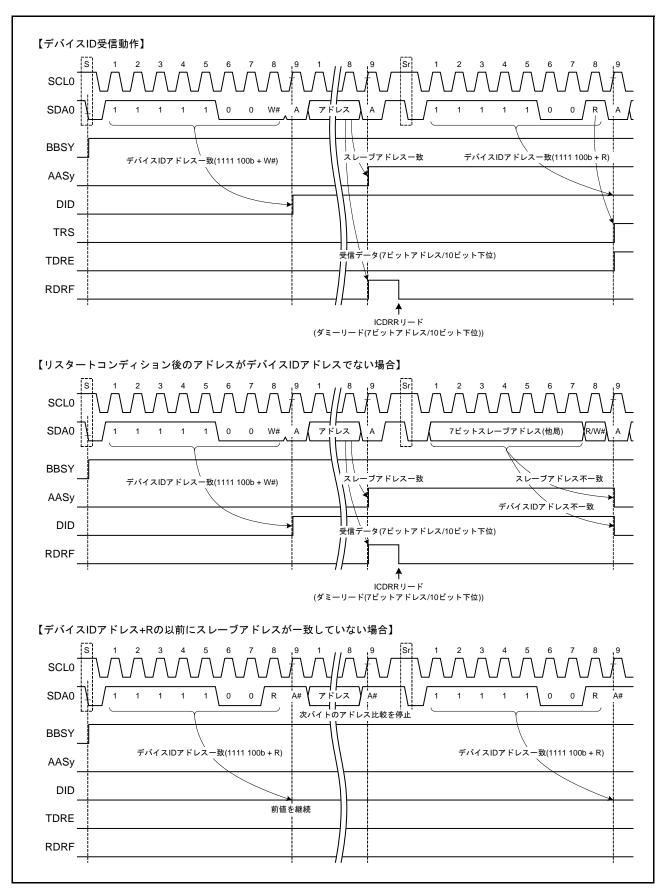

| 24    | 1.7.3  | デバイス ID アドレス検出機能                            | 797 |

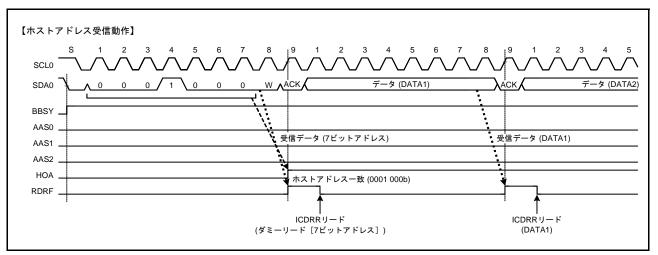

| 24    | 1.7.4  | ホストアドレス検出機能                                 | 799 |

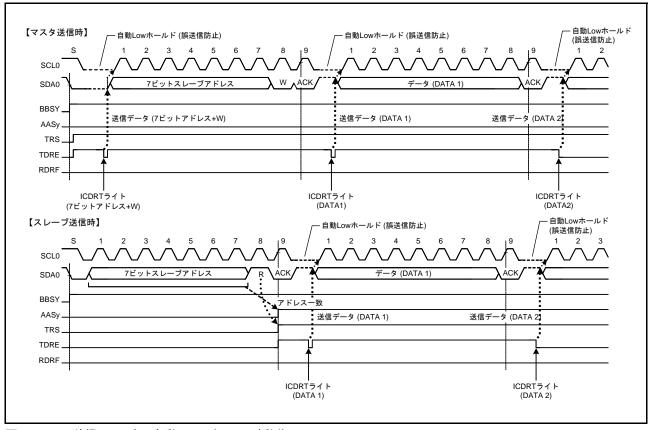

| 24.8  | SCI    | L の自動 Low ホールド機能                            | 800 |

| 24    | 1.8.1  | 送信データ誤送信防止機能                                | 800 |

| 24    | 1.8.2  | NACK 受信転送中断機能                               | 801 |

| 24    | 1.8.3  | 受信データ取りこぼし防止機能                              | 802 |

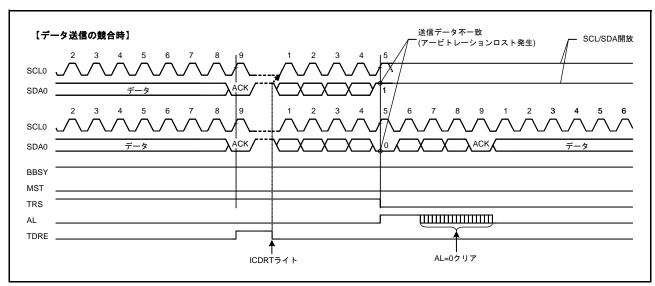

| 24.9  | アー     | ービトレーションロスト検出機能                             | 804 |

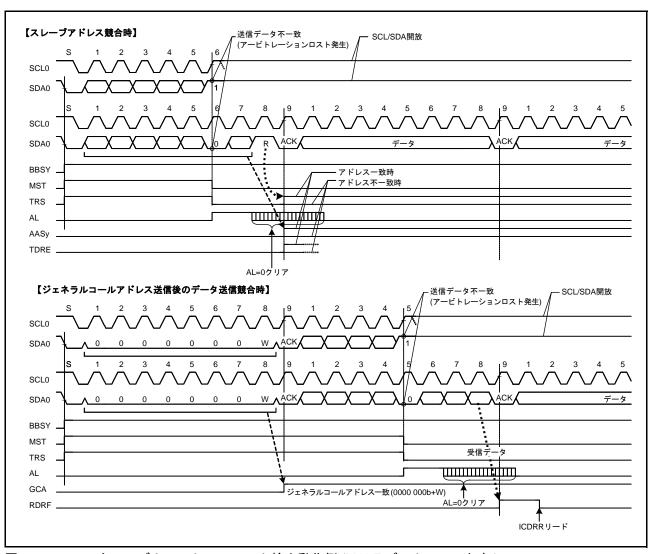

| 24    | 1.9.1  | マスタアービトレーションロスト検出機能 (MALE ビット)              | 804 |

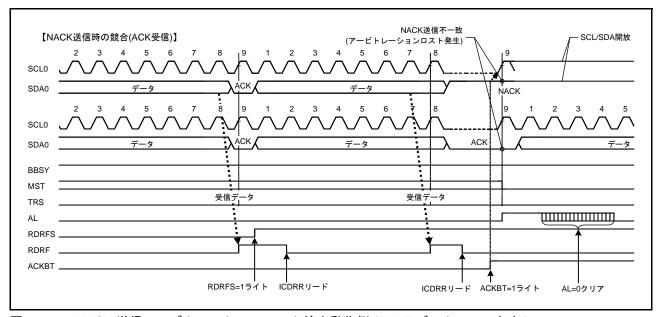

| 24    | 1.9.2  | NACK 送信アービトレーションロスト検出機能 (NALE ビット)          | 806 |

| 24    | 1.9.3  | スレーブアービトレーションロスト検出機能 (SALE ビット)             | 807 |

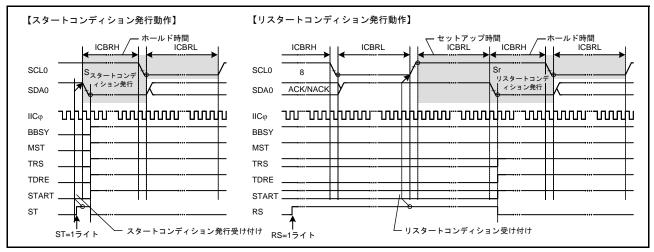

| 24.10 |        | タートコンディション、リスタートコンディション、                    |     |

|       |        | トップコンディション発行機能                              |     |

|       |        | スタートコンディション発行動作                             |     |

| 24    |        | リスタートコンディション発行動作                            |     |

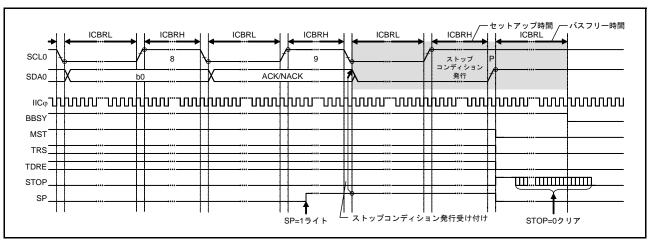

|       |        | ストップコンディション発行動作                             |     |

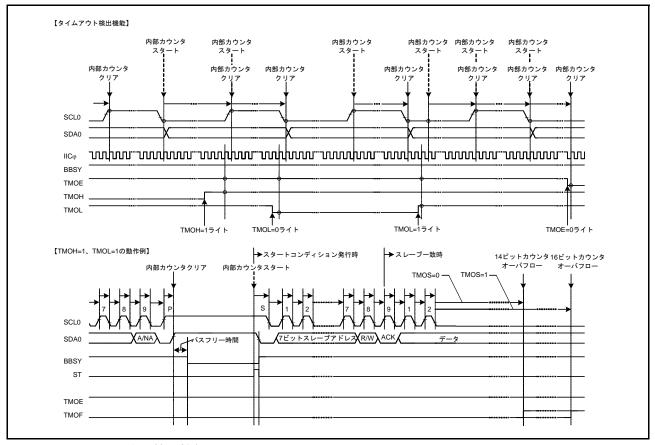

| 24.11 |        | スハングアップ                                     |     |

| 24    | 1.11.1 | タイムアウト検出機能                                  |     |

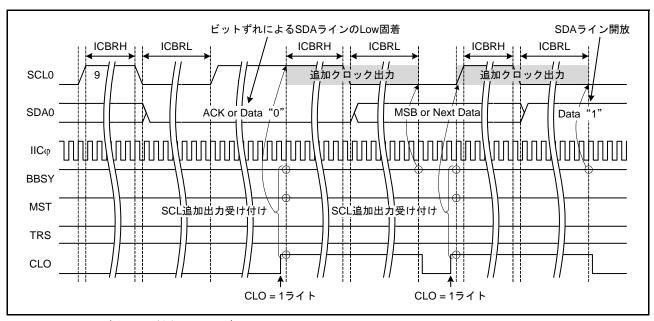

| 24    | 1.11.2 | SCL 追加出力機能                                  |     |

| 24    | 1.11.3 | RIIC リセット、内部リセット                            |     |

| 24.12 | SM     | Bus 動作                                      |     |

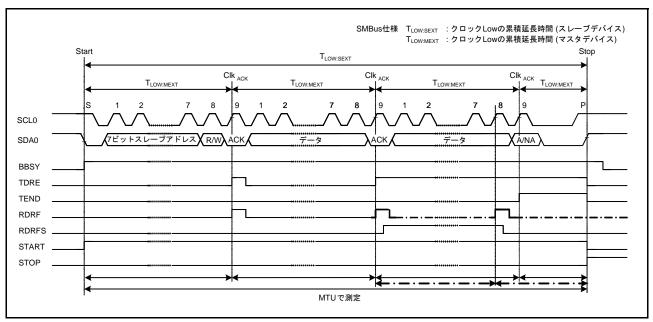

| 24    | 1.12.1 | SMBus タイムアウト測定                              |     |

| 24    | 1.12.2 | パケットエラーコード (PEC)                            |     |

|       | 1.12.3 | SMBus ホスト通知プロトコル (Notify ARP master コマンド)   |     |

| 24.13 | 割      | り込み要因                                       | 816 |

| 24.13.1     | TXI 割り込みおよび RXI 割り込みバッファ動作                                                                                                                              | 816 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 24.14 リセ    | アット時 / コンディション検出時のレジスタおよび機能の初期化                                                                                                                         | 817 |

| 24.15 使用    | 上の注意事項                                                                                                                                                  | 818 |

| 24.15.1     | モジュールストップ機能の設定                                                                                                                                          | 818 |

| 24.15.2     | 通信の開始に関する注意事項                                                                                                                                           | 818 |

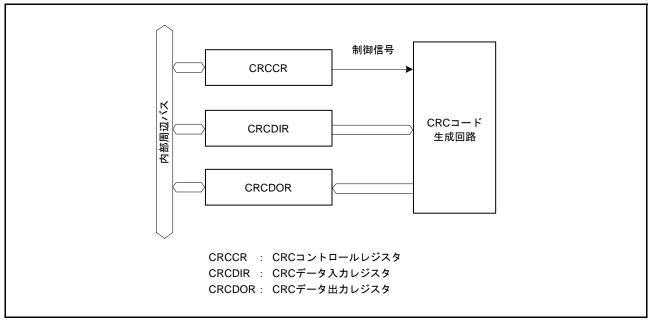

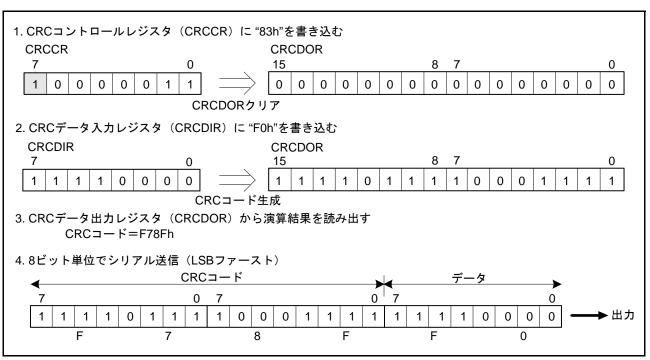

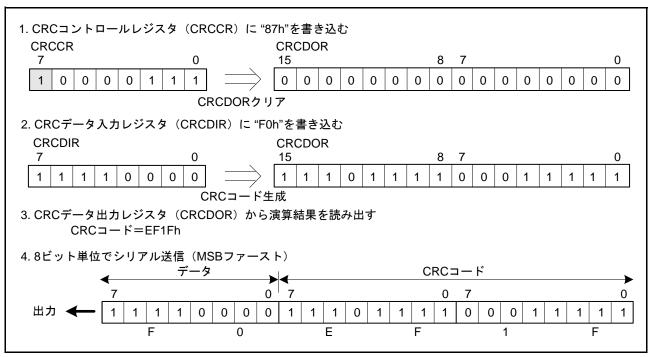

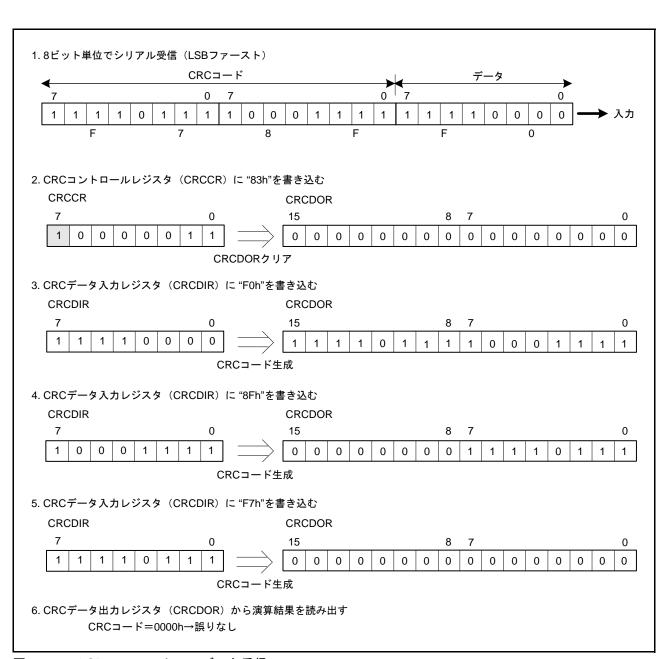

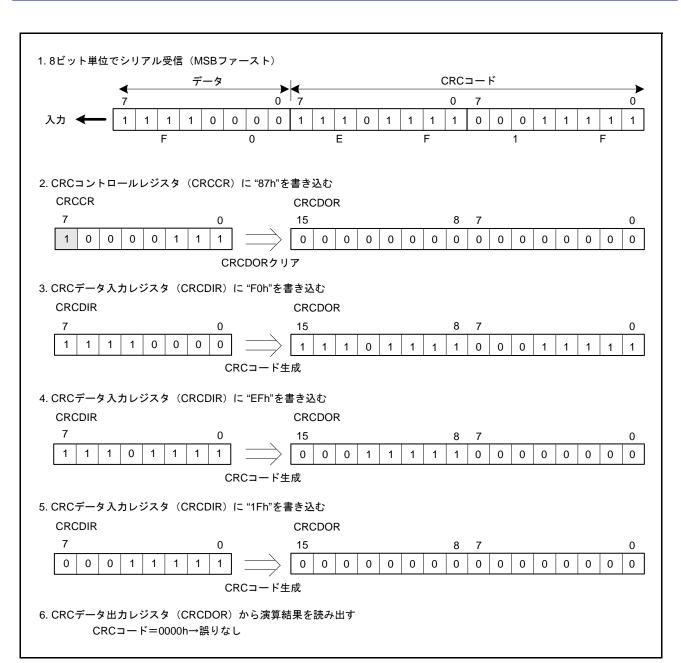

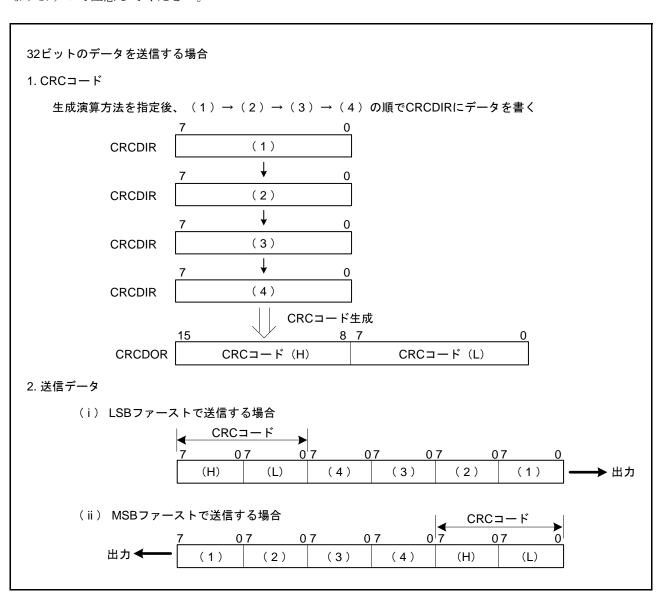

| 25. CRC 演算: | 器(CRC)                                                                                                                                                  | 819 |

| 25.1 概要     |                                                                                                                                                         | 819 |

| 25.2 レジ     | ジスタの説明                                                                                                                                                  | 820 |

| 25.2.1      | CRC コントロールレジスタ(CRCCR)                                                                                                                                   | 820 |

| 25.2.2      | CRC データ入力レジスタ(CRCDIR)                                                                                                                                   | 820 |

| 25.2.3      | CRC データ出力レジスタ(CRCDOR)                                                                                                                                   | 821 |

| 25.3 CRC    | こ演算器の動作説明                                                                                                                                               | 822 |

| 25.4 使用     | 上の注意事項                                                                                                                                                  | 825 |

| 25.4.1      | モジュールストップ機能の設定                                                                                                                                          | 825 |

| 25.4.2      | 転送時の注意事項                                                                                                                                                | 825 |

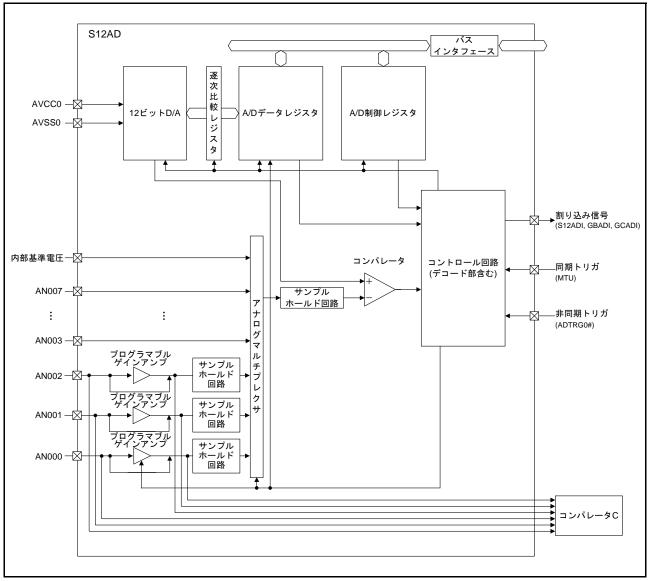

| 26. 12 ビット  | A/D コンバータ(S12ADF)                                                                                                                                       | 826 |

| 26.1 概要     |                                                                                                                                                         | 826 |

| 26.2 レジ     | ジスタの説明                                                                                                                                                  | 831 |

| 26.2.1      | A/D データレジスタ y(ADDRy)(y = 0 ~ 7)、<br>A/D データ二重化レジスタ(ADDBLDR)、<br>A/D データ二重化レジスタ A(ADDBLDRA)、<br>A/D データ二重化レジスタ B(ADDBLDRB)、<br>A/D 内部基準電圧データレジスタ(ADOCDR) | 831 |

| 26.2.2      | A/D 自己診断データレジスタ (ADRD)                                                                                                                                  | 833 |

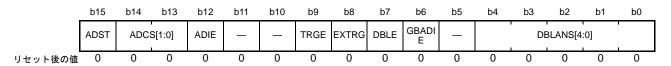

| 26.2.3      | A/D コントロールレジスタ (ADCSR)                                                                                                                                  | 834 |

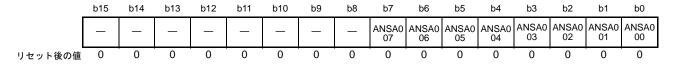

| 26.2.4      | A/D チャネル選択レジスタ A0 (ADANSA0)                                                                                                                             | 838 |

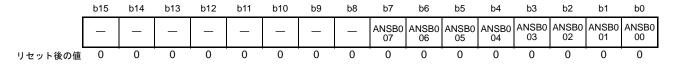

| 26.2.5      | A/D チャネル選択レジスタ B0(ADANSB0)                                                                                                                              | 839 |

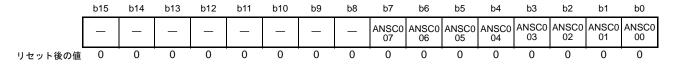

| 26.2.6      | A/D チャネル選択レジスタ C0(ADANSC0)                                                                                                                              | 840 |

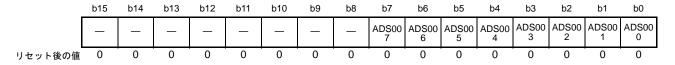

| 26.2.7      | A/D 変換値加算 / 平均機能チャネル選択レジスタ 0(ADADS0)                                                                                                                    | 841 |

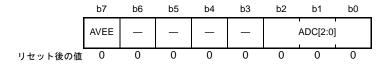

| 26.2.8      | A/D 変換値加算 / 平均回数選択レジスタ(ADADC)                                                                                                                           | 842 |

| 26.2.9      | A/D コントロール拡張レジスタ (ADCER)                                                                                                                                | 843 |

| 26.2.10     | A/D 変換開始トリガ選択レジスタ (ADSTRGR)                                                                                                                             | 845 |

| 26.2.11     | A/D 変換拡張入力コントロールレジスタ(ADEXICR)                                                                                                                           | 847 |

| 26.2.12     | A/D グループ C トリガ選択レジスタ(ADGCTRGR)                                                                                                                          | 848 |

| 26.2.13     | A/D サンプリングステートレジスタ n(ADSSTRn) (n = 0 $\sim$ 7, O)                                                                                                       | 850 |

| 26.2.14     | A/D サンプル & ホールド回路コントロールレジスタ (ADSHCR)                                                                                                                    | 851 |

| 26.2.15     | A/D 断線検出コントロールレジスタ(ADDISCR)                                                                                                                             | 852 |

| 26.2.16     | A/D グループスキャン優先コントロールレジスタ (ADGSPCR)                                                                                                                      | 853 |

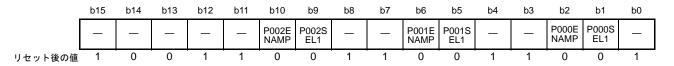

| 26.2.17     | A/D プログラマブルゲインアンプコントロールレジスタ (ADPGACR)                                                                                                                   | 855 |

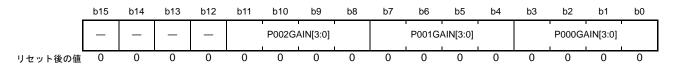

| 26.2.18     | A/D プログラマブルゲインアンプゲイン設定レジスタ 0 (ADPGAGS0)                                                                                                                 | 856 |

| 26.3 動作     | =説明                                                                                                                                                     | 857 |

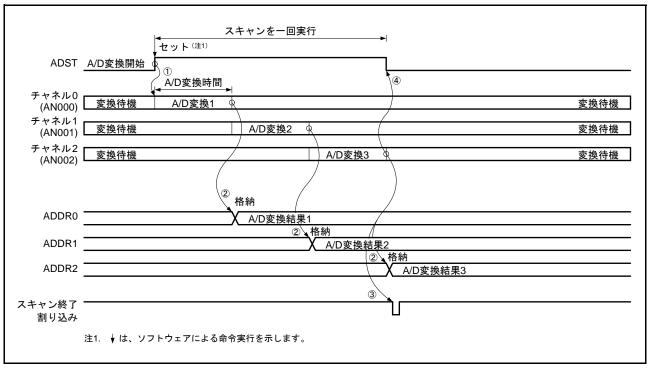

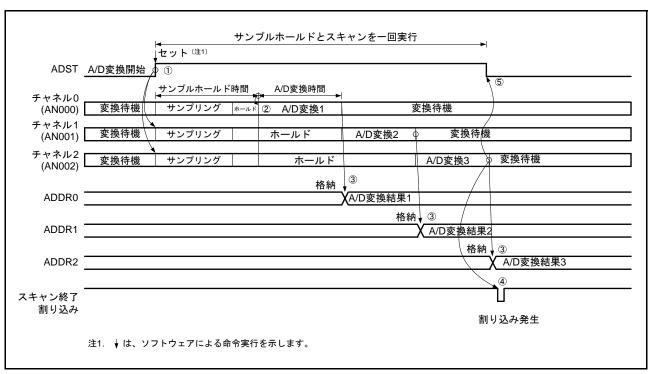

| 26.3.1  | スキャンの動作説明                            | 857 |

|---------|--------------------------------------|-----|

| 26.3.2  | シングルスキャンモード                          | 858 |

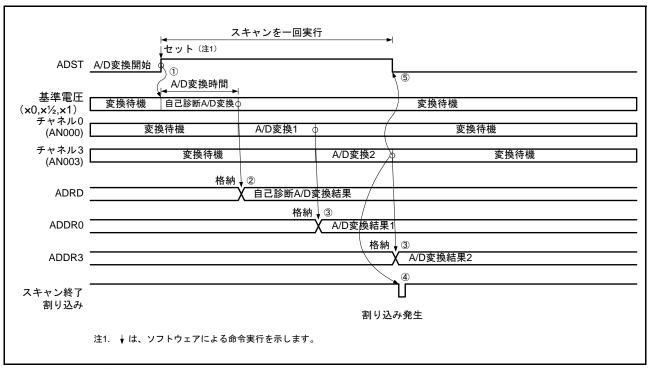

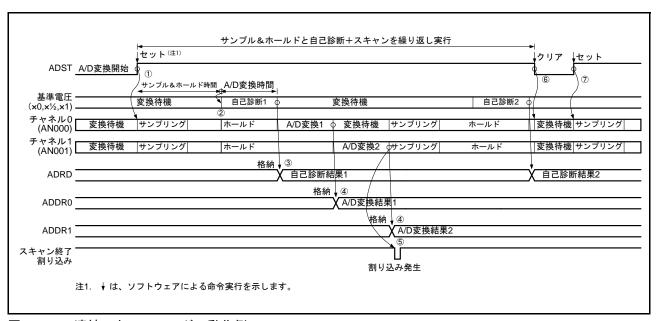

| 26.3.   | 2.1 基本動作 (チャネル専用サンプル & ホールドなし)       | 858 |

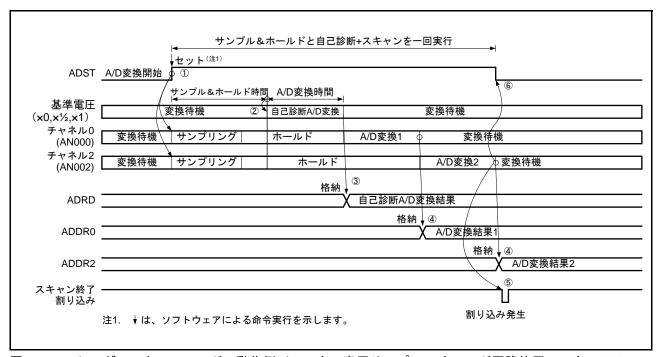

| 26.3.   | 2.2 基本動作(チャネル専用サンプル & ホールドあり)        | 859 |

| 26.3.2  | 2.3 チャネル選択と自己診断(チャネル専用サンプル & ホールドなし) | 860 |

| 26.3.2  | 2.4 チャネル選択と自己診断(チャネル専用サンプル & ホールドあり) | 861 |

| 26.3.2  | 2.5 内部基準電圧選択時の A/D 変換動作              | 862 |

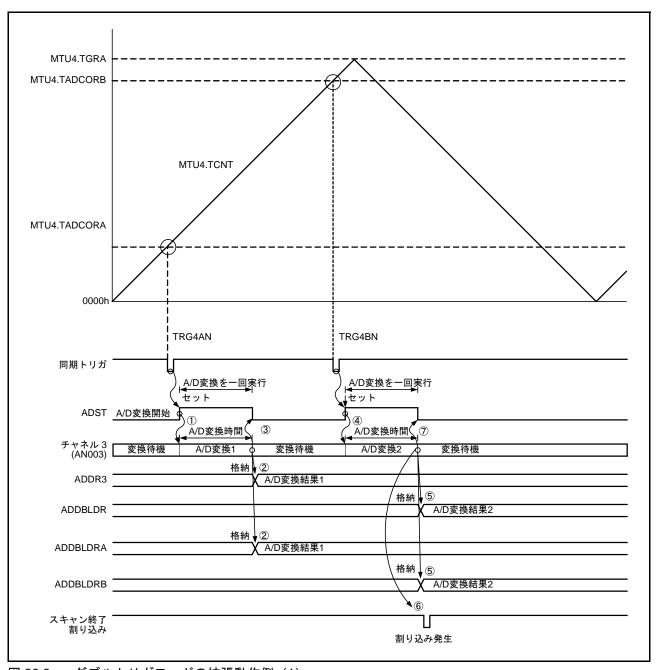

| 26.3.   | 2.6 ダブルトリガモード選択時の動作                  | 863 |

| 26.3.   | 2.7 ダブルトリガ拡張モードの動作                   | 864 |

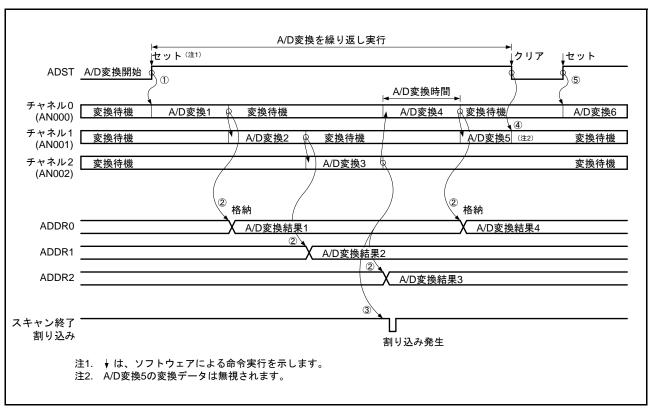

| 26.3.3  | 連続スキャンモード                            | 866 |

| 26.3.   | 3.1 基本動作 (チャネル専用サンプル & ホールドなし)       | 866 |

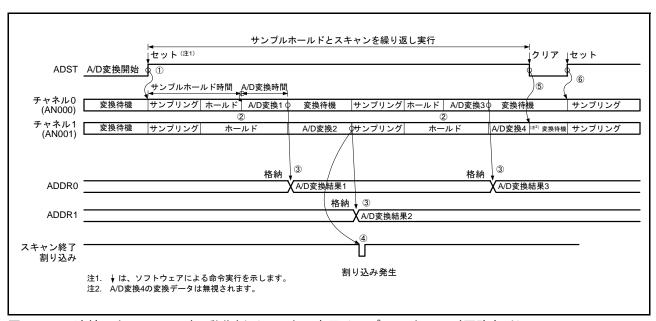

| 26.3.   | 3.2 基本動作 (チャネル専用サンプル & ホールドあり)       | 867 |

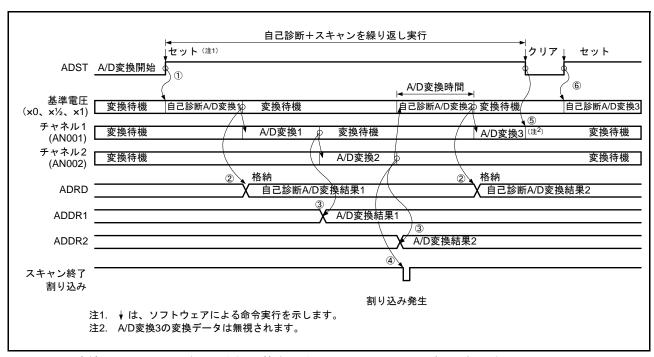

| 26.3.   | 3.3 チャネル選択と自己診断(チャネル専用サンプル & ホールドなし) | 868 |

| 26.3.   | 3.4 チャネル選択と自己診断(チャネル専用サンプル & ホールドあり) | 869 |

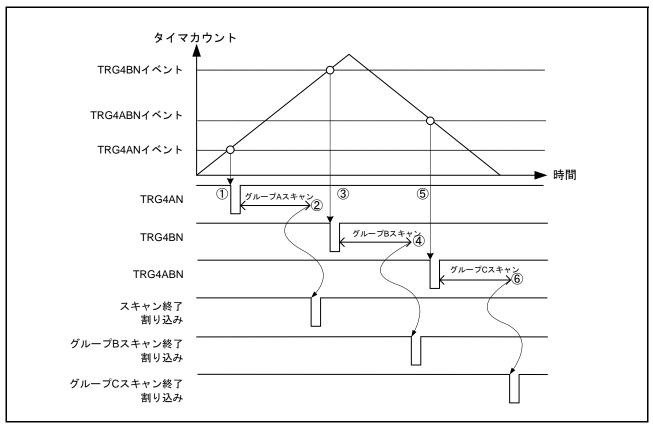

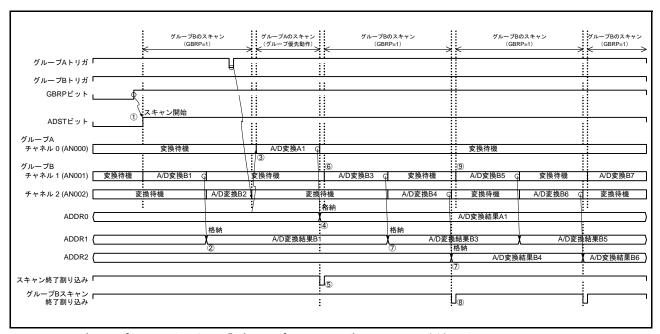

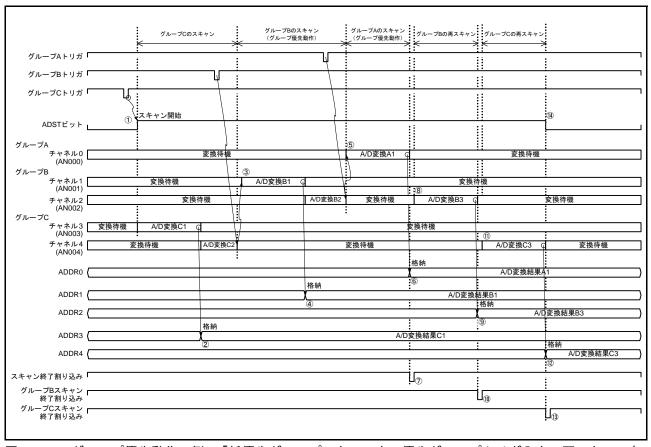

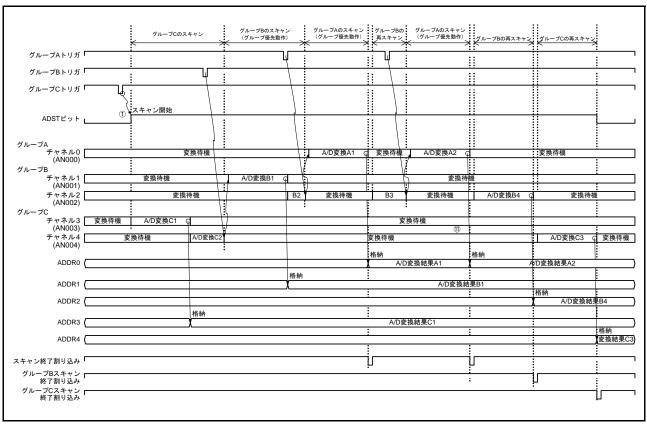

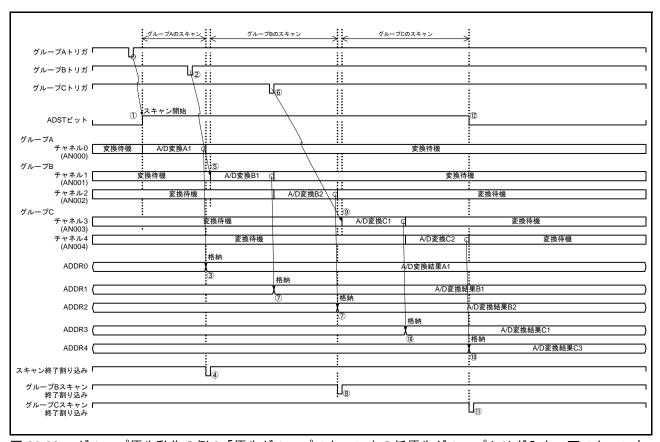

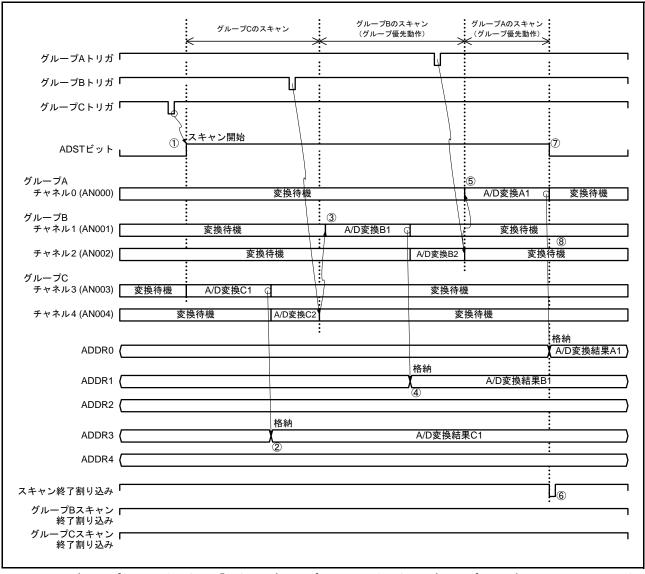

| 26.3.4  | グループスキャンモード                          | 870 |

| 26.3.4  | 4.1 基本動作                             | 870 |

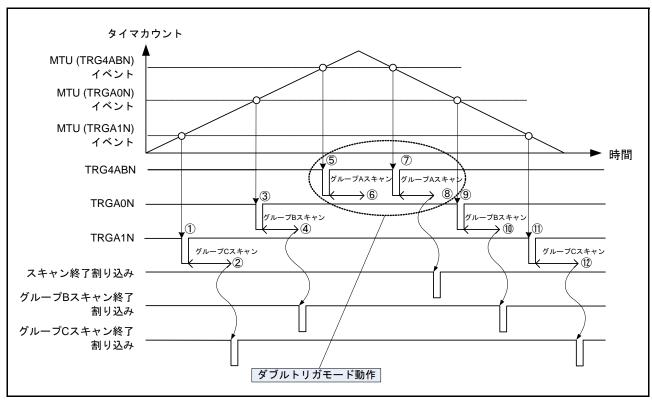

| 26.3.4  | 4.2 ダブルトリガモード選択時の動作                  | 871 |

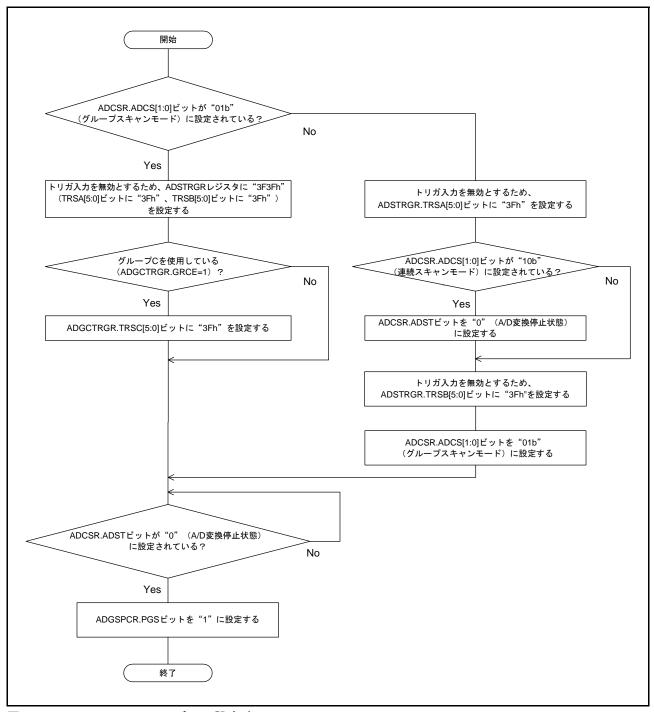

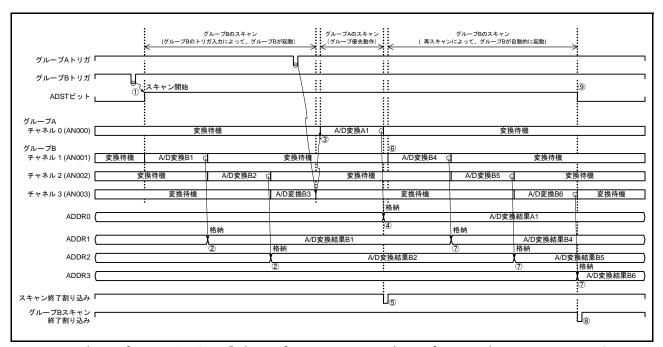

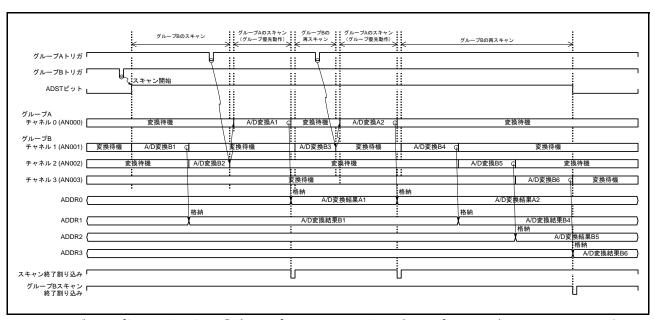

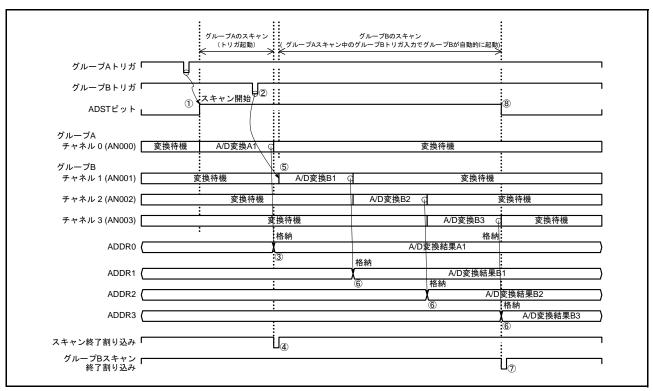

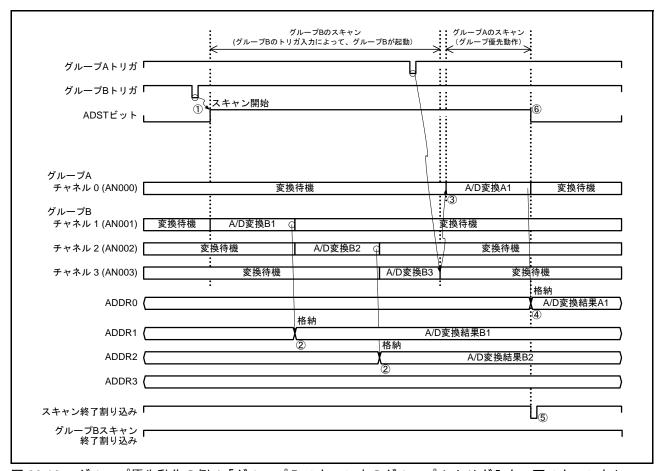

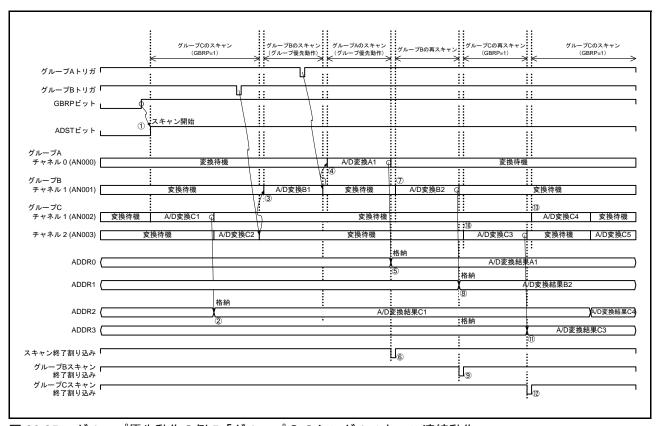

| 26.3.4  | 4.3 グループ優先制御動作                       | 873 |

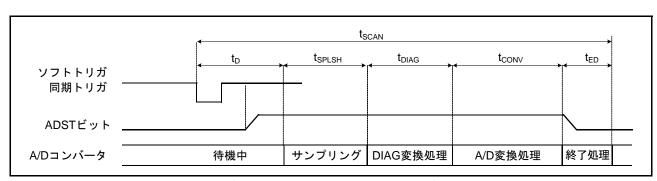

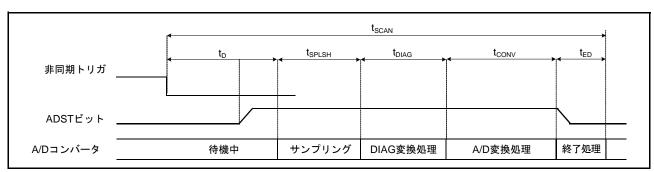

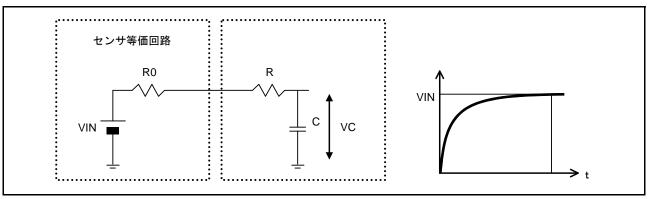

| 26.3.5  | アナログ入力のサンプリング時間とスキャン変換時間             | 891 |

| 26.3.6  | A/D データレジスタの自動クリア機能の使用例              | 893 |

| 26.3.7  | A/D 変換値加算 / 平均機能                     | 893 |

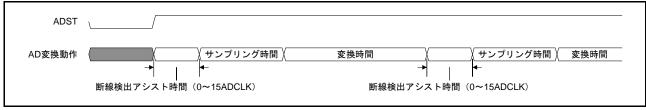

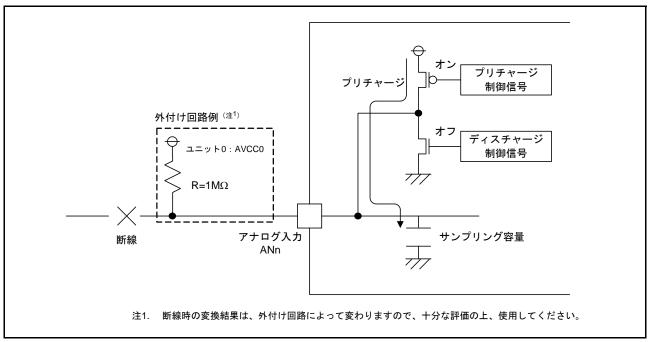

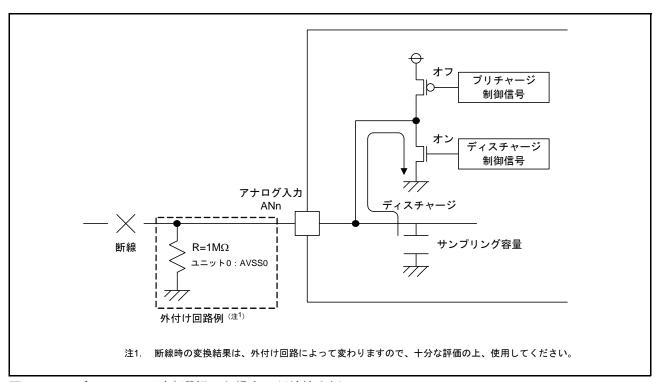

| 26.3.8  | 断線検出アシスト機能                           | 893 |

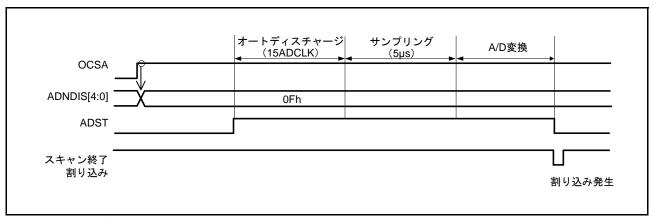

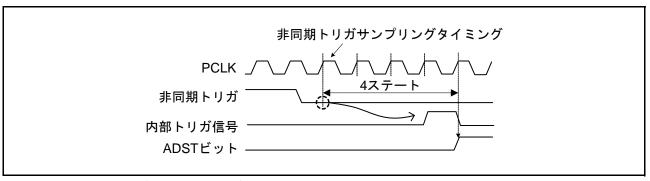

| 26.3.9  | 非同期トリガによる A/D 変換の開始                  | 895 |

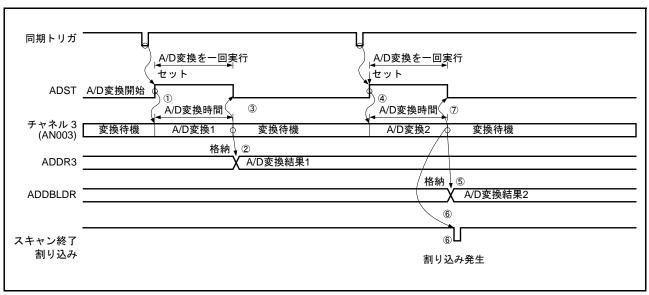

| 26.3.10 | 周辺モジュールからの同期トリガによる A/D 変換の開始         | 895 |

| 26.3.11 | プログラマブルゲインアンプ                        | 895 |

| 5.4 割   | り込み要因と DTC 転送要求                      | 896 |

| 26.4.1  | 割り込み要求                               | 896 |

| 5.5 許   | 容信号源インピーダンスについて                      | 897 |

| 5.6 使   | 用上の注意事項                              | 898 |

| 26.6.1  | データレジスタの読み出し注意事項                     | 898 |

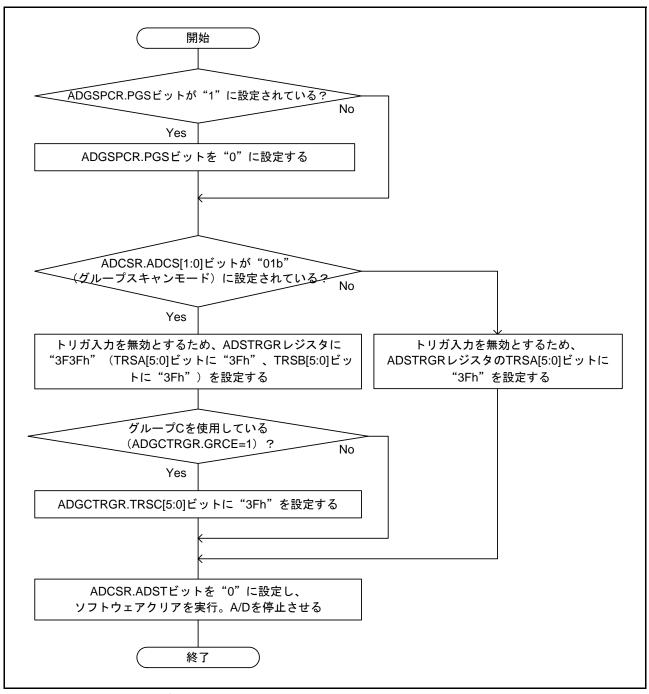

| 26.6.2  | A/D 変換停止時の注意事項                       | 898 |

| 26.6.3  | A/D 変換強制停止と開始時の動作タイミング               | 900 |

| 26.6.4  | スキャン終了割り込み処理の注意事項                    | 900 |

| 26.6.5  | モジュールストップ機能の設定                       | 900 |

| 26.6.6  | 低消費電力状態への遷移時の注意                      | 900 |

| 26.6.7  | ソフトウェアスタンバイモード解除時の注意                 | 900 |

| 26.6.8  | 断線検出アシスト機能使用時の絶対精度誤差                 | 900 |

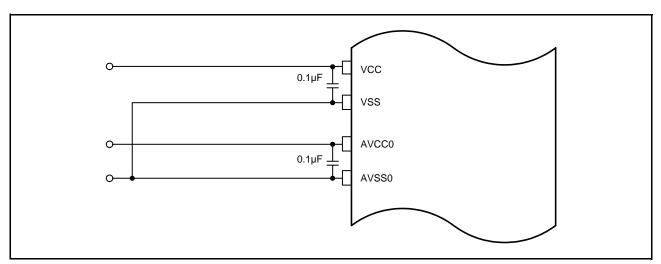

| 26.6.9  | アナログ電源端子他の設定範囲                       | 901 |

| 26.6.10 | ボード設計上の注意                            | 901 |

| 26.6.11 | ノイズ対策上の注意                            | 901 |

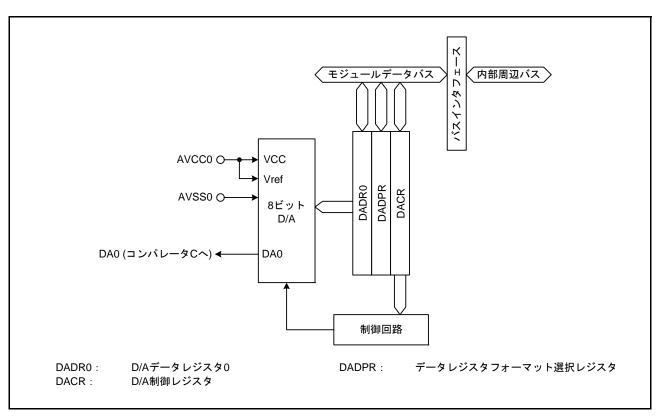

| 27. | コンパ    | レータ C 用リファレンス電圧生成専用 D/A コンバータ (DA)       | 903 |

|-----|--------|------------------------------------------|-----|

|     | 27.1   | 概要                                       | 903 |

|     | 27.2   | レジスタの説明                                  | 904 |

|     | 27.2.1 | D/A データレジスタ 0 (DADR0)                    | 904 |

|     | 27.2.2 | D/A 制御レジスタ (DACR)                        | 905 |

|     | 27.2.3 | データレジスタフォーマット選択レジスタ (DADPR)              | 905 |

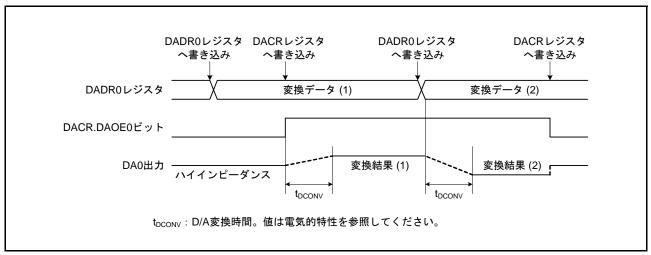

|     | 27.3   | 動作説明                                     | 906 |

|     | 27.4   | 使用上の注意事項                                 | 907 |

|     | 27.4.1 | モジュールストップ機能の設定                           | 907 |

|     | 27.4.2 | モジュールストップ時の D/A コンバータの動作                 | 907 |

|     | 27.4.3 | ソフトウェアスタンバイモード時の D/A コンバータの動作            | 907 |

|     | 27.4.4 | D/A コンバータの設定について                         | 907 |

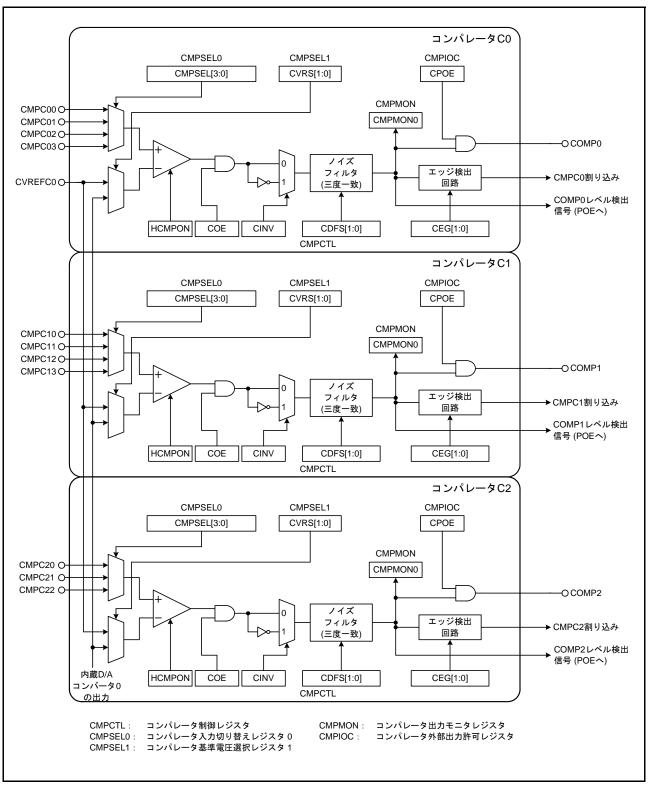

| 28. | コンパ    | レータ C (CMPC)                             | 908 |

|     | 28.1   | 概要                                       | 908 |

|     | 28.2   | レジスタの説明                                  | 911 |

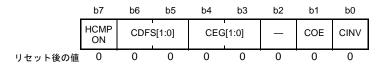

|     | 28.2.1 | コンパレータ制御レジスタ (CMPCTL)                    | 911 |

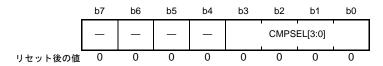

|     | 28.2.2 | コンパレータ入力切り替えレジスタ (CMPSEL0)               | 912 |

|     | 28.2.3 | コンパレータ基準電圧選択レジスタ (CMPSEL1)               | 913 |

|     | 28.2.4 | コンパレータ出力モニタレジスタ (CMPMON)                 | 914 |

|     | 28.2.5 | コンパレータ外部出力許可レジスタ (CMPIOC)                | 914 |

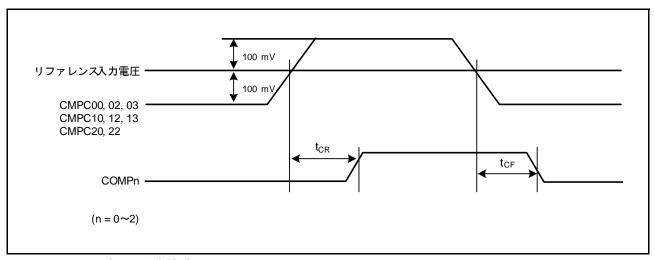

|     | 28.3   | 動作説明                                     | 915 |

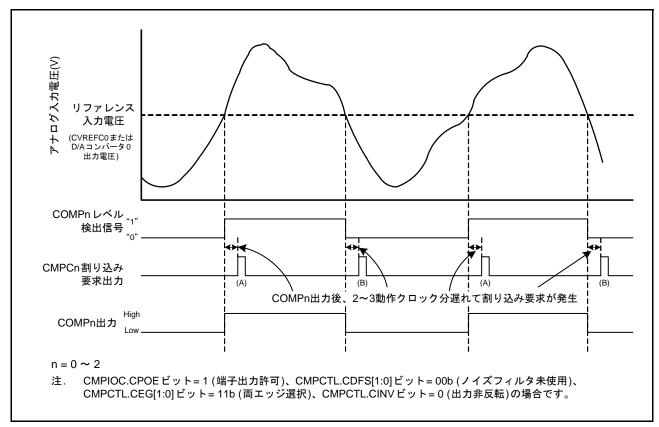

|     | 28.3.1 | コンパレータ動作例                                | 915 |

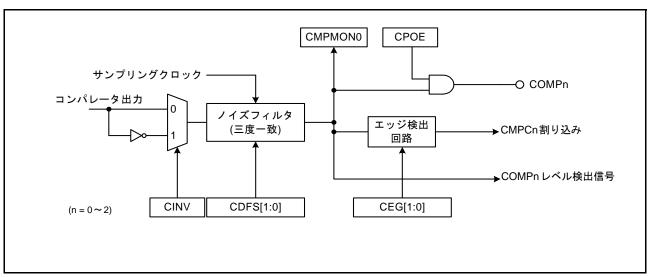

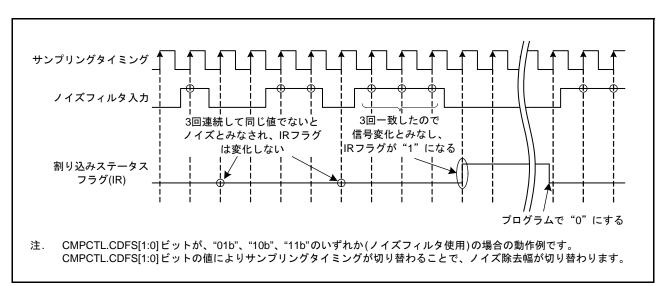

|     | 28.3.2 | ノイズフィルタ                                  | 916 |

|     | 28.3.3 | 割り込み                                     | 917 |

|     | 28.3.4 | コンパレータの端子出力                              | 917 |

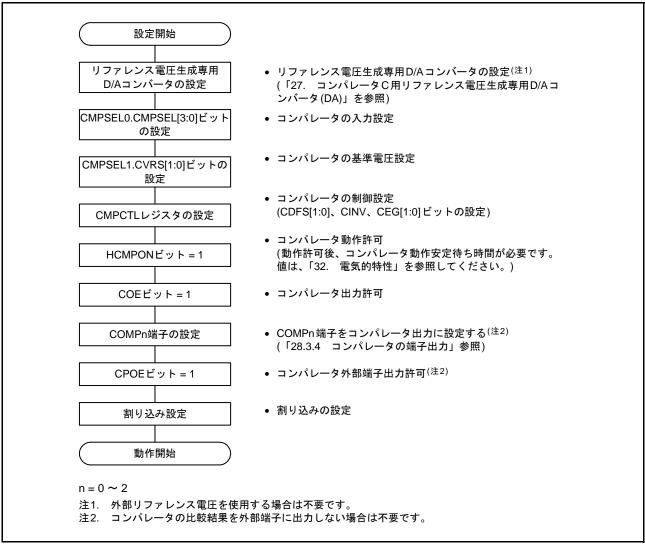

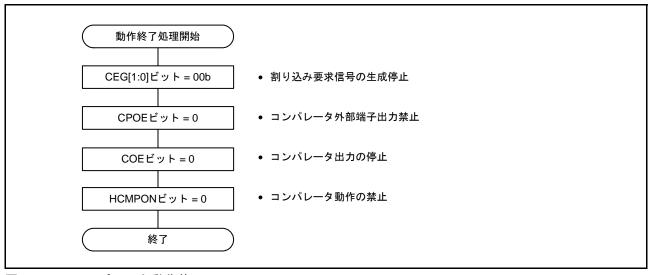

|     | 28.3.5 | コンパレータの設定手順                              | 918 |

|     | 28.4   | 使用上の注意事項                                 | 919 |

|     | 28.4.1 | モジュールストップ機能の設定                           | 919 |

|     | 28.4.2 | モジュールストップ時のコンパレータ C の動作                  | 919 |

|     | 28.4.3 | ソフトウェアスタンバイモード時のコンパレータ C の動作             | 919 |

|     | 28.4.4 | 12 ビット A/D コンバータがモジュールストップ中のコンパレータ C の動作 | 919 |

|     | 28.4.5 | リファレンス電圧生成に使用する D/A コンバータの設定について         | 920 |

| 29. | データ    | 演算回路 (DOC)                               | 921 |

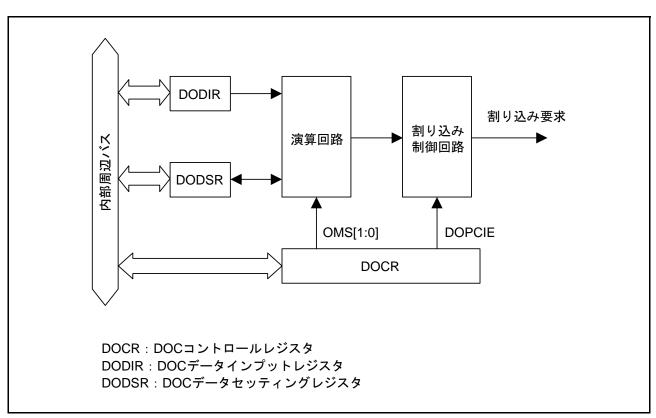

|     |        | 概要                                       |     |

|     | 29.2   | レジスタの説明                                  | 922 |

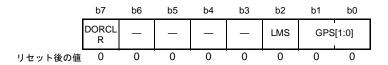

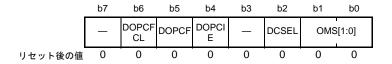

|     | 29.2.1 | DOC コントロールレジスタ (DOCR)                    | 922 |

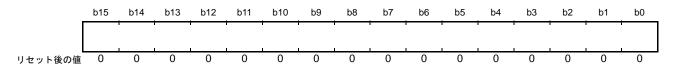

|     | 29.2.2 | DOC データインプットレジスタ (DODIR)                 |     |

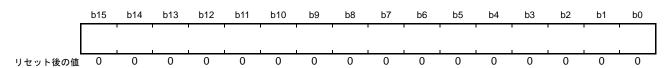

|     | 29.2.3 | DOC データセッティングレジスタ (DODSR)                |     |

|     |        | 動作説明                                     |     |

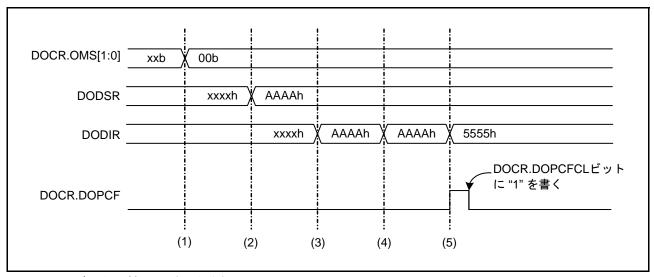

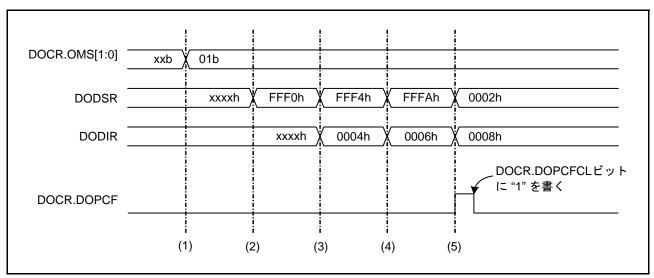

|     | 29.3.1 | データ比較モード                                 |     |

|     |        |                                          | '   |

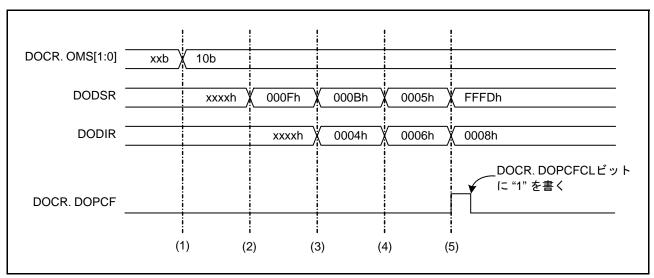

|     | 29.3.2  | データ加算モード                                 | 925 |

|-----|---------|------------------------------------------|-----|

|     | 29.3.3  | データ減算モード                                 | 926 |

|     | 29.4 割  | り込み要求                                    | 926 |

|     | 29.5 使  | 用上の注意事項                                  | 926 |

|     | 29.5.1  | モジュールストップ機能の設定                           | 926 |

| 30. | RAM     |                                          | 927 |

|     | 30.1 概  | 要                                        | 927 |

|     | 30.2 動  | 作説明                                      | 927 |

|     | 30.2.1  | 消費電力低減機能                                 | 927 |

| 31. | フラッシ    | ュメモリ (FLASH)                             | 928 |

|     | 31.1 概  | 要                                        | 928 |

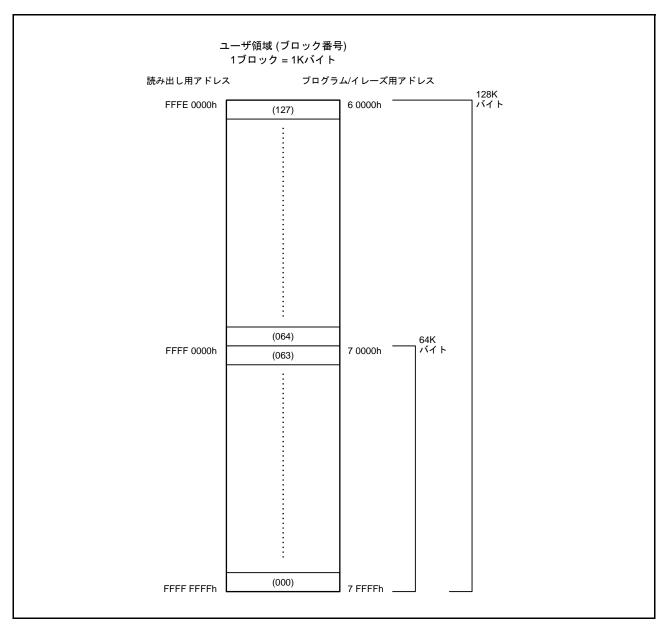

|     | 31.2 RC | DM の領域とブロックの構成                           | 929 |

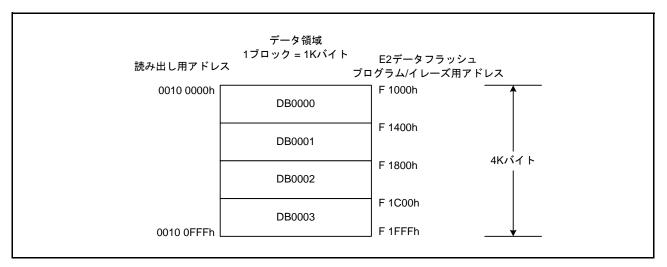

|     | 31.3 E2 | データフラッシュの領域とブロックの構成                      | 930 |

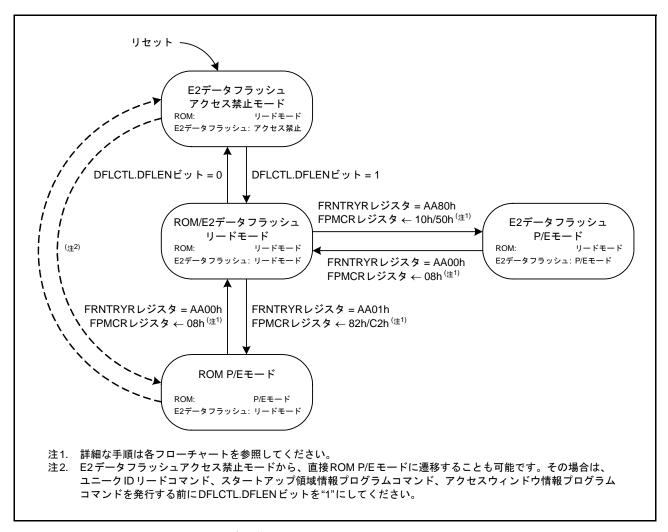

|     | 31.4 V  | ジスタの説明                                   | 931 |

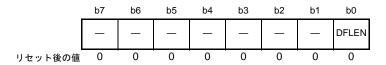

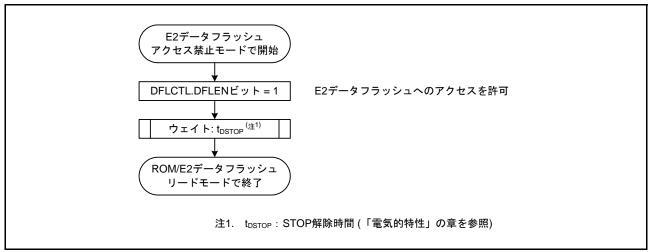

|     | 31.4.1  | E2 データフラッシュ制御レジスタ (DFLCTL)               | 931 |

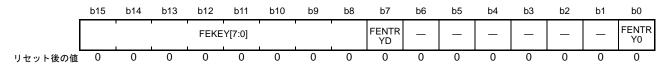

|     | 31.4.2  | フラッシュ P/E モードエントリレジスタ (FENTRYR)          | 932 |

|     | 31.4.3  | プロテクト解除レジスタ (FPR)                        | 933 |

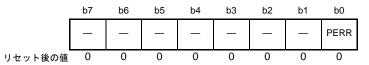

|     | 31.4.4  | プロテクト解除ステータスレジスタ (FPSR)                  | 933 |

|     | 31.4.5  | フラッシュ P/E モード制御レジスタ (FPMCR)              | 934 |

|     | 31.4.6  | フラッシュ初期設定レジスタ (FISR)                     | 935 |

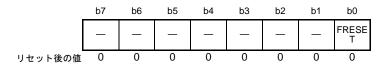

|     | 31.4.7  | フラッシュリセットレジスタ (FRESETR)                  | 937 |

|     | 31.4.8  | フラッシュ領域選択レジスタ (FASR)                     | 937 |

|     | 31.4.9  | フラッシュ制御レジスタ (FCR)                        | 938 |

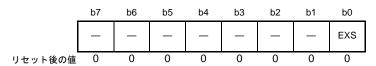

|     | 31.4.10 | フラッシュエクストラ領域制御レジスタ (FEXCR)               | 940 |

|     | 31.4.11 | フラッシュ処理開始アドレスレジスタ H (FSARH)              | 941 |

|     | 31.4.12 | フラッシュ処理開始アドレスレジスタ L (FSARL)              | 941 |

|     | 31.4.13 | フラッシュ処理終了アドレスレジスタ H (FEARH)              | 942 |

|     | 31.4.14 | フラッシュ処理終了アドレスレジスタ L (FEARL)              | 942 |

|     | 31.4.15 | フラッシュリードバッファレジスタ H (FRBH)                | 943 |

|     | 31.4.16 | フラッシュリードバッファレジスタ L (FRBL)                | 943 |

|     | 31.4.17 | フラッシュライトバッファレジスタ H (FWBH)                | 943 |

|     | 31.4.18 | フラッシュライトバッファレジスタ L (FWBL)                | 944 |

|     | 31.4.19 | フラッシュステータスレジスタ 0 (FSTATR0)               |     |

|     | 31.4.20 | フラッシュステータスレジスタ 1 (FSTATR1)               | 947 |

|     | 31.4.21 | フラッシュエラーアドレスモニタレジスタ H (FEAMH)            | 948 |

|     | 31.4.22 | フラッシュエラーアドレスモニタレジスタ L (FEAML)            |     |

|     | 31.4.23 | フラッシュスタートアップ設定モニタレジスタ (FSCMR)            |     |

|     | 31.4.24 | フラッシュアクセスウィンドウ開始アドレスモニタレジスタ (FAWSMR)     |     |

|     | 31.4.25 | フラッシュアクセスウィンドウ終了アドレスモニタレジスタ (FAWEMR)     |     |

|     | 31.4.26 | ユニーク ID レジスタ n (UIDRn) (n = 0 $\sim$ 31) | 950 |

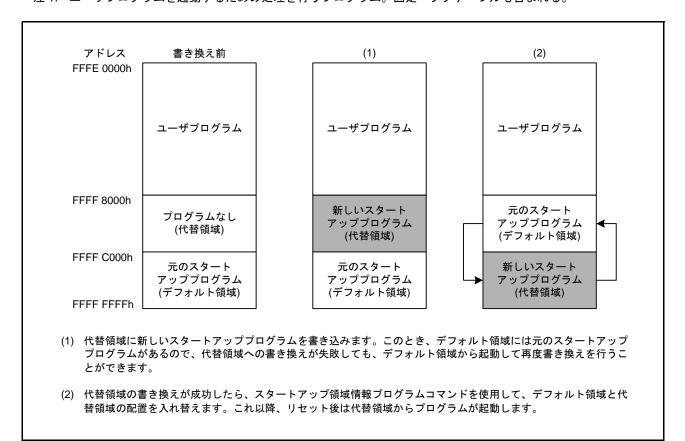

| 31.5  | スタ      | ート   | アッププログラム保護機能                      | 951 |

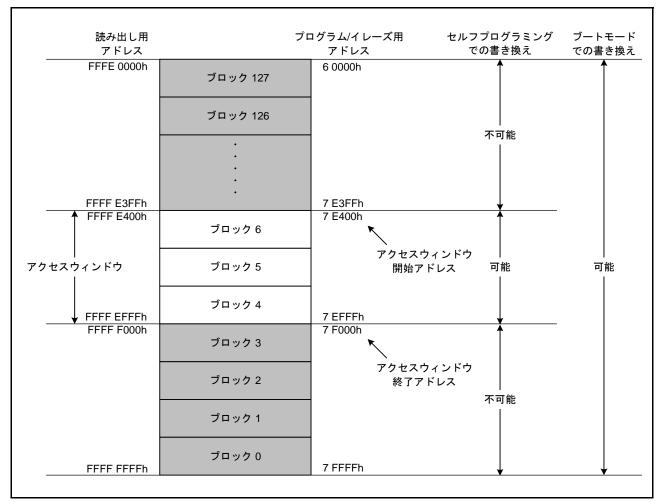

|-------|---------|------|-----------------------------------|-----|

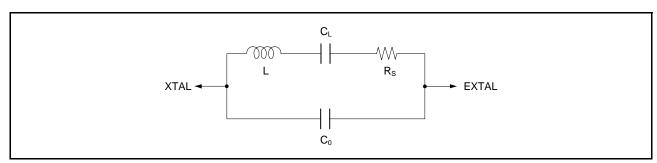

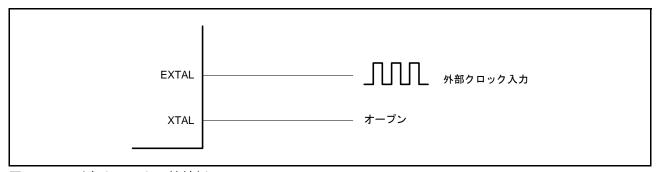

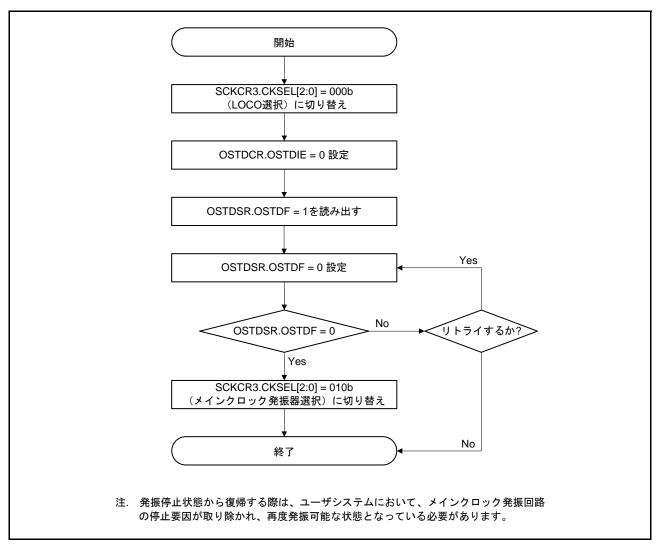

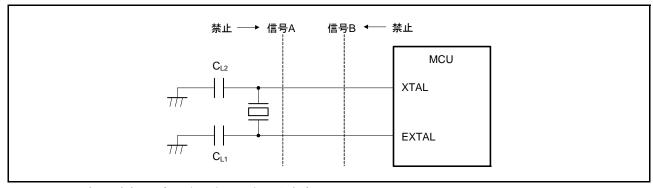

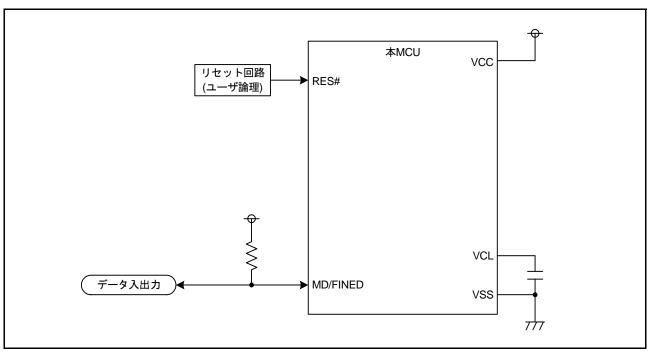

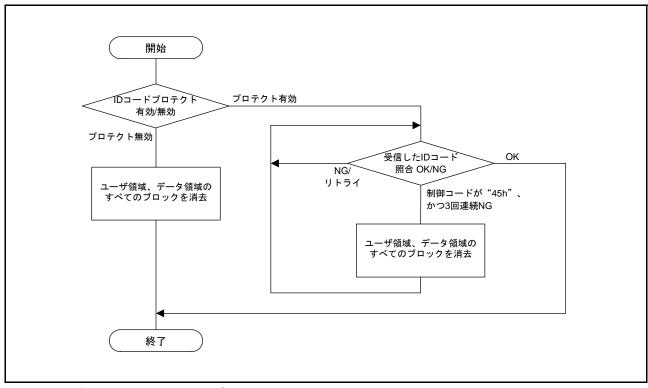

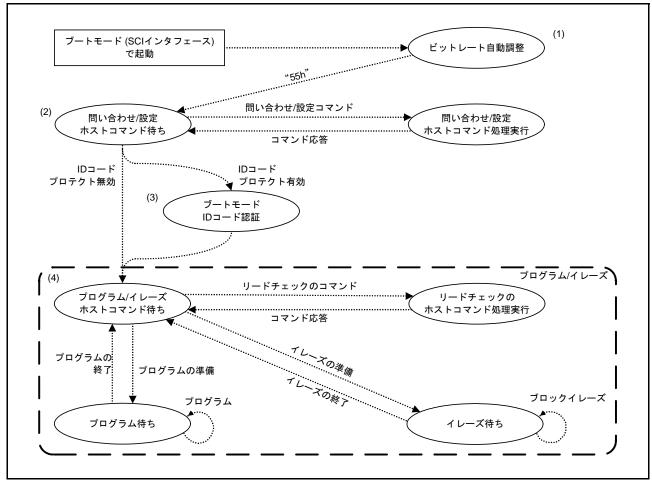

| 31.6  | エリ      | アプ   | ロテクション                            | 952 |