Package Information

| CAD Model: | View CAD Model |

| Pkg. Type: | SOIC |

| Pkg. Code: | PSG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 12.8 x 7.6 x 2.34 |

| Pitch (mm): | 1.27 |

Environmental & Export Classifications

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 1 |

Product Attributes

| Pkg. Type | SOIC |

| Lead Count (#) | 20 |

| Pb (Lead) Free | Yes |

| Carrier Type | Reel |

| App Jitter Compliance | TR62411, ETS300011, GR-1244 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.008 - 0.008, 10 - 50 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 12.8 |

| MOQ | 1000 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 0.008 - 44.736 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 3 |

| Package Area (mm²) | 97.3 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 12.8 x 7.6 x 2.34 |

| Prog. Clock | No |

| Published | No |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 1000 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 2.34 |

| Width (mm) | 7.6 |

Resources for MK2049-36

Description

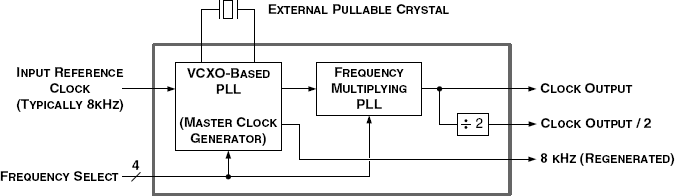

The MK2049-36 is a Phased Locked Loop (PLL) based clock synthesizer that accepts multiple input frequencies. With an 8 kHz clock input as a reference, the MK2049-36 generates T1, E1, T3, E3, OC3 and other communications frequencies. This allows for the generation of clocks frequency-locked to an 8 kHz backplane clock, simplifying clock synchronization in communications systems. This part also has a jitter-attenuated Buffer capability. In this mode, the MK2049-36 is ideal for filtering jitter from clocks with high jitter. IDT can customize these devices for many other different frequencies. Contact your IDT representative for more details.