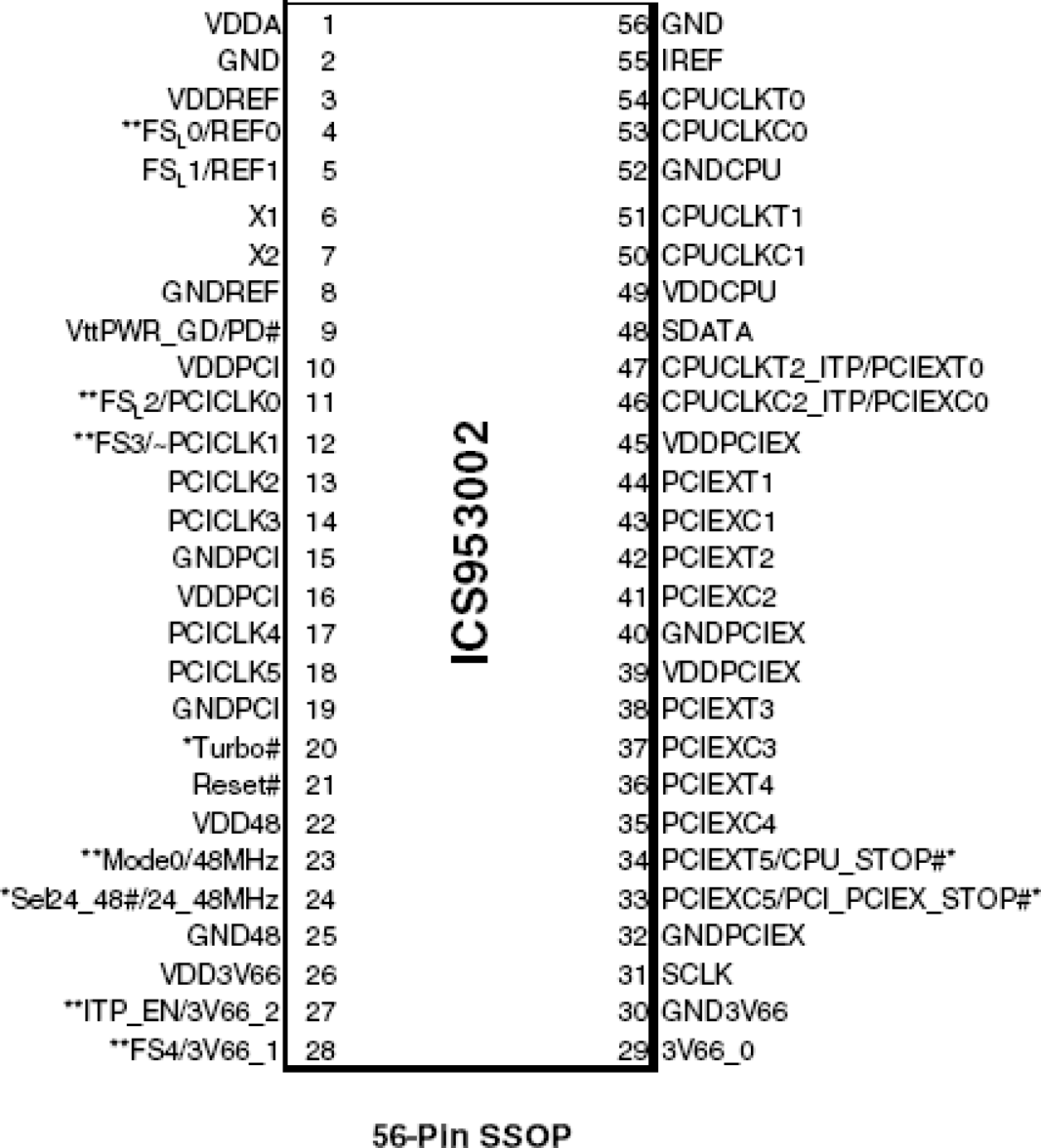

Package Information

| CAD Model: | View CAD Model |

| Pkg. Type: | SSOP |

| Pkg. Code: | PVG56 |

| Lead Count (#): | 56 |

| Pkg. Dimensions (mm): | 18.4 x 7.5 x 2.3 |

| Pitch (mm): | 0.64 |

Environmental & Export Classifications

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 1 |

| ECCN (US) | |

| HTS (US) |

Product Attributes

| Pkg. Type | SSOP |

| Lead Count (#) | 56 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| App Jitter Compliance | PCIe |

| C-C Jitter Max P-P (ps) | 85 |

| Chipset Manufacturer | VIA |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Function | Clock Generator |

| Input Freq (MHz) | 14.318 - 14.318 |

| Input Type | Crystal |

| Inputs (#) | 1 |

| Length (mm) | 18.4 |

| MOQ | 130 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 8 |

| Output Freq Range (MHz) | 14.318 - 400 |

| Output Skew (ps) | 100 |

| Output Voltage (V) | 3.3 |

| Package Area (mm²) | 138 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.64 |

| Pkg. Dimensions (mm) | 18.4 x 7.5 x 2.3 |

| Prog. Clock | Yes |

| Prog. Interface | SMBus, I2C |

| Qty. per Carrier (#) | 26 |

| Qty. per Reel (#) | 0 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 2.3 |

| Width (mm) | 7.5 |

Resources for 953002

Description

953002 is a 56-pin clock chip for P4 type processors with PCI-Express. The 953002 is part of a whole new line of ICS clock generators and buffers called TCH™ (Timing Control Hub). This part incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a serially programmable I2C interface, this device can adjust the output clocks by configuring the frequency setting, the output divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each individual output clock. M/N control can configure output frequency with resolution up to 0.1MHz increment.