Package Information

| CAD Model: | View CAD Model |

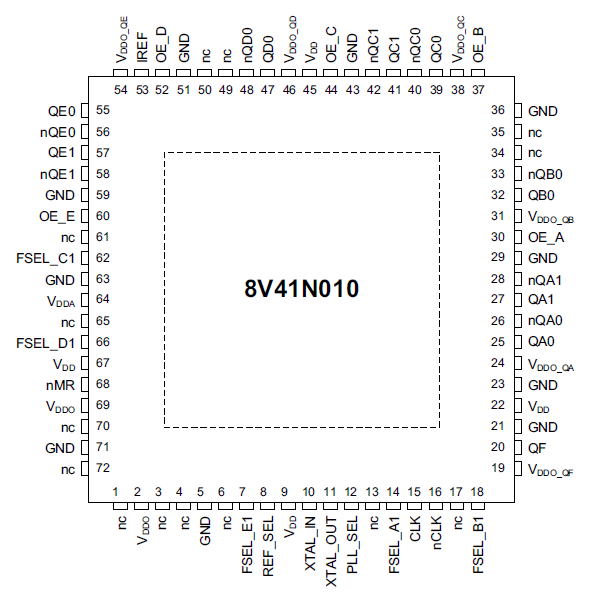

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG72 |

| Lead Count (#): | 72 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.0 |

| Pitch (mm): | 0.5 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

Product Attributes

| Lead Count (#) | 72 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

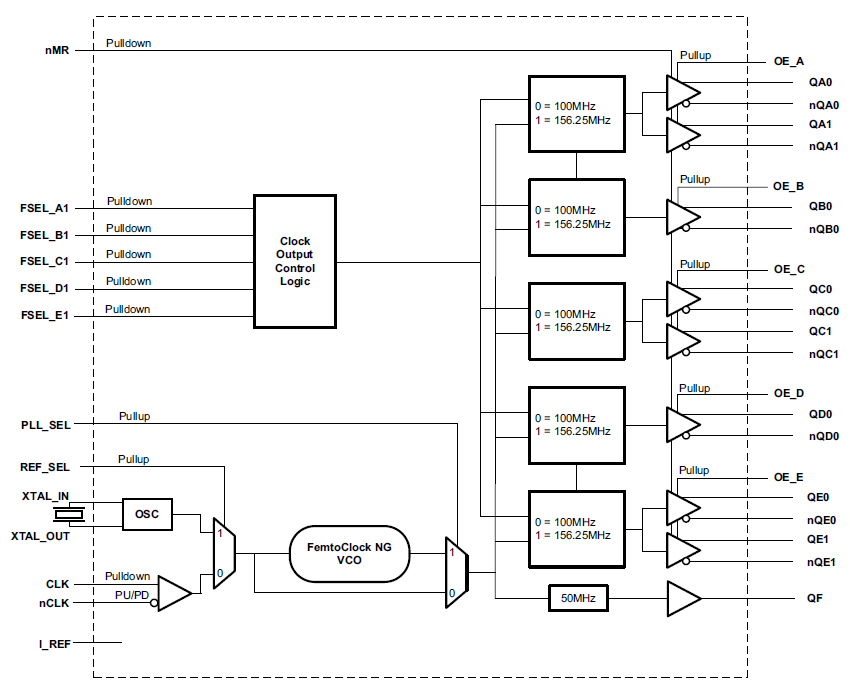

| Advanced Features | 50M output(s), 100M output(s), 156.25M output(s) |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, XAUI, RXAUI |

| Chipset Manufacturer | Cavium |

| Clock Spec. | Cavium: Period Jitter < 25 ps |

| Core Voltage (V) | 3.3V |

| Feedback Input | No |

| Function | Generator |

| Input Freq (MHz) | 25 - 25 |

| Input Type | Crystal, LVCMOS, LVDS, LVPECL, LVHSTL, HCSL |

| Inputs (#) | 2 |

| Length (mm) | 10 |

| MOQ | 2500 |

| Output Banks (#) | 6 |

| Output Freq Range (MHz) | 50 - 50, 100 - 100, 156.25 - 156.25 |

| Output Type | LVCMOS, HCSL |

| Output Voltage (V) | 3.3V |

| Outputs (#) | 9 |

| Package Area (mm²) | 100 |

| Phase Jitter Max RMS (ps) | 0.45 |

| Phase Jitter Typ RMS (ps) | 0.32 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Prog. Clock | No |

| Published | No |

| Reel Size (in) | 13 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 10 |

Resources for 8V41N010I

Description

The 8V41N010 is a PLL-based clock generator specifically designed for Cavium Networks Octeon II processors. This high-performance device is optimized to generate the processor core reference clock, the PCI-Express, sRIO, XAUI, SerDes reference clocks, and the clocks for both the Gigabit Ethernet MAC and PHY. The output frequencies are generated from a 25MHz external input source or an external 25MHz parallel resonant crystal. The industrial temperature range of the 8V41N010 supports telecommunication, networking, and storage requirements.