Package Information

| CAD Model: | View CAD Model |

| Pkg. Type: | CABGA |

| Pkg. Code: | AJG144 |

| Lead Count (#): | 144 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.2 |

| Pitch (mm): | 0.8 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

Product Attributes

| Lead Count (#) | 144 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Function | Port Synchronizer |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 168 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e1 SnAgCu |

| Temp. Range (°C) | -40 to 85°C |

| Application | PTP Line Card, low-cTE line card |

| Channels (#) | 8 |

| Core Voltage (V) | 2.5V, 3.3V |

| Diff. Inputs | 8 |

| Diff. Outputs | 12 |

| Family Name | ClockMatrix |

| Fractional Output Dividers (#) | 8 |

| Input Freq (MHz) | 0.001 - 1000 |

| Input Type | HCSL, LVDS, LVHSTL, LVPECL, SSTL |

| Inputs (#) | 16 |

| Length (mm) | 10 |

| Loop Bandwidth Range (Hz) | 17 - 12000 |

| MOQ | 168 |

| Output Banks (#) | 8 |

| Output Freq Range (MHz) | 5.0E-7 - 1000 |

| Output Skew (ps) | 50 |

| Output Type | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL |

| Output Voltage (V) | 1.2V, 1.5V, 1.8V, 2.5V, 3.3V |

| Outputs (#) | 24 |

| Phase Jitter Max RMS (ps) | 0.2 |

| Phase Jitter Typ RMS (ps) | 0.15 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.2 |

| Pkg. Type | CABGA |

| Product Category | IEEE 1588 |

| Prog. Interface | I2C, SPI |

| Published | No |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 1.2 |

| Width (mm) | 10 |

| Xtal Freq (KHz) | 25 - 54 |

Resources for 8A34011

Description

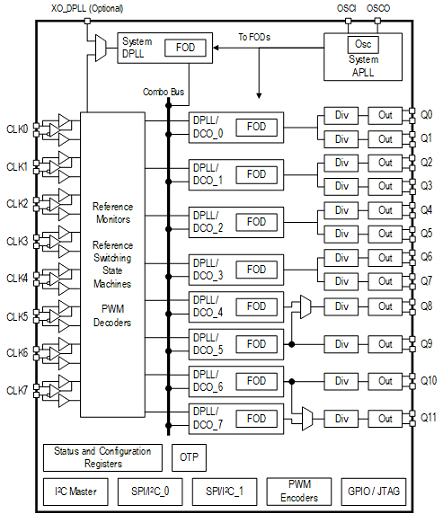

The 8A34011 line card synchronizer for IEEE 1588 regenerates and distributes ultra-low jitter; precision timing signals that are locked to IEEE 1588 and Synchronous Ethernet (SyncE) reference sources elsewhere in a system. The device can be used to precisely synchronize IEEE 1588 Time Stamp Units (TSUs) and SyncE ports on line cards or daughter cards that are connected with synchronization sources across backplanes or other media that introduce clock propagation delays. Digital PLLs (DPLLs) support hitless reference switching between references from redundant timing sources. The device can be used to actively measure and compensate for clock propagation delays across backplanes and across circuit boards to ensure the distribution of accurate time and phase with minimal time error between IEEE 1588 TSUs in a system. The device supports multiple independent timing channels for IEEE 1588 clock synthesis, SyncE clock generation, jitter attenuation, and universal frequency translation. Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs ultra-low jitter clocks that can directly synchronize SerDes running at up to 28Gbps; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces and IEEE 1588 TSUs.

To see other devices in this product family, visit the ClockMatrix™ Timing Solutions page.