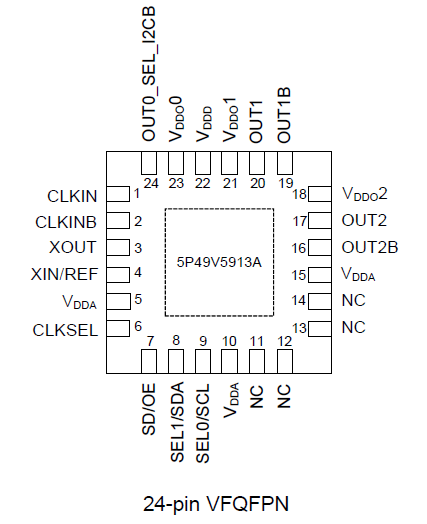

Package Information

| CAD Model: | View CAD Model |

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG24 |

| Lead Count (#): | 24 |

| Pkg. Dimensions (mm): | 4.0 x 4.0 x 0.9 |

| Pitch (mm): | 0.5 |

Environmental & Export Classifications

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

Product Attributes

| Lead Count (#) | 24 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 490 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Additive Phase Jitter Typ P-P (fs) | 0.7 |

| Advanced Features | Programmable Clock, Reference Output, Spread Spectrum |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3 |

| C-C Jitter Typ P-P (ps) | 46 |

| Core Voltage (V) | 1.8V, 2.5V, 3.3V |

| Family Name | VersaClock 5 |

| Input Freq (MHz) | 1 - 350 |

| Input Type | Crystal, LVCMOS, LVPECL, LVDS, HCSL |

| Inputs (#) | 2 |

| Length (mm) | 4 |

| MOQ | 490 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 1 - 350 |

| Output Skew (ps) | 75 |

| Output Type | LVCMOS, LVPECL, HCSL, LVDS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Outputs (#) | 3 |

| Package Area (mm²) | 16 |

| Phase Jitter Max RMS (fs) | 1500 |

| Phase Jitter Max RMS (ps) | 1.5 |

| Phase Jitter Typ RMS (fs) | 700 |

| Phase Jitter Typ RMS (ps) | 0.7 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 4.0 x 4.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Prog. Clock | Yes |

| Prog. Interface | I2C, OTP |

| Published | No |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 4 |

Resources for 5P49V5913

Description

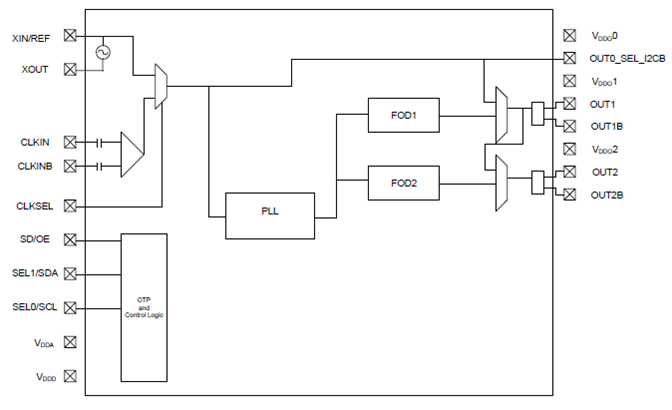

The 5P49V5913 is low-power programmable clock generator with best-in-class jitter performance and design flexibility with universal outputs capable of generating any output frequency. The 5P49V5913 is intended for high performance consumer, networking, industrial, computing, and data-communications applications. Configurations may be stored in on-chip One-Time Programmable (OTP) memory or changed using I2C interface. This is Renesas' fifth generation of programmable clock technology (VersaClock® 5). The frequencies are generated from a single reference clock or crystal input. A glitchless manual switchover function allows one of the redundant clock inputs to be selected during normal operation.

Two select pins allow up to 4 different configurations to be programmed and accessible using processor GPIOs or bootstrapping. The different selections may be used for different operating modes (full function, partial function, partial power-down), regional standards (US, Japan, Europe) or system production margin testing. The device may be configured to use one of two I2C addresses to allow multiple devices to be used in a system.